Изобретение относится к вычислительной технике и может быть использовано в системах обработки и передачи цифровой информации.

Цепь изобретения - повышение быстродействия.

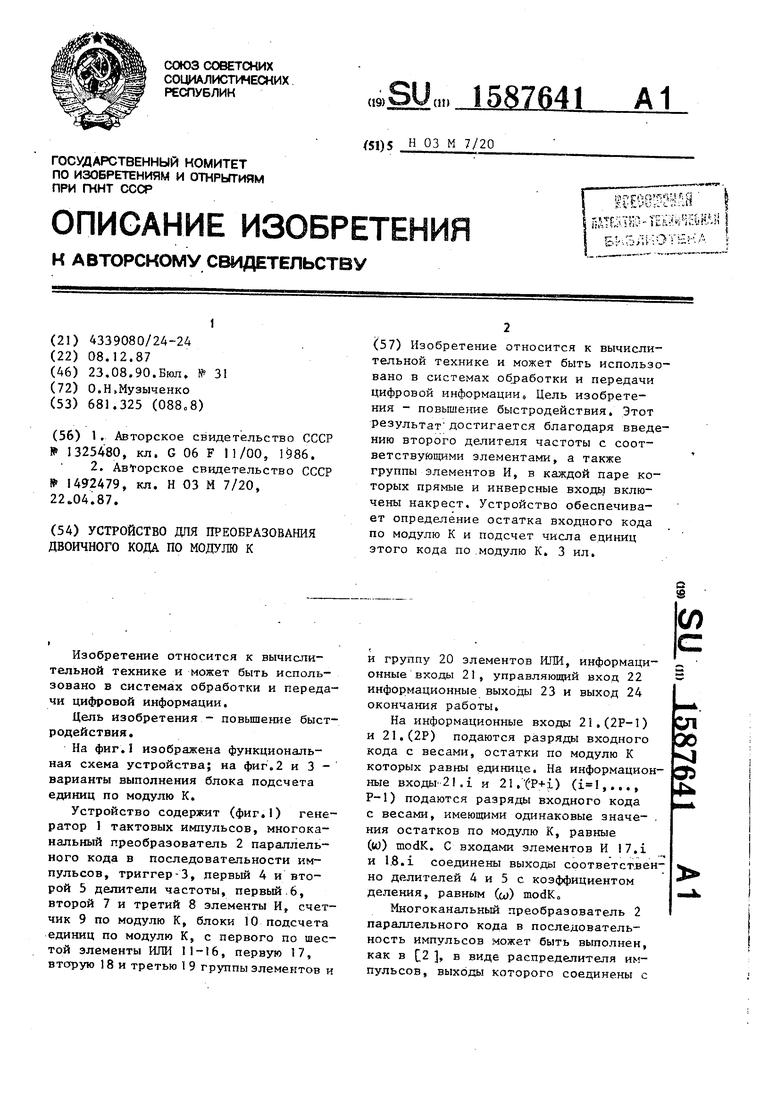

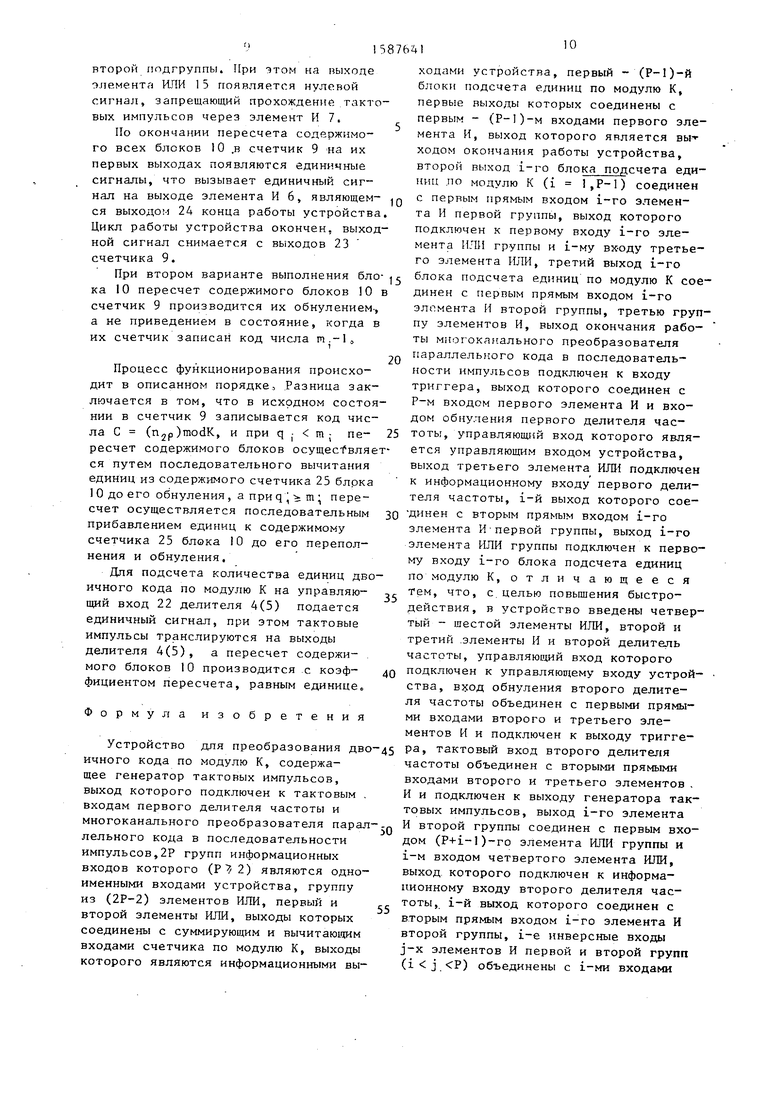

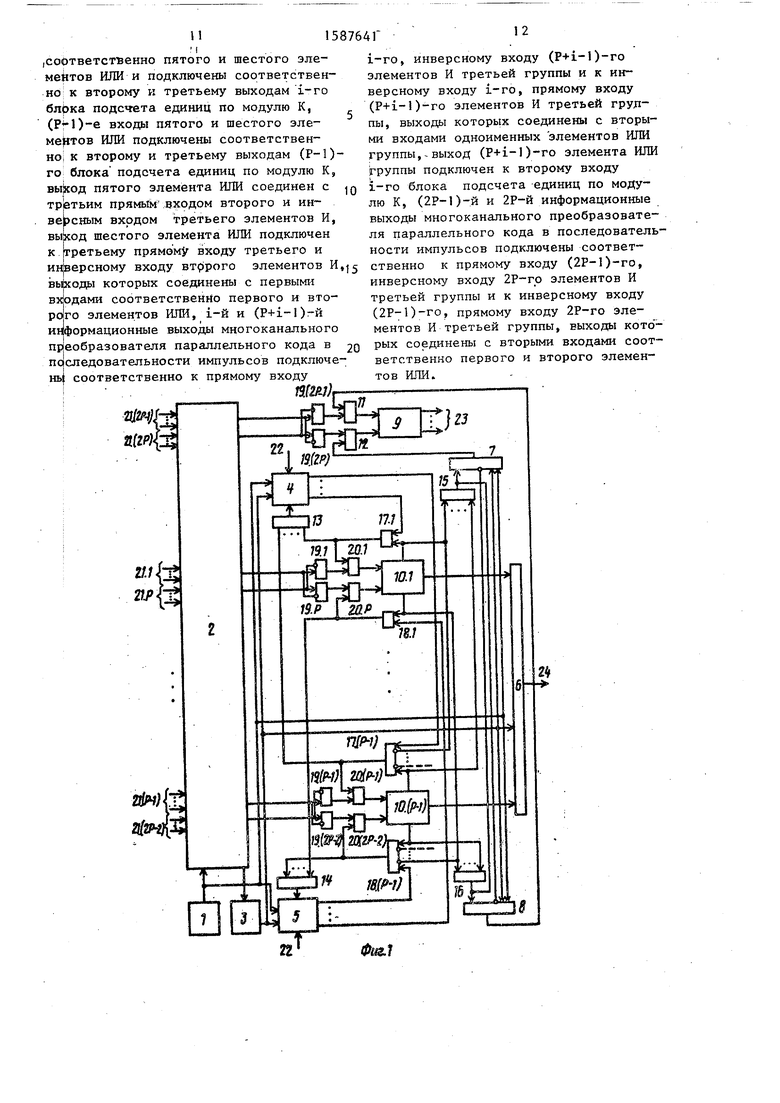

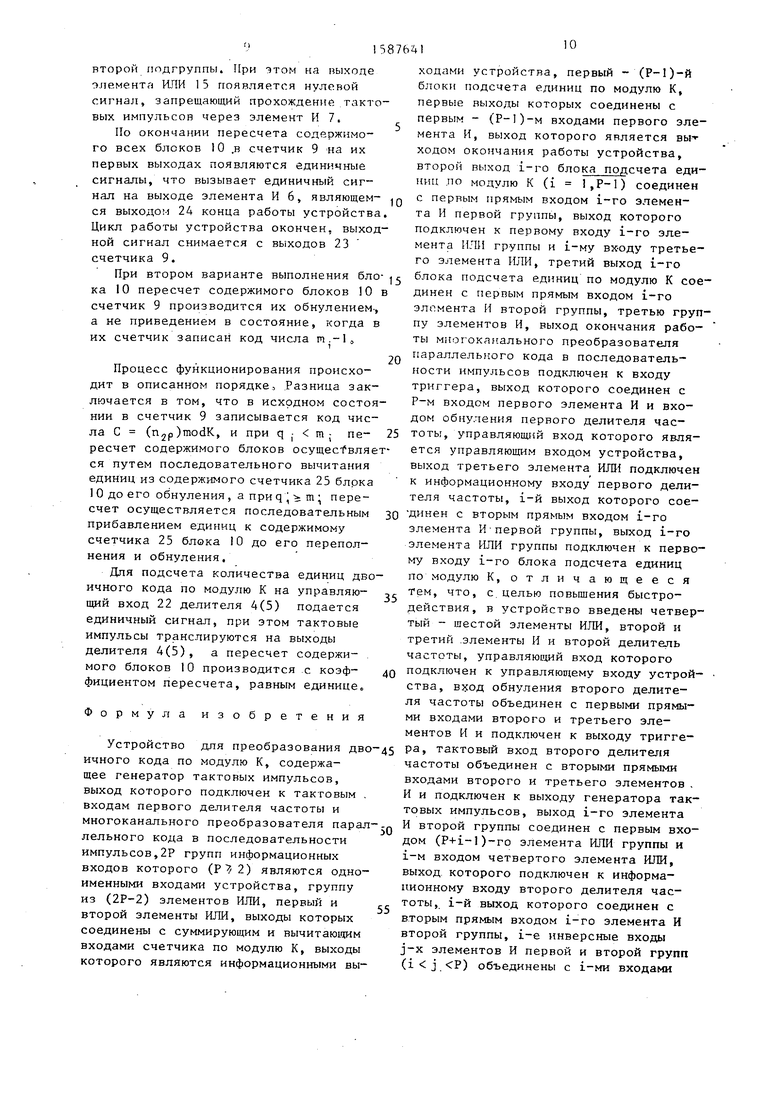

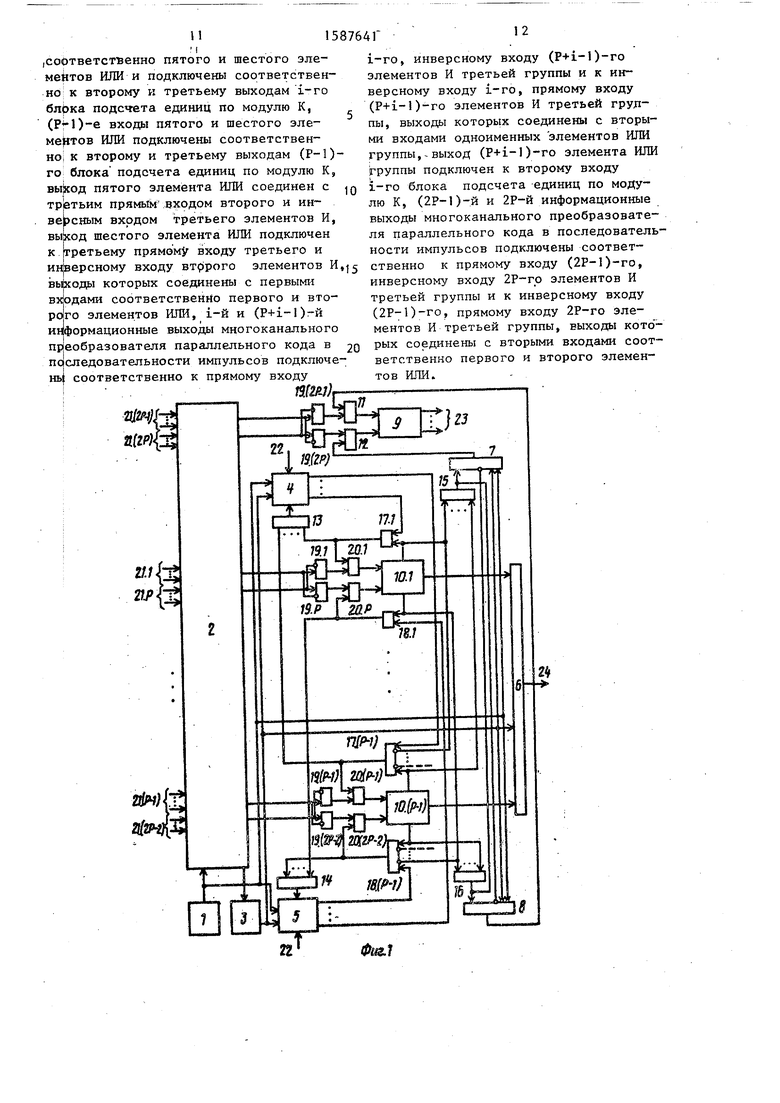

На фиг.1 изображена функциональная схема устройства; на фиг.2 и 3 - варианты выполнения блока подсчета единиц по модулю К.

Устройство содержит (фиг.1) генератор 1 тактовых импульсов, многоканальный преобразователь 2 параллельного кода в последовательности импульсов, триггер-3, первый 4 и второй 5 делители частоты, первый.6, второй 7 и третий 8 элементы И, счетчик 9 по модулю К, блоки 10 подсчета единиц по модулю К, с первого по шестой элементы ИЛИ 11-16, первую 17, вторую 18 и третью 1 9 группы элементов и

и группу 20 элементов ИЛИ, информационные входы 21, управляющий вход 22 информационные выходы 23 и выход 24 окончания работы.

На информационные входы 21.(2Р-1) и 21.(2Р) подаются разряды входного кода с весами, остатки по модулю К которых равны единице. На информационные входы-21.1 и 21. ( P+i) (

Р-1) подаются разряды входного кода с весами, имеющими одинаковые значе- . ния остатков по модулю К, равные (Ю) modK. С входами элементов И 17.1 и 1.8.1 соединены выходы соответственно делителей 4 и 5 с коэффициентом деления, равным (о)) modK,

Многоканальный преобразователь 2 параллельного кода в последовательность импульсов может быть выполнен, как в , в виде распределителя импульсов, выходы которого соединены с

сд

Эб

зь

4;:

10

15

20

первыми входами элементов И 2Р групп (2Р - число каналов преобразователя, вторые входы элементов И каждой группы являютсяг входами соответствующего .канала преобразователя, а выходы соединены с входами элемента ИЛИ, выход которого является выходом канала пре образователя, тактовый вход распреде™ лителя импульсов является тактовым входом преобразователя, а выход последнего разряда распределителя - выходом конца преобразования.

Многоканальный преобразователь 2 параллельного Кода в последовательность импульсов может быть также выполнен в виде 2Р регистров сдвига, соединенных информационными входами с информационньши входами преобразователя, тактовыми входами - с его тактовым входом, а выходами переноса - с выходами каналов преобразователя, инверсные,выходы каждого регистра сдвига соединены с входами своего элемента И, а их выходы - с входами эле-25 мента И,выход которого является выходом- конца преобразования,входы разрешения - записи регистров сдвига соединены с вхо- дом разрешения записи преобразователя.

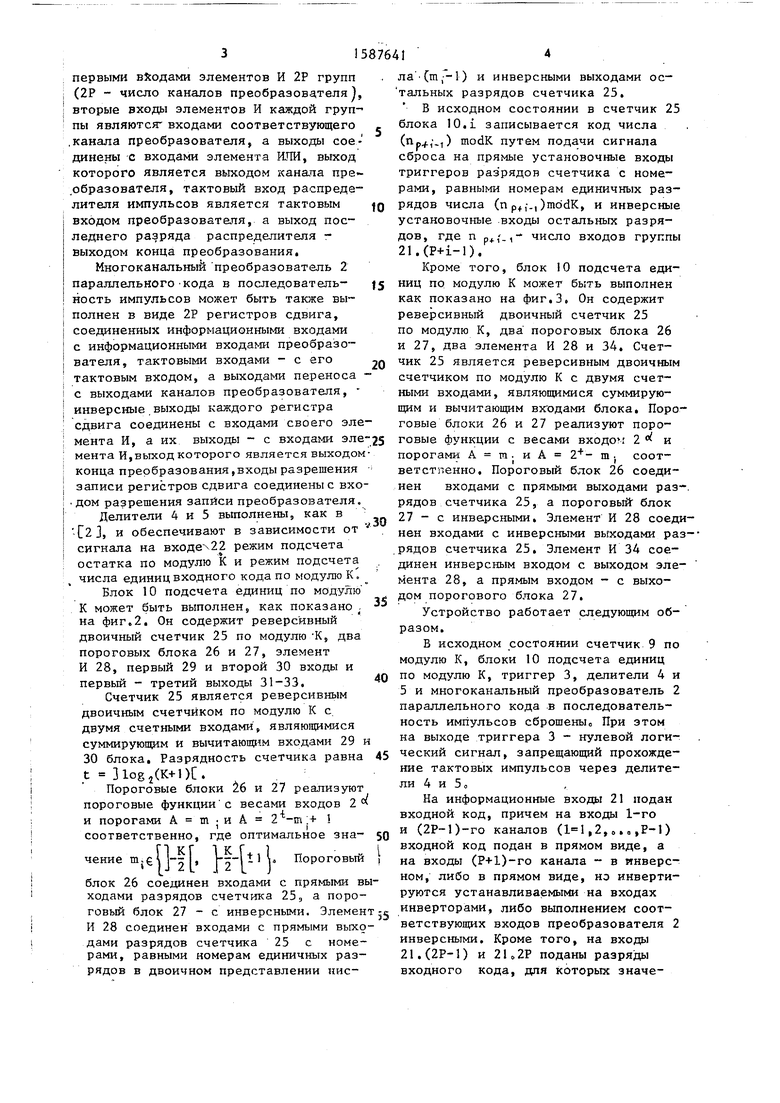

Делители 4 и 5 выполнены, как в -C2J, и обеспечивают в зависимости от сигнала на входе-х22 режим подсчета остатка по модулю К и режим подсчета числа единиц входного кода по модулю К, Блок 10 подсчета единиц по модулю К может быть выполнен, как показано. на фиг.2. Он содержит реверсивный двоичный счетчик 25 по модулю К, два пороговых блока 26 и 27, элемент И 28, первый 29 и второй 30 входы и первый - третий выходы 31-33.

Счетчик 25 является реверсивным двоичным счетчиком по модулю К с двумя счетными входами, являющимися

. ла (т;-1) и инверсными выходами остальных разрядов счетчика 25,

В исходном состоянии в счетчик 25 блока 10,1 записывается код числа (Пр,,,) modK путем подачи сигнала сброса на прямые установочные входы триггеров разрядов счетчика с номерами, равными номерам единичных разрядов числа (п .,)mddK, и инверсные установочные входы остальных разрядов, где п р,. , число входов группы 21,(P+i-l),

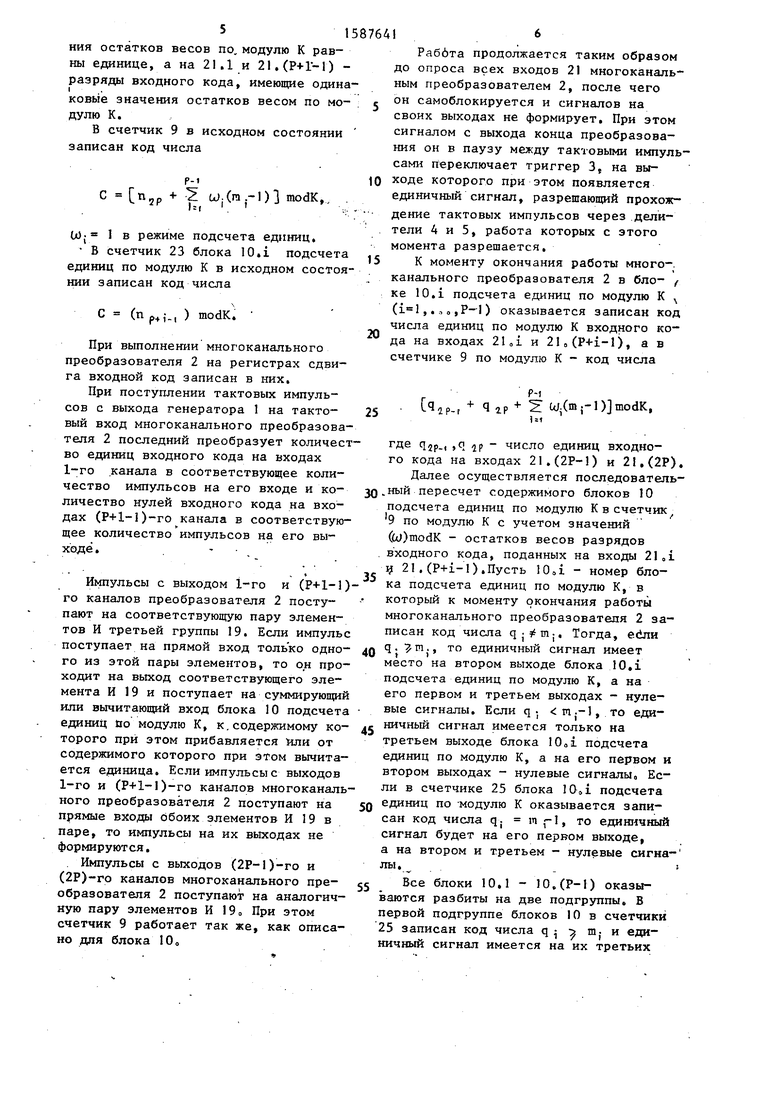

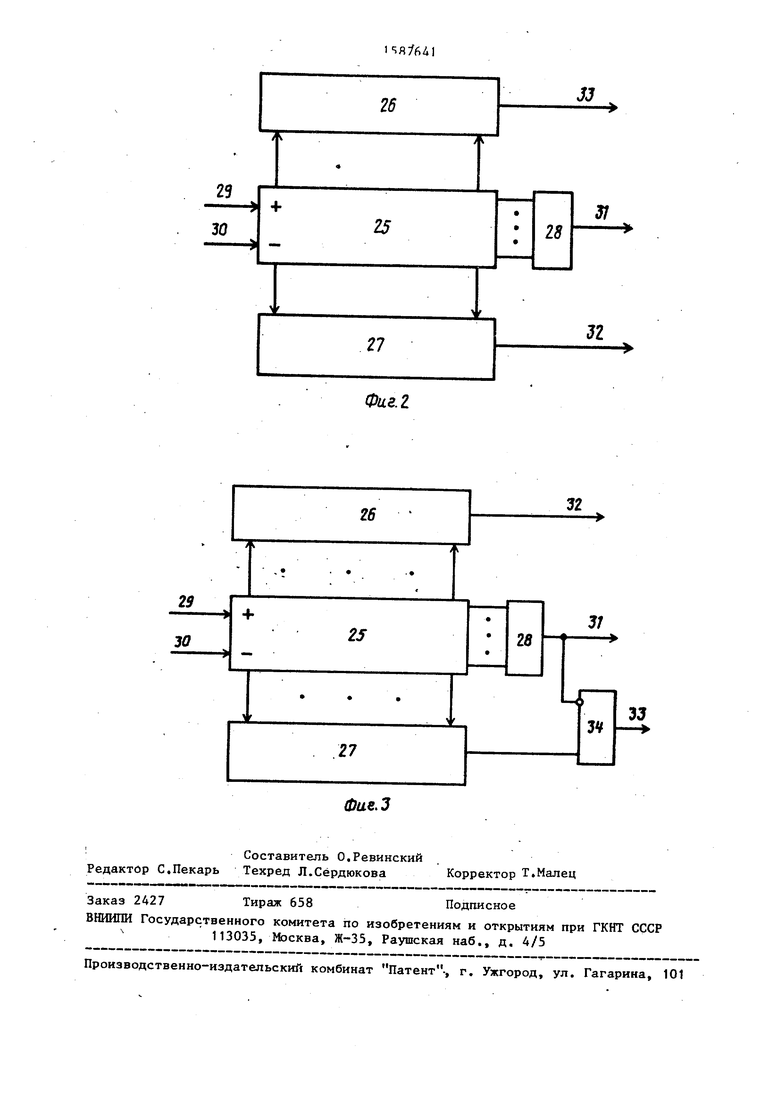

Кроме того, блок 10 подсчета единиц по модулю К может быть выполнен как показано на фиг,3. Он содержит реверсивный двоичный счетчик 25 по модулю К, два пороговых блока 26 и 27, два элемента И 28 и 34, Счетчик 25 является реверсивным двоичным счетчиком по модулю К с двумя счетными входами, являющимися суммирующим и вычитающим входами блока. Пороговые блоки 26 и 27 реализуют пороговые функции с весами входог: 2 и порогами А m. и А m . соот- ветстпенно. Пороговый блок 26 соединен входами с прямыми выходами разрядов счетчика 25, а пороговый блок 27 - с инверсньп-1и. Элемент И 28 соеди нен входами с инверсными вь ходами раз рядов счетчика 25, Элемент И 34 соединен инверсным входом с выходом элемента 28, а прямым входом - с выходом порогового блока 27,

Устройство работает следующим образом,

В исходном состоянии счетчик 9 по модулю К, блоки 10 подсчета единиц по модулю К, триггер 3, делители 4 и 5 и многоканальный преобразователь 2 параллельного кода в последовательность импульсов сброшеныо При этом на выходе триггера 3 - нулевой логи30

35

40

суммирующим и вычитающим входами 29 и

30 блока. Разрядность счетчика равна 45 ческий сигнал, запрещающий прохождение тактовых импульсов через делители 4 и 5 о

t 3log2(K+l)C,

Пороговые блоки 6 и 27 реализуют пороговые функции с весами входов 2

А 1

и порогами А m и соответственно, где

чение m

оптимальное знаi4H Пороговый

50

i

Элемент -g

блок 26 соединен входами с прямыми выходами разрядов счетчика 25, а пороговый блок 27 - с инверсными И 28 соединен входами с прямыми выхо дами разрядов счетчика 25 с номерами, равными номерам единичных разрядов в двоичном представлении нис10

15

20

25- -

876414

. ла (т;-1) и инверсными выходами остальных разрядов счетчика 25,

В исходном состоянии в счетчик 25 блока 10,1 записывается код числа (Пр,,,) modK путем подачи сигнала сброса на прямые установочные входы триггеров разрядов счетчика с номерами, равными номерам единичных разрядов числа (п .,)mddK, и инверсные установочные входы остальных разрядов, где п р,. , число входов группы 21,(P+i-l),

Кроме того, блок 10 подсчета единиц по модулю К может быть выполнен как показано на фиг,3. Он содержит реверсивный двоичный счетчик 25 по модулю К, два пороговых блока 26 и 27, два элемента И 28 и 34, Счетчик 25 является реверсивным двоичным счетчиком по модулю К с двумя счетными входами, являющимися суммирующим и вычитающим входами блока. Пороговые блоки 26 и 27 реализуют пороговые функции с весами входог: 2 и порогами А m. и А m . соот- ветстпенно. Пороговый блок 26 соединен входами с прямыми выходами раз, рядов счетчика 25, а пороговый блок 27 - с инверсньп-1и. Элемент И 28 соединен входами с инверсными вь ходами разрядов счетчика 25, Элемент И 34 соединен инверсным входом с выходом элемента 28, а прямым входом - с выходом порогового блока 27,

Устройство работает следующим образом,

В исходном состоянии счетчик 9 по модулю К, блоки 10 подсчета единиц по модулю К, триггер 3, делители 4 и 5 и многоканальный преобразователь 2 параллельного кода в последовательность импульсов сброшеныо При этом на выходе триггера 3 - нулевой логи30

35

40

ческий сигнал, запрещающий прохожде

ние тактовых импульсов через делители 4 и 5 о

На информационные входы 21 подан входной код, причем на входы 1-го и (2Р-1)-го каналов (,2,,.„,Р-1) входной код подан в прямом виде, а на входы (Р+1)-го канала - в инверсном, либо в прямом виде, но инвертируются устанавливаемыми на входах инверторами, либо выполнением соответствующих входов преобразователя 2 инверсными. Кроме того, на входы 21,(2Р-1) и 2К2Р поданы разряды входного кода, дпя которых значе51587641

ния остатков весов по, модулю К равны единице, а на 21.1 и 21.(Р-Ц-1) - разряды входного кода, имеющие одинаковые значения остатков весом по модулю К.

В счетчик 9 в исходном состоянии записан код числа

J о

Р-1 С + . Z (x)j(ra.-l)3 modK,, .

W; 1 В режиме подсчета единиц,

В счетчик 23 блока ЮЛ подсчета единиц по модулю К в исходном состоянии записан код числа

С (п р,-., ) modK.

При выполнении многоканального преобразователя 2 на регистрах сдвига входной код записан в них.

При поступлении тактовых импульсов с выхода генератора 1 на тактовый вход многоканального преобразователя 2 последний преобразует количество единиц входного кода на входах 1-го канала в соответствующее количество импульсов на его входе и количество нулей входного кода на входах (Р+1-1)-го канала в соответствующее количество импульсов на его выходе.

где qjp., ,q p - число единиц входн го кода на входах 21.(2Р-) и 21. Далее осуществляется последова 30-ный пересчет содержимого блоков 1 подсчета единиц по модулю К в счет 9 по модулю К с учетом значений (w)modK - остатков весов разрядов входного кода, поданных на входы у 21. (P+i-1).Пусть ОЛ - номер б ка подсчета единиц по модулю К, в которьш к моменту окончания работ многоканального преобразователя 2 писан код числа . Тогда, ейл

35

И myльcы с выходом 1-го и (Р+1-1)- го каналов преобразователя 2 поступают на соответствующую пару элементов И третьей группы 19. Если импульс.. --- , , . -,. -.„„, .. поступает на прямой вход только одно- 40 Ч- единичный сигнал имеет го из этой пары элементов, то он про- место на втором выходе блока 10,i ходит на выход соответствующего элемента И 19 и поступает на суммирующий или вычитающий вход блока 10 подсчета единиц QO модулю К, к.содержимому ко- 45 торого при этом прибавляется или от содержимого которого при этом вычитается единица. Если импульсы с выходов 1-го и СР+1-1)-го каналов многоканального преобразователя 2 поступают на прямые входы сэбоих элементов И 19 в паре, то импульсы на их выходах не формируются.

Импульсы с выходов (2Р-1)-го и (2Р)-го каналов многоканального преобразователя 2 поступают на аналогичную пару элементов И 19а При этом счетчик 9 работает так же, как описано для блока 10,

подсчета единиц по модулю К, а на его первом и третьем выходах - нул вые сигналы. Если q п.-1, то ед ничный сигнал имеется только на третьем выходе блока lOoi подсчета единиц по модулю К, а на его перво втором выходах - нулевые сигналы. ли в счетчике 25 блока ШЛ подсче 50 единиц по -модулю К оказывается зап сан код числа q j in ,-1, то единич сигнал будет на его первом выходе, а на втором и третьем - нулевые си лы.

55 Все блоки 10.1 - 10.(Р-1) оказы 1ваются разбиты на две подгруппы. В первой подгруппе блоков 10 в счетч 25 записан код числа q - т- и ед ничный сигнал имеется на их третьих

Раббта продолжается таким образом до опроса всех входов 21 многоканальным преобразователем 2, после чего он самоблокируется и сигналов на

своих выходах не формирует. При этом сигналом с выхода конца преобразования он в паузу между тактовыми импульсами переключает триггер 3, на выходе которого при этом появляется единичный сигнал, разрешающий прохождение тактовых импульсов через делители 4 и 5, работа которых с этого момента разрешается.

К моменту окончания работы много-, канального преобразователя 2 в бло- ке lO.i подсчета единиц по модулю К (,., о ,) оказывается записан код числа единиц по модулю К входного кода на входах 21,i и 21„(Р+1-1), а в счетчике 9 по модулю К - код числа

Р-) 25 Cq-ip., + qip+ 2: W Cmj-DjmodK,

где qjp., ,q p - число единиц входного кода на входах 21.(2Р-) и 21.(2Р). Далее осуществляется последователь- 30-ный пересчет содержимого блоков 10 подсчета единиц по модулю К в счетчик 9 по модулю К с учетом значений (w)modK - остатков весов разрядов входного кода, поданных на входы 21„i у 21. (P+i-1).Пусть ОЛ - номер блока подсчета единиц по модулю К, в которьш к моменту окончания работы многоканального преобразователя 2 записан код числа . Тогда, ейли

5

.. --- , , . -,. -.„„, .. 0 Ч- единичный сигнал имеет место на втором выходе блока 10,i 5

.. --- , , . -,. -.„„, .. Ч- единичный сигнал имеет место на втором выходе блока 10,i

подсчета единиц по модулю К, а на его первом и третьем выходах - нулевые сигналы. Если q п.-1, то единичный сигнал имеется только на третьем выходе блока lOoi подсчета единиц по модулю К, а на его первом и втором выходах - нулевые сигналы. Если в счетчике 25 блока ШЛ подсчета единиц по -модулю К оказывается записан код числа q j in ,-1, то единичршй сигнал будет на его первом выходе, а на втором и третьем - нулевые сигна- лы. i

Все блоки 10.1 - 10.(Р-1) оказы- 1ваются разбиты на две подгруппы. В ервой подгруппе блоков 10 в счетчики 5 записан код числа q - т- и едиичный сигнал имеется на их третьих

ыходах, о второй подгруппе блоков 10 в счетчики 25 записан код числа i п и единичный сигнал имеется а их вторых выходах,

Далее в каждой из укаэа:нных групп оследовательно, а в обеих подгруппах дновременно происходит процесс пересчета содержимого блоков 10 в счетчик

путем приведения каждого изблоков д

10в состояние, при котором н его счетчик 25. записан код числа q. ra ,--1.

Пусть 10.L - наименьший номер бло- ка подсчета единиц по модулю К пер- 15 вой подгруппы. На его третьем выходе 33 единичный сигнал, поступающий на вход элемента И 18oi, на инверсных входах которого, соединенных с третьими выходами блоков 10.1-10(1-1) - 20 нулевые сигналы, что разрешает прохождение тактовых импульсов с выхода делителя 5 на выход элемента И ISdo Импульсы с выхода элемента И 18.1 поступают на вход элемента ИЛИ 25 20.(P+i-l) и на вход элемента ИЛИ 14, Импульсы, поступающие на вход элемента ИЛИ 20.(Р+1-1).проходят на его выход .и поступают на вычитающий вход блока 0.i,OT содержимого которого 30 .каждый раз вычитается единица. При этом импульс с выхода делителя 5 поступает на вход элемента И 18,1 через (a)modK тактовых импульсов, поступающих на та.ктовый вход делителя 5 с выхода генератора 1. Проходя через элемент И 18.1, импульс с выхода делителя 5 поступает через элемент RTM 14 на вход сброса делителя 5, возвращая его в исходное состояние. дО

Пусть lO.h - наименьший номер блока подсчета единиц по модулю К второй подгруппы. На его третьем выходе нулевой сигнал, а на втором - единичный, поступающий на вход элемента И 45 17.h, на инверсных входах которого, соединенных с вторыми выходами блоков 10.1 -lO.(h-l), - нулевые сигналы, что разрешает прохождение импульсов с выхода делителя 4 на выход эле- Q мента И 17.h. Импульсы с выхода элемента И 17.h поступают на вход элемента ИЛИ 20.h, проходят на его выход и поступают на суммирующий вход блока lOih, к содержимому которого каждый раз прибавляется единица. При этом импульс с выхода делителя 4 поступает на вход элемента И через (io)raodK тактовых импульсов, пос35

5 0 5 0 О

5 Q

5

тупающих на тактовый вход делителя 4 с выхода генератора I. Одновременно импульс с выхода элемента И 17„Ь поступает на вход элемента ИЛИ 13, проходит на его выход и поступает на вход сброса делителя 4, возвращая его в исходнЬе состояние.

Пока происходит процесс пересчета содержимого блоков 10.1 первой подгруппы, хотя бы на одном из третьих выходов блоков 10 имеется единичный сигнал, который проходит через элемент ИЛИ 16 и поступает на инверсный вход элемента И 7, запрещая прохождение тактовых импульсов на его выход Пока происходит процесс пересчета содержимого блоков lOoh второй подгруппы, хотя бы на одном из вторых выходов блоков 10 имеется единичный сигнал, который проходит через элемент ИЛИ 15 на инверсный вход элемента И 8, запрещая прохождение тактовых импульсов на его выход

Если раньше закончится пересчет содержимого блоков lO.h второй подгруппы, то на выходе элемента ИЛИ 15 появится нулевой логический сигнал, который запретит прохождение тактовых импульсов через элемент И 7 и разрешит их прохождение через элемент И Во При этом тактовые импульсы с выхода элемента И 8 поступают на вход элемента ИЛИ 11, проходят на его выход и поступают на суммирующий вход счетчика 9, к содержимому которого каждый раз прибавляется единица. Работа происходит таким образом до окончания п-ерёсчета содержимого блоков 10.1 первой подгруппы. При этом на выходе элемента ИЛИ 16 появляется нулевой сигнал, запрещающими прохождение тактовых импульсов через элемент И 8.

Если раньше закончится пересчет содержимого блоков 10 первой подгруппы, то на выходе элемента ИЛИ 16 появится нулевой логический сигнал, который запретит прохождение тактовых импульсов через элемент И 8 и разрешит их прохождение через элемент И 7. При этом тактовые импульсы с выхода элемента И 7 поступают на вход элемента ИЛИ 12, проходят на его выход и поступают на вычитающий вход счетчика 9, от содержимого которого при этом вычитается единица. Работа происходит таким образом до окончания пересчета содержимого блоков lO.h

второй подгруппы. При этом на выходе элемента ИЛИ 15 появляется нулевой сигнал, запрещающий прохожде.ние тактовых импульсов через элемент И 7,

По окончании пересчета содержимого всех блоков 10 .в счетчик 9 на их первых выходах появляются единичные сигналы, что вызывает единичный сигнал на выходе элемента И 6, являющемся выходом 24 конца работы устройства. Цикл работы устройства окончен, выходной сигнал снимается с выходов 23 счетчика 9.

При втором варианте выполнения бло ка 10 пересчет содержимого блоков 10 в счетчик 9 производится их обнулением-, а не приведением в состояние, когда в их счетчик записан код числа m.-I,

Процесс функционирования происходит в описанном порядке. Разница заключается в том, что в исходном состоянии в счетчик 9 записывается код числа С (n2p)raodK, и при q I Ш; пе- 25 расчет содержимого блоков осуществляется путем последовательного вычитания единиц из содержимого счетчика 25 блока 1 О до его обнуления , а при q m; пересчет осуществляется последовательным прибавлением единиц к содержимому счетчика 25 блока 10 до его переполнения и обнуления.

Для подсчета количества единиц двоичного кода по модулю К на управляющий вход 22 делителя 4(5) подается единичный сигнал, при этом тактовые импульсы транслируются на выходы делителя 4(5), а пересчет содержимого блоков 10 производится с коэффициентом пересчета, равным единице.

Формула изобрет

ходами устройства, первый - (Р-1)-й блоки подсчета единиц по модулю К, первые выходы которых соединены с первым - (Р-1)-м входами первого элемента И, выход которого является вы ходом окончания работы устройства, второй выход 1-го блока подсчета единиц по модулю К (i 1,Р-1) соединен 10 первым прямым входом i-ro элемента И первой группы, выход которого подключен к первому входу i-ro элемента ИЛИ группы и t-му вх-оду третьего элемента ИЛИ, третий выход i-ro ,5 блока подсчета единиц по модулю К соединен с первым прямым входом i-ro элемента И второй группы, третью группу элементов И, выход окончания рабо- ты многоканального преобразователя 2Q Г1араллельного кода в последовательности импульсов подключен к входу триггера, выход которого соединен с Р-м входом первого элемента И и входом обнуления первого делителя частоты, управляющий вход которого является управляющим входом устройства, выход третьего элемента ИЛИ подключен к информационному входу первого делителя частоты, i-й выход которого сое- 30 Динен с вторым прямым входом i-ro элемента И-первой группы, выход i-ro элемента ИЛИ группы подключен к первому входу i-ro блока подсчета единиц по модулю К, отличающееся тем, что, с, целью повышения быстродействия, в устройство введены четвертый - шестой элементы ИЛИ, второй и третий .элементы И и второй делитель частоты, управляющий вход которого подключен к управляющему входу устрой- ства, вход обнуления второго делителя частоты объединен с первыми прямы- е н и я ми входами второго и третьего эле35

40

ментов И и подключен к выходу триггедля преобразования дво-дз Ра, тактовый вход второго делителя

частоты объединен с вторыми прямыми входами второго и третьего элементов И и подключен к выходу генератора тактовых импульсов, выход i-ro элемента И второй группы соединен с первым входом (P+i-l)-ro элемента ИЛИ группы и i-M входом четвертого элемента ИЛИ, выход которого подключен к информационному входу второго делителя частоты, i-й выход которого соединен с вторым прямым входом i-ro элемента И второй группы, i-e инверсные входы J-X элементов И первой и второй групп (i j Р) объединены с i-ми вxoдa и

Устройство

ичного кода по модулю К, содержащее генератор тактовых импульсов, выход которого подключен к тактовым входам первого делителя частоты и многоканального преобразователя парап--„ лельного кода в последовательности импульсов,2Р групп информационных входов которого () являются одноименными входами устройства, группу из (2Р-2) элементов ИЛИ, первый и второй элементы ИЛИ, выходы которых соединены с суммирующим и вычитаю1 щм входами счетчика по модулю К, выходы которого являются информационными вы55

,соответственно пятого и шестого эле- мейтов ИЛИ и подключены соответственно к второму и третьему выходам i-ro 6л|7ка подсчета единиц по модулю К, ()-в входы пятого и шестого эле- мертов ИЛИ подключены соответственно к второму и третьему выходам (Р-1)- го блока подсчета единиц по модулю К, пятого элемента ИЛИ соединен с JQ третьим прямым- входом второго и инверсным входом третьего элементов И, шестого элемента ИЛИ подключен к третьему прямому входу третьего и

i-ro, инверсному входу (P+i-l)-ro элементов И третьей группы и к инверсному входу i-ro, прямому входу (P+i-l)TO элементов И третьей группы, выходы которых соединены с вторы ми входами одноименных элементов ИЛ группы,-выход (P+i-l)-ro элемента ИЛ группы подключен к второму входу 1-го блока подсчета единиц по моду лю К, (2Р-1)-й и 2Р-Й информационны выходы многоканального преобразоват ля параллельного кода в последовате ности импульсов подключены соответинверсному входу втррого элементов И. ственно к прямому входу (2Р-1)-го,

вьвсода которых соединены с первыми входами соответственно первого и второго элементов ИЛИ, i-й и (P+i-l)r-H информационные выхода многоканального пр еобразователя параллельного кода в 20 пс1следовательности импульсов подключе- Hbi соответственно к прямому входу КП{Ш),

инверсному входу 2Р-гр элементов И третьей группы и к инверсному входу (2Р-1)-го, прямому входу 2Р-ГО элементов И третьей группы, выходы кот рых соединены с вторыми входами соо ветственно первого и второго элемен тов ИЛИ.

«3

afzpfe

i-ro, инверсному входу (P+i-l)-ro элементов И третьей группы и к инверсному входу i-ro, прямому входу (P+i-l)TO элементов И третьей группы, выходы которых соединены с вторыми входами одноименных элементов ИЛИ группы,-выход (P+i-l)-ro элемента ИЛИ группы подключен к второму входу 1-го блока подсчета единиц по модулю К, (2Р-1)-й и 2Р-Й информационные выходы многоканального преобразователя параллельного кода в последовательности импульсов подключены соответственно к прямому входу (2Р-1)-го,

инверсному входу 2Р-гр элементов И третьей группы и к инверсному входу (2Р-1)-го, прямому входу 2Р-ГО элементов И третьей группы, выходы кото - рых соединены с вторыми входами соответственно первого и второго элементов ИЛИ.

„. I Р J

Фа$.1

Фиг.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования двоичного кода по модулю К | 1987 |

|

SU1587642A1 |

| Устройство для подсчета числа единиц двоичного кода | 1987 |

|

SU1569995A1 |

| Устройство для подсчета числа единиц двоичного кода по модулю К | 1986 |

|

SU1427574A1 |

| Устройство для преобразования двоичного кода в код по модулю К | 1987 |

|

SU1492479A1 |

| Устройство для контроля двоичного кода по модулю К | 1990 |

|

SU1737736A1 |

| Устройство для контроля количества единиц двоичного кода по модулю К | 1986 |

|

SU1401461A1 |

| Устройство для контроля равновесного кода | 1987 |

|

SU1580563A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПАРАЛЛЕЛЬНОГО ДВОИЧНОГО КОДА ПО МОДУЛЮ K | 1991 |

|

RU2020760C1 |

| Устройство для обнаружения ошибок в параллельном коде | 1987 |

|

SU1564733A1 |

| Устройство для подсчета числа единиц двоичного кода по модулю К | 1986 |

|

SU1438006A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах обработки и передачи цифровой информации. Цель изобретения повышение быстродействия. Это достигается благодаря введению второго делителя частоты с соответствующими элементами, а также группы элементов И, в каждой паре которых прямые и инверсные входы включены накрест. Устройство обеспечивает определение остатка входного кода по модулю К и подсчет числа единиц этого кода по модулю К. 3 ил.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для преобразования двоичного кода в код по модулю К | 1987 |

|

SU1492479A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-08-23—Публикация

1987-12-08—Подача