соединен с входом синхронизации регистра адреса решающего блока, четвертьй выход первой группы выходов распределителя импульсов решающего блока соединен с управляющими, входами ключей первой группы решающего блока, пятый выход первой/. группы выходов распределителя импульсов решающего блока соединен с первыми входами элементов И первой группы решающего блока, щестой выход первой группы выходов распределителя импульсов решающего блока соединен с первыми входами элементов И второй группы решающего блока седьмой выход первой группы выходов распределителя импульсов, решаю:щегЬ блока соединен с управляющими входами ключей второй группы рещающего блока, восьмой выход первой группы выходов распределителя импульсов решающего блока соединен с входом синхронизации регистра команд решающего блока, девятьй выход первой группы выходов распре делителя импульсов решающего бло- . ка соединен с входом синхронизации регистра результата итерации решающего блока, десятый выход первой группы выходов распределителя импульсов решающего блока с.оединен с входом синхрониза1 сии регистра ле вой точки решающего блока одиннадцатый выход первой группы выходов распределителя импульсов решающегоблока соединен с управляющим входом сумматора решающего блока, двенад:цатьй выход первой группы выходов распределителя импульсов решающего блока соединен с входом синхронизадаи регистра правой точки решающего блока, пбрвая группа входов распределителя импульсов решающего блока соединена с выходами дешифратора команд решающего блока, входы которого соединены с выходами регистра команд решающего блока, выходы кдю|чей второй группы решающего блока ;соединены с информационными входами регистра коэффициента, регистра команд, регистра правой точки, первыми группами информационных входов регистра результата итерации и регистра левой точки решающего блока выходы счетчика команд решающего блока соединены с информационными входами регистра адреса решающего блока, выходы регистра правой точки 49 решающего блока соединены с входами первого слагаемого сумматора решающего блока, входы второго слагаемого которого соединены с информационнь1ми входами регистра левой точки решающего блока, выходы сумматора решающего блока соединены с второй группой информационных входов регистра результата итерации решающего блока, правая группа выходов которого соединена :с второй группой информационных входов регистра левой точки решающего блока, выходы регистра коэффициента решающего блока соединены с вторыми входами элементов И первой группы решающего блока, вторая группа выходов регистра результата итерации решающего блока соединена с вторьми входами элементов И второй группы решающего блока i выходь элементов И первой :и второй групп решающего блока соединены соответственно с первыми и вторыми входами элементов ИЛИ групп, выходы которых соединень: с информа- ционными входами ключей первой груп-1пы решающего блока, первый выход :второй группы выходов распределителя импульсов решающего блока соединен с входом записи узла памяти решающего блока, второй выход второй Труппы выходов распределителя импульсов решающего блока соединен с входом чтения узла памяти решающего блока, информационные входы ключей второй группы решающего блока соединены с выходами узла памяти решающего блока, выходы ключей первой руппы решающего блока соединены с информационными входами узла памяти решанмдего блока, выходы регистра адреса решающего блока соединены с адресными входами узла памяти решающего блока, отличающееся тем, что, с целью повьш1ения производительности, в него введены группа из К блоков запроса прерывания и блок приоритетного прерывания, причем казкдый блок запроса пре рывания содержит дешифратор адреса, .элемент И, триггер, выход дешифра|тора адреса блока запроса прерывания соединен с первым входом элемен|та И блока запроса прерьгаания, которого соединен с. синхронизирующим входом триггера блока ;3айроса прерывания, блок приоритет|ного прерывания содержит регистр iaanpoca прерывания, регистр текущего состояния, дешифратор приоритета, триггер блокировки, элемент ИЛИ элемент И, триггер прерывания, регистр управления, дешифратор упра,ления, выходы регистра запроса прерьшаний блока приоритетного прерьтания соединены с первой группой входов дешифратора приоритетов, с первой группой информационных входо регистра управления и входами дешифратора управления блока приоритетного прерывания, первая группа выходов регистра текущего состояния блока приоритетного прерывания соединена с второй группой входов дешифратора приоритета блока приоритетного прерывания , выход которого соединен с первым входом элемента И блока приоритетного прерывания, второй вход которого соединен с вторым выходом регистра текущего состяния блока приоритетного прерывания, выход триггера блокировки блока приоритетного прерывания соединен с первым входом элемента И блока приоритетного прерывания, второй вход которого соединен с выходом элемента ИЛИ блока приоритетного прерывания, выход элемента И блока приоритетного прерывания соединен с информационным входом триггера прерывания блока приоритетного прерывания, выход которого соединен с входом триггера блокировки и с синхронизирующим входом регистра управления блока приоритетного прерывания, блок управления содержит две группы ключей, регистр предьщущей итерации, сумматор, де-t

шифратор команд, регистр текущей итерации, распределитель импульсов, выходы регистра адреса блока управления соединены с адресными входами узла памяти блока управления, выходы первой группы ключей блока управления соединены с информационными входами узла памяти блока управле-. ния, информационные выходы которого соединены с информационными входами второй группы ключей, .первый выход первой группы выходов распределителя импульсов блока управления с входом записц узла памяти блока управления, второй выход первой группы выходов распределителя импульсов блока управления соединен с входом чтения узла памяти блока управления, первый выход второй

34949

группы выходов распределитео|Я импУльсов блока управления соединен управляющим входом счетчика команд блока управления, второй выход второй группы выходов распределителя импульсов блока управления соединен с управляющим входом регистра адреса блока управления, третий выход второй группы выходов распределите-, ля импульсов блока управления соединен с управлякицими входами первой .группы ключей блока управления, .четвертый выход второй группы выходов распределителя импульсов блока управления соединен с управляющими входами второй группы ключей блока управления, пятьй выход второй группы выходов распределителя иМпульсов блока управления соединен с управляющим входом регистра команд блока управления, шестой выход второй группы выходов распределителя импульсов блока управления сое;Динен с управлякяцим входом регистра предьщущей итерации блока управления , седьмой выход второй группы выходов распределителя импульсов блока управления - с управляющим входом сумматора блока управления, восьмой выход второй группы выходов распределителя импульсов блока упрайления соединен с управлякмцим входом регистра текущей итерации блока управления, первая группа входов распределителя импульсов блока управления соединена с выходами дешифратора команд блока управления, входы которого соединены с выходами регистра команд блока управления, выходы второй группы ключей блока управления соединены с входами ре. гистра команд, регистра предьздущей итерации, первой Труппой входов регистра, текущей итерации блока управления, выходы счетчика команд блока управления соединеш | с входами ;регистра адреса блока управления, ;выходы регистра предьадущей итерации Яблока управления соединены с входа;ми первого слагаемого сумматора блока управления, входы второго слагаемого которого соединены с пер вой группой выходов регистра текущей итерации блока управления, выходы сумматора блока управления соединены с второй группой входов регистра текущей итерации блока управления, вторая группа выходов которого соединена с информационными входами первой группы ключей блока управления, выходы регистра адреса блока управления соединены с входами первого дешифратора адрес каждого коммутатора, выходы первой группы ключей блока управления соединены с входаьш регистра вывода каждого коммутатора и с второй группой входов регистра текущего состояния блока приоритетного прерывания, входы второй группы ключей блока управления соединены с выходами входных информационных ключей каждого коммутатора и с второй группой выходов регистра управления блока приоритетного прерывания, третий выход первой группы выходов распределителя импульсов блока управления соединен с вторым входом первого элемента И/каждого коммутатора, четвертьм выход первой группы выходов распределителя импульсов блока управления соединен с вторым входом третьего элемента И каждого коммутатора, пятьй выход первой группы выходов распределителя импульсов блока управления соединен с первым входом регистра текущего состояния блока приоритетного прерывания, шестой выход первой группы выходов распределителя импульсов блока управления соединен с третьим входом элемента И блока приоритетного прерывания, седьмой выход первой группы выходов распределителя импул сов блока управления соединен с синхронизируюсцим входом триггера прерывания блока приоритетного . прерывания, восьмой выход первой группы выходов распределителя импулсов блока управления соединен с первым управляющим входом регистра управления блока приоритетного пре|рывания, девятый выход первой группы выходов распределителя импульсов блока управления соединен с вторым управляющим входом регистра управления блока приоритетного прерывания первый выход которого соединен с вторым входом распределителя импульсов блока управления, выходы выходных информационный ключей -го коммутатора соединены с информационными входами второй группы ключей -го решающего блока, информационные входы регистра ввода -го коммутатора и информационный вход триггера i -го блока запроса прерывания соединены с выходами первой группы ключей -го решающего блока, входы второго дешифратора адреса -f -го коммутатора и входы дешифратора адреса -то блока запроса прерывания соединены с выходами регистра адреса ч -го решающего блока, второй вход четвертого элемента И i -го коммутатора и второй вход элемента И -го блока запроса прерывания соединены с третьим выходом второй группы выходов распределителя импульсов i -го решающего блока, второй вход второго элемента И , -го коммутатора соединен с четвертым выходо второй группы выходов распределителя импульсов i -го решающего блока, второй вход триггера запроса : -го коммутатора соединен с пятым выходом второй группы выходов распределителя импульсов f -го решающего блока выход триггера запроса -го коммутатора соединен с вторым входом распределителя импульсов i -го решающего блока, выход триггера V -го блока запроса прерывания соединен с соответствующим, входом регистра запроса прерьшания блока приоритетного прерывания, вход сброса триггера i -го блока запроса .прерывания соединен с соответструняцим выходом дешифратора управления блока приоритетного прерьгоания,вторая группа информационных входов регистра управления блока приоритетного прерывания соеддинена с логическим нулем устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения дифференциальных уравнений | 1982 |

|

SU1104513A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для решения дифференциальных уравнений | 1982 |

|

SU1108460A1 |

| Устройство для сопряжения вычислительной машины с телеграфными каналами связи | 1986 |

|

SU1392571A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1989 |

|

SU1734098A1 |

| Устройство для управления каналами | 1979 |

|

SU877519A1 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Устройство для сопряжения электронной вычислительной машины с каналами связи | 1988 |

|

SU1513463A2 |

| Устройство для решения дифференциальных уравнений | 1983 |

|

SU1233148A1 |

УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ДИФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ, содержащее блок управления, блок ввода-вывода, группу из К решающих блоков и группу из К коммутаторов, причем вход данных блока управления соединен с выходом блока ввода-вывода, выход результата блока управления соединен с информационным входом блока, ввода-вывода, блок управления содержит узел памяти, регистр адреса, счетчик Команд, регистр команд, дешифратор команд, причем информационные выходы регистра команд соединены с входами дешифратора команд каждый коммутатор содержит регистр ввода, регистр вывода, группу выходньпс информационных ключей, группу входных информационных ключей, четыре элемента И, два дешифратора адреса и триггер запроса, в каждом коммутаторе выходы регистра вывода кал1дого коммутатора соединены с информационными входами выходньк информационных ключей коммутатора, выходы регистра ввода кажДого коммутатора соединены с информационными входами входных информационных ключей, выход первого элемента И каждого коммутатора соединен с входом синхронизации регистра вывода и первым входом триггера запроса, выход второго элемента И -каждого коммутатора соединен с управляющими входами выходных информационных ключей, первого дешифратора адреса каждого коммутаторасоединен с первыми входами первого и третьего элементов И, выход третьего элемента И соединен с управляющими входами входных информационных ключей, выход второго дешифратора адS реса каждого коммутатора соединен с первыми входами второго и четверто го элементов И, выход четвертого элемента И каждого коммутатора соединен с входом синхронизации регистра ввода, решающий блок содержит регистр результата итерации, распре.делитель импульсов, регистр левой точки, дешифратор команд, регистр коэффициента, сумматор, регистр косо манд, счетчик команд, регистр правой точки, две группы ключей, две (;О 4ib группы элементов И, группу элементов ИЛИ, регистр адреса, узел памяСО ти, причем в каждом решающем блоке первый выход первой группы выходов распределителя импульсов соединен с входом синхронизации регистра коэффициента решающего блока, второй выход первой группы выходов распределителя импульсов решающего блока соединен со счетным входом счетчика команд решакицего блока, третий выход первой группы выходов распределителя импульсов решающего блока

Изобретение относится к цифровой вычислительной технике, а именно к устройствам для обработки цифровых

данных, и может быть использовано для решения дифференциальных уравнений в частных производных. Известны устройства для решения дифференциальных уравнений, содержащие решающие блоки, информационны связи, коммутаторы, информационную шину, блок ввода-вывода, блок упрай ления, а каждый решающий блок содер жит микропроцессор, запоминающий блок, группы элементов ИЛИ Щ. Недостатком этих устройств является ограниченная пропускная способность информационной шины, которая является общей для всех решающих блоков и позволяет осуществлять загрузку и обмен между решающими блоками последовательно, что снижает общую производительность. Наиболее близким к предлагаемому является устройство, содержащее решающие блоки, каждый из которых через соответствующий коммутатор. соединен двусторонними связями с информационной шиной, устройство управления, соединенное двусторонними связями с устройством вводавывода и с Информационной шиной, а каждый решающий блок содержит регис ры чтения и записи, ключи, узел/ связи, микропроцессор, соединенный двусторонними связями с запоминающим устройством, подключенным соответствуюпщм входом и выходом к выходу решающего блока, соединенными коммутаторами, управляющие входы каждого коммутатора соединены с соответствукмцими выходами устройства уп{эавления m . Недостатком этого устройства является низкая производительность которая является следствием того, что, с одной стороны, наличие общей управляющей шины для включения-выкл чения всех микропроцессоров обеспечивает только синхронный режим работы, а с другой стороны, наличие общей информационной шины, которая связывает между собой решаницие блоки, приводит к необходимости последовательного обмена информацией между решающими блоками, тогда как микропроцессоры, ожидая окончания обмена, простаивают. Цель изобретения - повышение пр изводительноетр устройства. - Поставленная цепь достигается тем, что в устройство для решения дифференциальных уравнений, содержащее блок управления, блок вводавывода, группу из К решающих блоков и группу из К коммута.оров, причем вход данных блока управления соединен с выходом блока ввода-вывода, выход результата блока управления соединен с информационным (ВХОДОМ блока ввода-вывода, блок управления содержит узел памяти, ре- . гистр адреса, счетчик команд, регистр команд, дешифратор команд, при-iчем информационные выходы регистра команд соединены с входами дешифраiTopa команд,/каждый коммутатор содержит регистр ввода, регистр вывода, группу выходных информационных ключей, группу входных информационных ключей,, четыре элемента И, два дешифратора адреса и триггер запро;са, выходы регистра вывода каждого коммутатора соединены с информационными входами выходных информационных ключей, выходы регистра ввода каждого коммутатора соединены с информационными входами входных информационных ключейj выход первого элемента И каждого коммутатора соединен с входом синхронизации регистра вывода. и первым входом триггера запроса, выход второго элемента И каждого коммутатора соединен с управляющ 1ми входами выходных информационных ключей, выход первого дешифратора адреса каждого коммутатора соединен с первыми входами первого и третьего элементов И, выход третьего элемента И коммутатора соединен с управлякяцими входами входщ пс информационных ключей, выход второго дешифратора адреса каждого коммутатора соединен с первыми входами второго и четвертого элементов И, выход четвертого элемента И каждого коммутатора соединен с входом синхронизации регистра ввЪда, рещанщий блок содержит регистр результата итерации, распределитель импульсов, регистр левой точки, дешифратор команд, регистр коэффициента,суммаTop, регистр команду счетчие команд регистр правой очки, две группы ключей, две группы элементов И, групЬпу элементов ИЛИ, регистр адреса, узел памяти, причем в каждом решающем блоке первьй выход первой rpynmJ выходов распределителя импульсов соединен с входом синхрониза1щи регистра коэффициента решающего блока, второй выход первой группы выходов распределителя импульсов решающего блока соедщнен со счетным

входом счетчика команд решающего блока,/третий выход первой групйы выходов распределителя импульсов решающего блока соединен с входом синхронизации регистра адреса решающего блока, четвертьй выход первой группы выходов распределителя импульсов решающего блока соединен с ;управлякяцими входами ключей первой :групш 1 решакнцего блока, пятый выход первой группы выходов распределителя импульсов решающего блока соединен с первыми входами элементов И первой группы решающего блока, шестой выход первой группы выходов распределителя импульсов решающего :блока соединен с первыми входами элементов И второй группы решающего блока, седьмой выход первой rpyniui выходов распределителя импульсов решающего блока соединен с управляющими входами ключей второй групп .решающего блока, восьмой выход первой группы выходов распределителя импульсов решающего блока соединен с входом синхронизации регистра команд решающего блока, девятый выход первой группы выходов распределителя импульсов решающего блока соединен с входом синхронизации регистра результата итерации решающего блока, десятый выход первой группы выходов распределителя импулсов решающего блока соединен с входом синхронизахщи регистра левой точки решающего блока, одиннадцатый выход первой группы выходов распределителя импульсов решакнцего блока соединен с управляющим входом сумматора решающего блока, двенадцатый выход первой группь выходов распределителя импульсов решающего блока соединен с входом синхронизации регистра правой точки решающего блока, первая группа входов распре, делителя импульсов решакнцего блока соединейа с выходами дешифратора команд решающего блока, входы которого соединены с выходами регистра команд решающего блока, выходы ключей второй группы решакщего блока соединены с информационными входам регистра коэффициента, регистра команд, регистра правой точки, первыми группами информационных входов регистра результата итерации и регистра левой точки решающего блока, выходы счетчика команд решакщего .

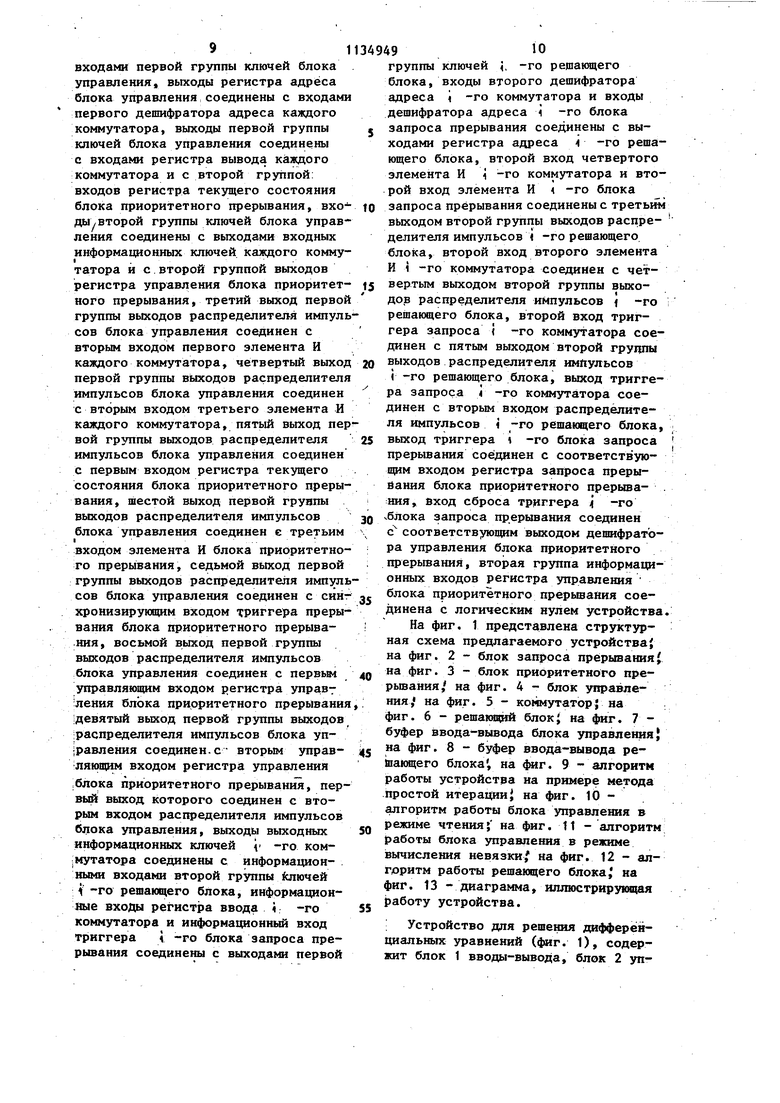

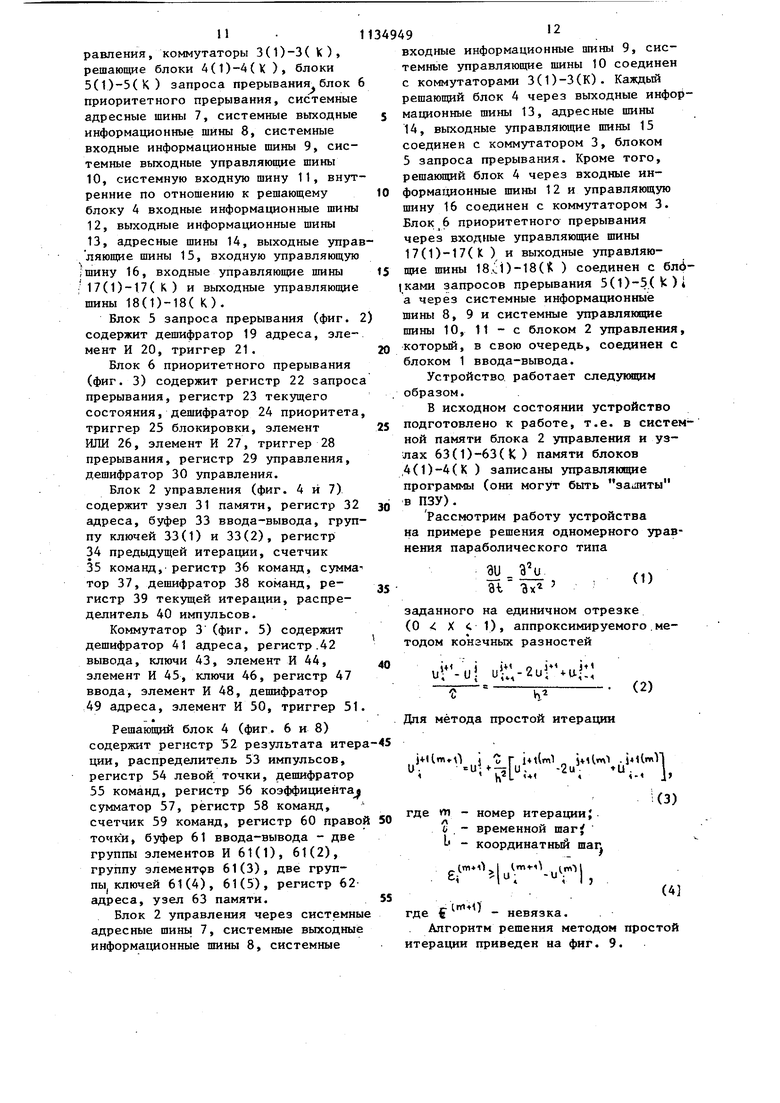

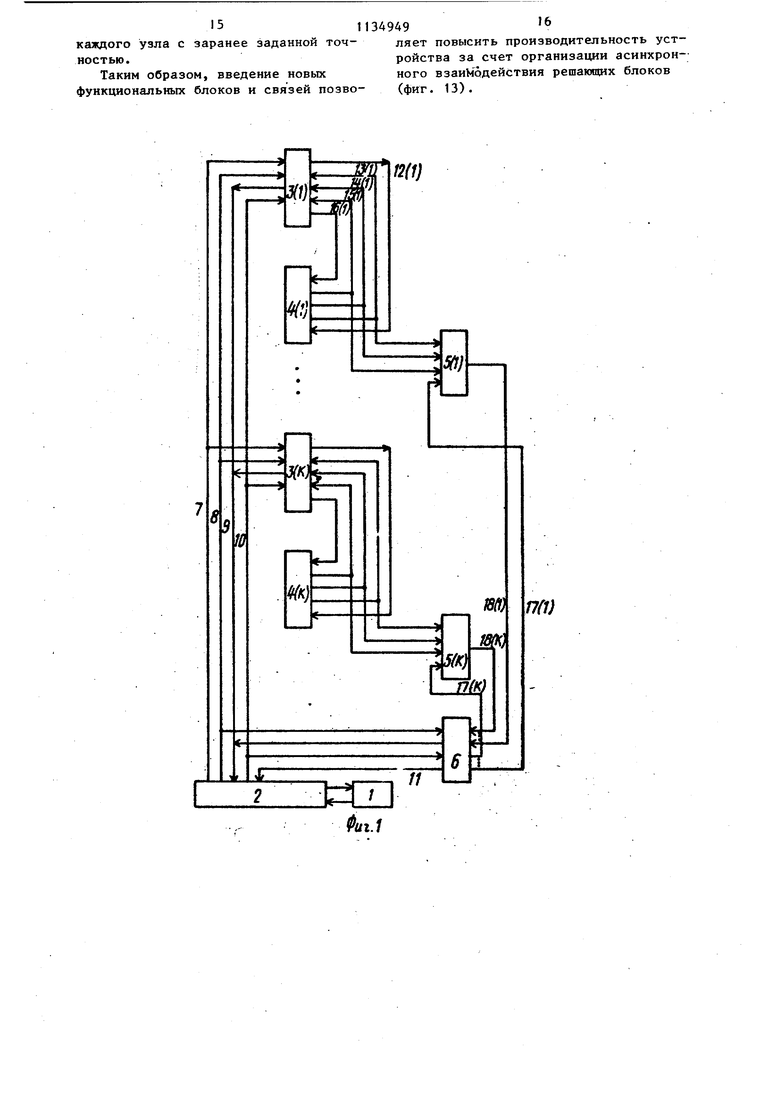

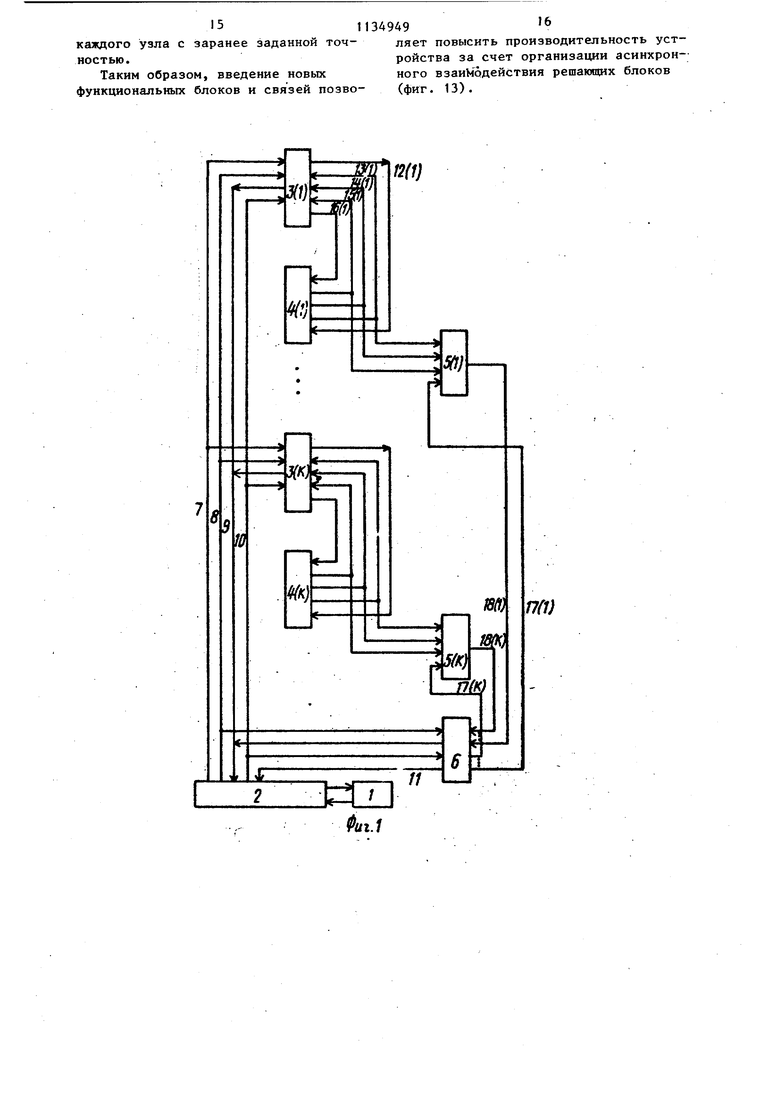

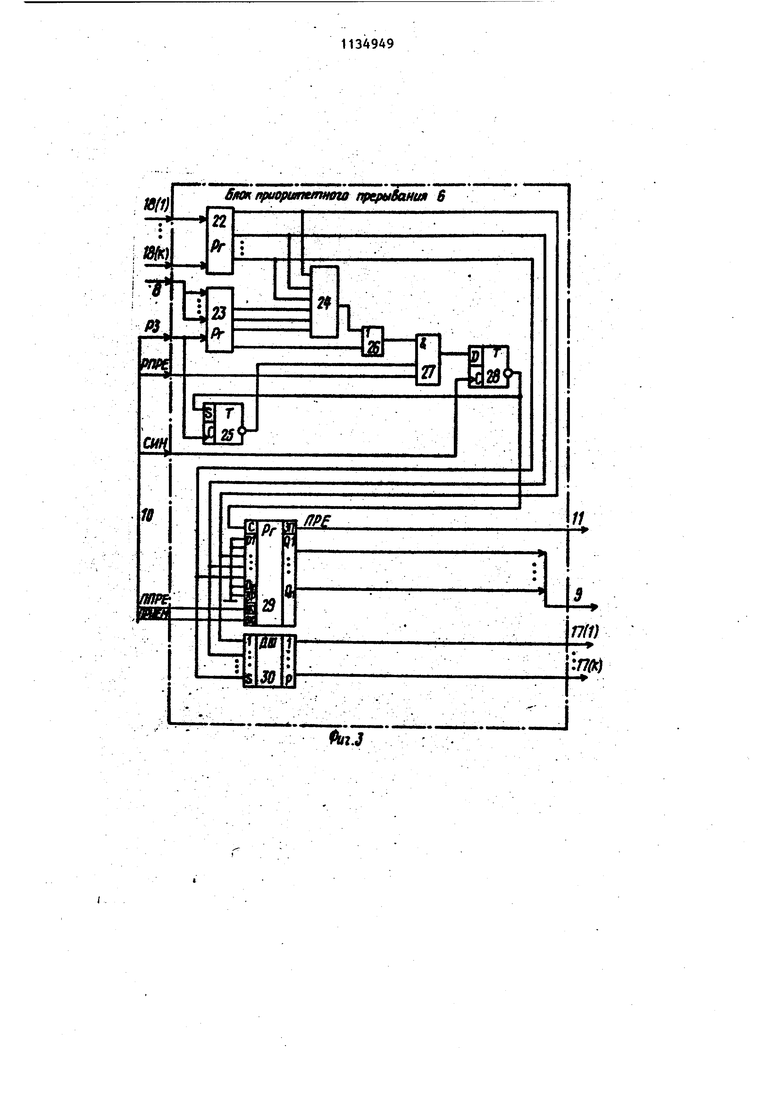

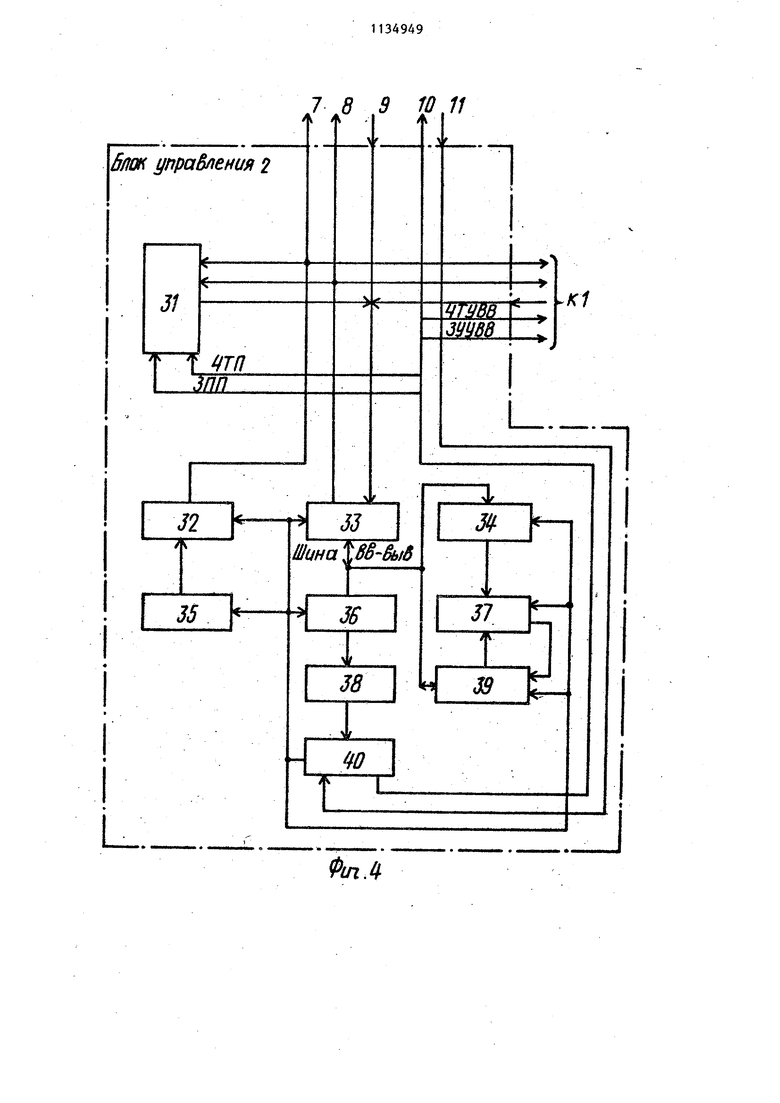

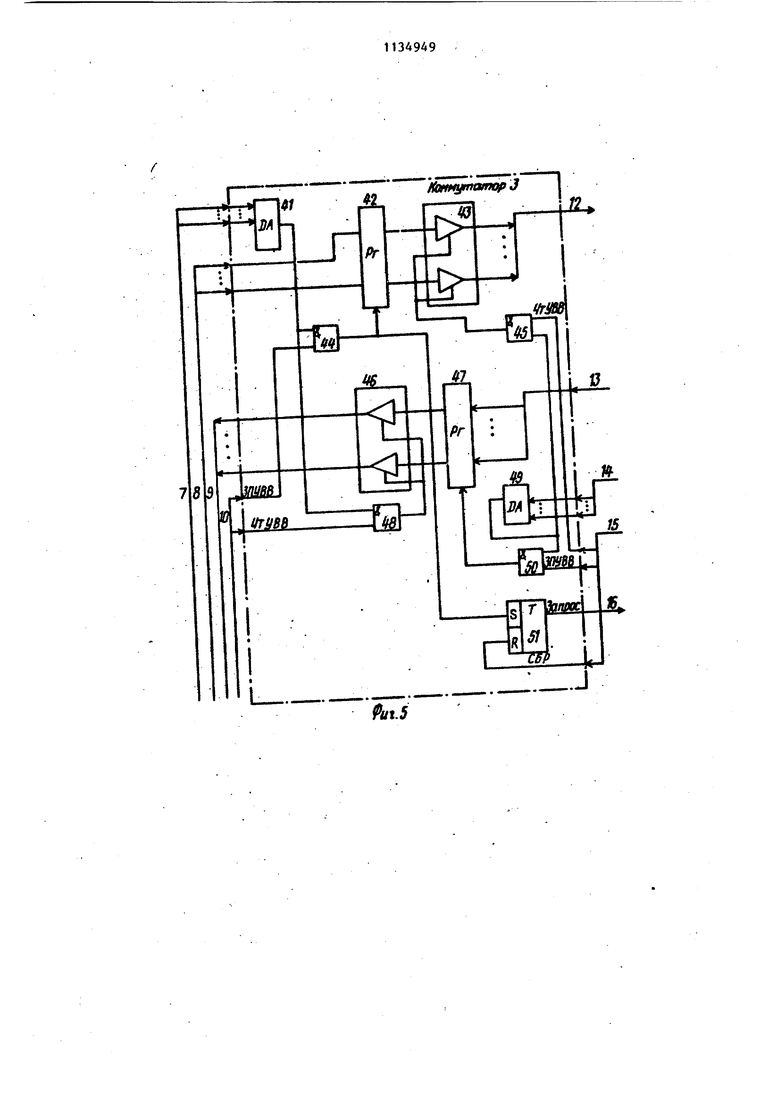

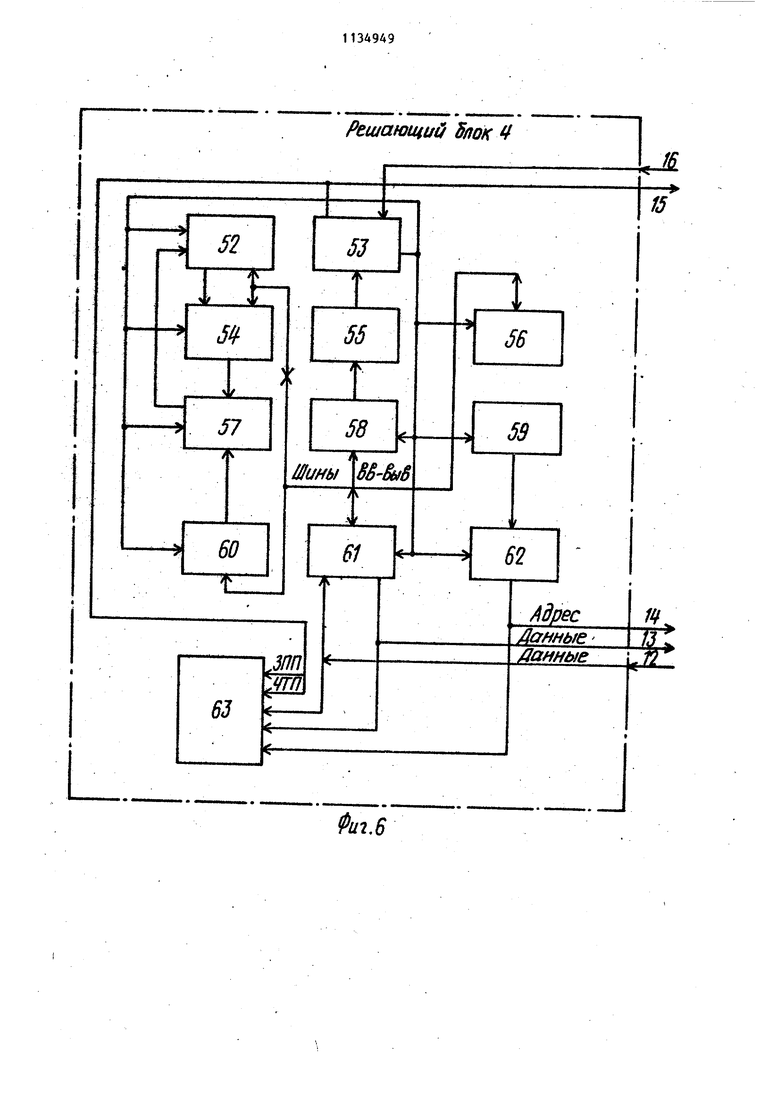

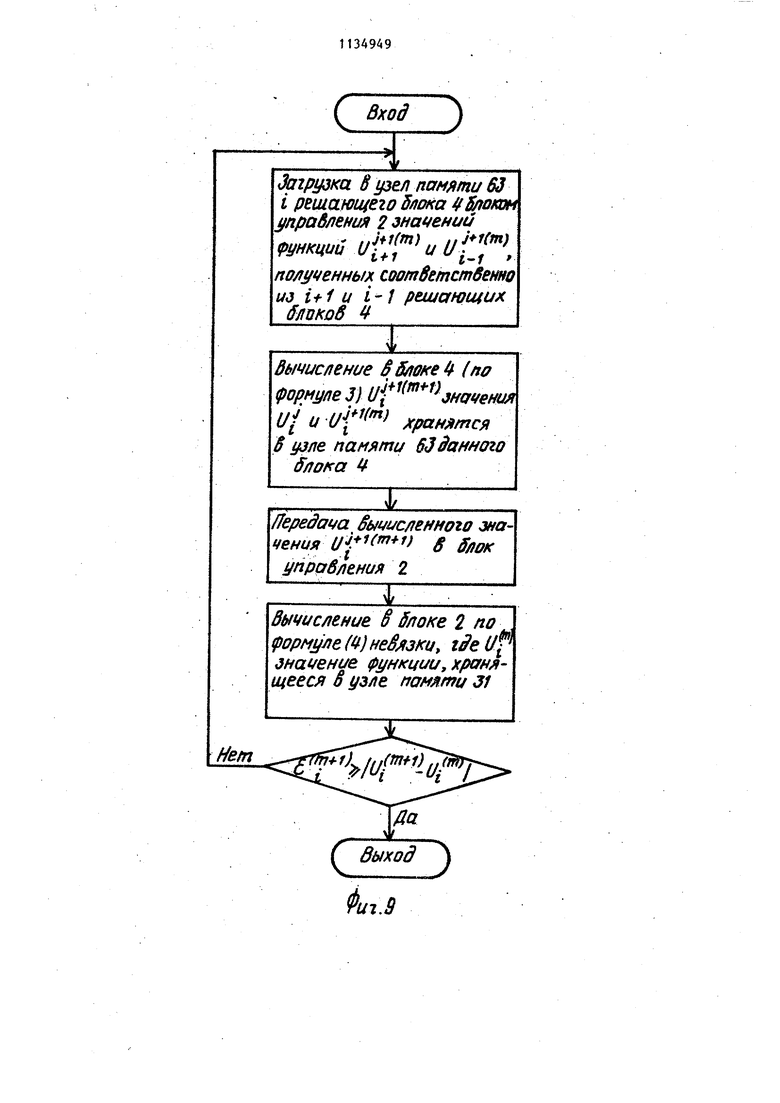

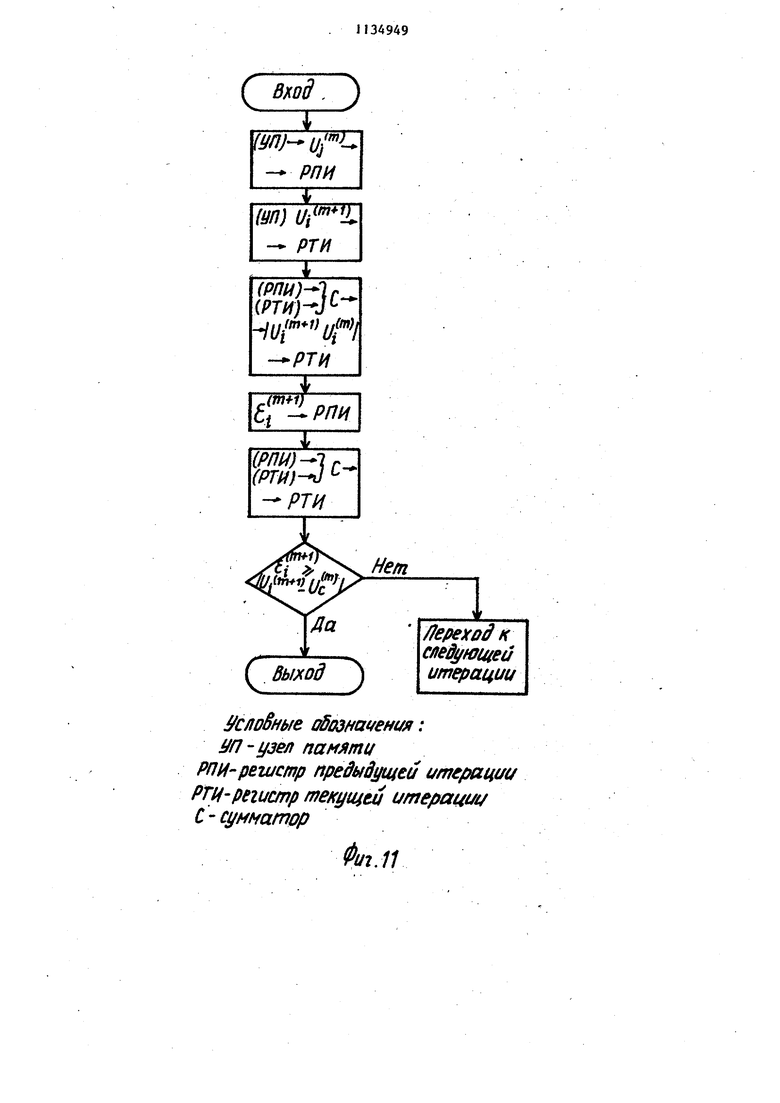

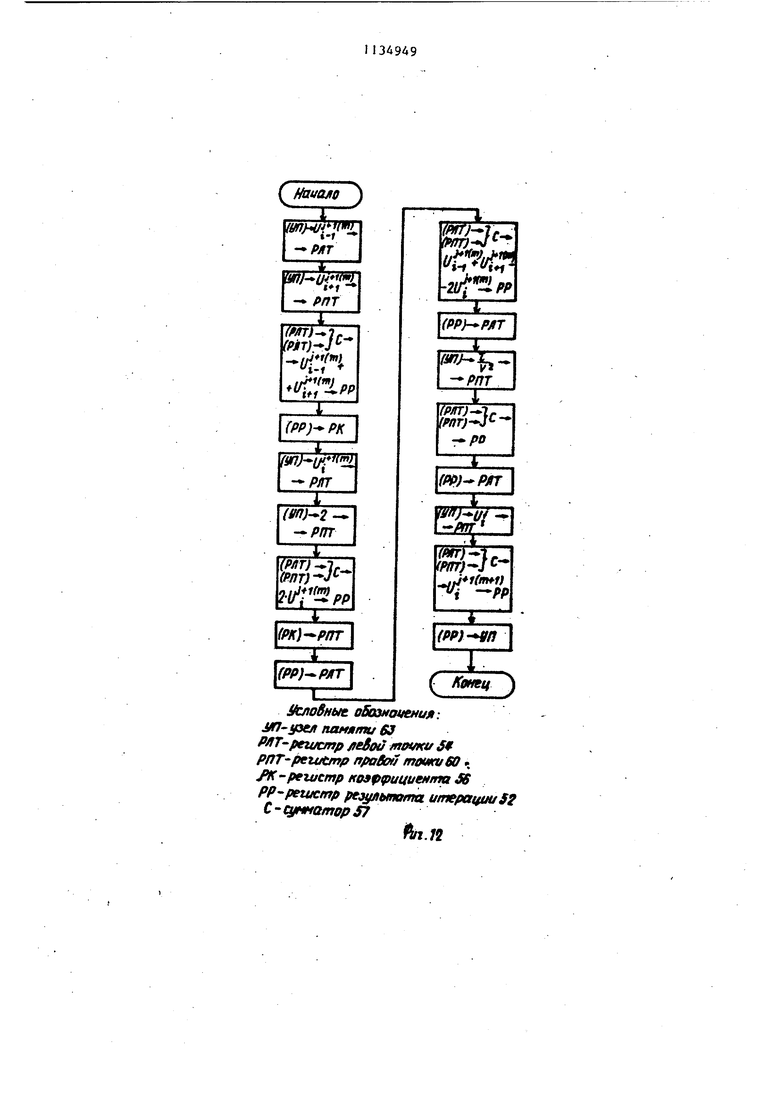

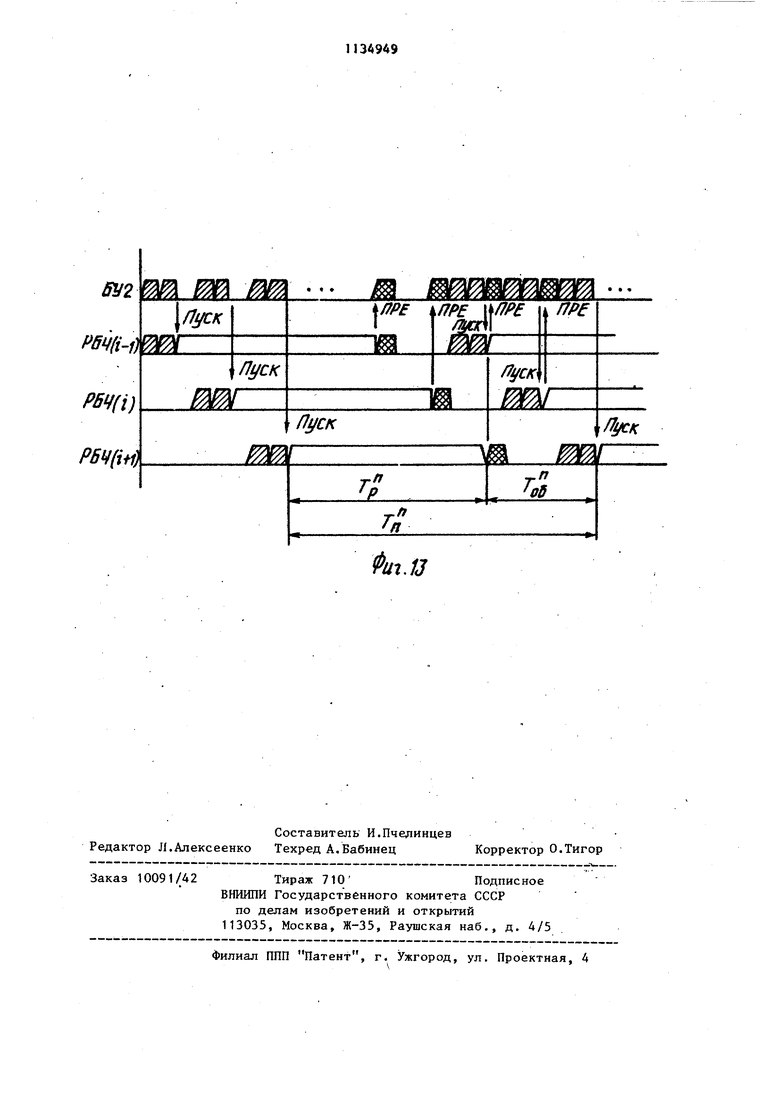

блока соединены с информационными входами регистра адреса решакяцего блока, выходы регистра правой точки решающего блока соединены с входами первого слагаемого сумматора решающего блока, входы второго слагаемого которого соединены с информционными входами регистра левой точНи решающего блока, выходы сумматора решающего блока соединены с второй группой информационных входов регистра результата итерации решающего блока, первая группа выходов которого соединена с второй группой информационш 1х входов регистра лево точки решающего блока, выходы регис ра коэффициента решающего блока соединены с вторыми входами элементов И первой группы решающего блока, вторая группа выходов регистра результата итерации решающего блока соединена с вторьми входами элементов И второй группы решающего блока выходы элементов И первой и второй Групп решающего блока соединены соответственно с первыми и вторыми входами элементов ИЛИ групп, выходы которых соединены с информационными входами ключей первой группы решающего блока, первый выход второ группы выходов распределителя импульсов решающего блока соединен с входом записи узла памяти решающего блока, второй выход второй группы выходов распределителя импульсов решающего блока соединен с входом чтения узла памяти решающего блока, информационные входы ключей второй группы/решакщего блока соединены С выходами узла памяти решающего блока, вькоды ключей первой группы решанлцего блока соединены с информционными входами узла памяти решающего блока, выходы регистра адреса решающего блока соединены, с адресными входами узла памяти решаницего блока, введены группа из К блоков запроса прерывания и блок приоритетного прерывания, причем каждый блок запроса прерывания содержит дешифратор адреса, элемент И, триг-; гер, выход дешифратора адреса блока запроса прерывания соединен с первым входом элемента И блока запроса прерывания, выход которого соединен с синхронизирующим входом триггера блока запроса прерывания, блок приоритетного прерывания с6держит регистр запроса прерывания. регистр текущего состояния, дешифра тор приоритета, триггер блокировки, элемент ИЛИ, элемент И, триггер прерывания, регистр управления, дешифратор управления, выходы регистра запроса прерываний блока приоритетного прерывания соединены с первой группой входов дешифратора приоритетов, с первой группой инфор ционных входов регистра управления и входами дешифратора управления блока приоритетного прерывания, пер группа выходов регистра текущего ,, состояния блока приоритетного преры вания соединена с второй группой входов дешифратора приоритета блока приоритетного прерывания, выход которого соединен с первым входом элемента И блока приоритетного прер вания, второй вход которого соедине с вторым выходом регистра текущего состояния блока приоритетного прерывания, выход триггера блокировки блока приоритетного прерывания соединен с первым входом элемента И блока приоритетного прерывания, вто рой вход которого соединен с выходом элемента ШТИ блока приоритетног прерывания,/ выход элемента И блока приоритетного прерывания соединен с информационным входом триггера прерывания блока приоритетного прер вания, выход которого соединен с входом триггера блокировки и с синхронизирующим входом регистра управ ления блока приоритетного, прерывани блок управления содержит две группы ключей, регистр предыдущей итерации сумматор, дешифратор команд, регист текущей итерации, распределитель импульсов, выходы регистра адреса блока управления соединены с адресньп-м входами узла памяти блока, упра ления, выходы первой группы ключей блока управления соединены с информ ционными входами узла памяти блока управления, информационные выходы которого соединены с информационными входами второй группы ключей, первый выход первой группы выходов распределителя импульсов блока управления соединен с входом записи узла памяти блока управления, второ выход первой группы выходов распределителя импульсов блока управления соединен с входом чтения узла памяти блока управления, первый выход второй группы выходов распределителя импульсов блока управления соединен с управляющим входом счетчика команд блока управления, второй выход второй группы выходов распределителя импульсов блока управления соединен с управляющим входом регистра адреса блока управления, третий выход второй группы выходов распределителя импульсов блока управления соединен с управляющими входами первой группы ключей блока управления, четвертый выход второй группы выходов распределителя импульсов блока управления соединен с управляющими входами .второй группы ключей блока управления, пятый выход второй группы выходов распределителя импульсов блока управления соединен с управлякяцим входом регистра команд блока управления, шестой выход второй группы выходов распределителя импульсов блока управления соединен с управляющим входом регистра предыдущей итерации блока управления, седьмой выход второй группы выходов распределителя импул сов блока управления соединен с управляющим входом сумматора блока управления, восьмой выход второй группы выходов распределителя импульсов блока управления соединен с управляющим входом регистра текущей итерации блока управления, первая группа входов распределителя импульсов блока управления соединена с выходами дешифратора команд блока управления, входы которого соединены с выходами регистра комаид блока управления, выходы второй группы ключей блока управления соединега с входами регистра команд, регистра предыдущей итерации, первой группой входов регистра текущей итерации блока управления, выходы счетчика команд блока управления соединены с входами регистра адреса блока управления, выходы регистра предыдущей итерации блока згправления соединены с входами первого слагаемого сумматора блока управления, входы второго слагаемого которого соединены с первой группой выходов регистр ра текущей итерации блока управления, выходы сумматора блока управления . соединены с второй группой входов регистра текущей итерации блока управления, вторая группа выходов которого соединена с информационными 9 входами первой группы ключей блока управления, выходы регистра адреса блока управления соединены с входами первого дешифратора адреса каждого коммутатора, выходы первой группы ключей блока управления соединены с входами регистра вывода каяадого коммутатора и с второй группой: входов регистра текущего состояния блока приоритетного прерывания, входы/второй группы ключей блока управления соединены с выходами входных информационных ключей казкдого коммутатора и с второй группой выходов регистра управления блока приоритетного прерывания, третий выход первой группы выходов распределителя импуль сов блока управления соединен с вторым входом первого элемента И каждого коммутатора, четвертый выход первой группы выходов распределителя импульсов блока управления соединен с вторым входом третьего элемента И каждого коммутатора, пятый выход пер вой группы выходов распределителя импульсов блока управления соединен с первым входом регистра текущего состояния блока приоритетного прерывания, шестой выход первой грунпы выходов распределителя импульсов блока управления соединен е третьим I . .. входом элемента И блока приоритетного прерывания, седьмой выход первой группы выходов распределителя импуль сов блока управления соединен с синг хронизирующим входом -триггера прерывания блока приоритетного прерыва.ния, восьмой выход первой группы выходов распределителя импульсов .блока управления соединен с первьм управляющим входом регистра управу ления блока приоритетного прерывания |девятый выход первой группы выходов распределителя импульсов блока уп|равления соединен.с- вторым управляющим входом регистра управления ,блока приоритетного прерывания, первый выход которого соединен с вторым входом распределителя импульсов блока управления, выходы выходных информационных ключей v -го ком.мутатора соединены с информационными входами второй группы Ключей I -го решающего блока, информационные входы регистра ввода i -го коммутатора и информационный вход триггера -го блока запроса прерывания соединены с выходами первой 910 группы ключей . -го решающего блока, входы второго дешифратора адреса -го коммутатора и входы дешифратора адреса i -го блока запроса прерывания соединены с выходами регистра адреса -го решающего блока, второй вход четвертого элемента И i -го коммутатора и второй вход элемента И -го блока запроса прерывания соединены с третыш выходом второй группы выходов распределителя импульсов -го решающего блока, второй вход второго элемента И 1 -го коммутатора соединен с четвертым выходом второй группы выходов распределителя импульсов i -го ; решающего блока, второй вход триггера запроса i -го коммутатора соединен с пятым выходом второй грудпы выходов распределителя импульсов ( -го решающего блока, выход триггера запроса -го коммутатора соединен с вторым входом распределителя импульсов 1 -го решающего блока, ; выход триггера -го блока запроса прерьшания соединен с соответствующим входом регистра запроса прерывания блока приоритетного прерыва- . ния, вход сброса триггера jj -го яблока запроса прерывания соединен с соответствующим выходом дешифратора управления блока приоритетного прерывания, вторая группа информационных входов регистра управления блока приоритетного прерывания соединена с логическим нулем устройства. На фиг, 1 предста,влена структурная схема предлагаемого устройства} на фиг. 2 - блок запроса прерывания( на фиг. 3 - блок приоритетного прерьгаания/ на фиг. 4 - блок управления,« на фиг. 5 - коммутаторJ на фиг. 6 - решакш ий блок на фиг. 7 буфер ввода-вывода блока управления{ на фиг. 8 - буфер ввода-вывода решающего блока , на фиг. 9 - алгоритм работы устройства на примере метода простой итерацииi на фиг. 10 алгоритм работы блока управления в режиме чтения; на фиг. 11 - алгоритм работы блока управления в режиме вычисления невязки/ на фиг. 12 - алгоритм работы решающего блока на фиг. 13 - диаграмма, шшюстрирукицая работу устройства. ; Устройство для решения дифференциальных уравнений (фиг. 1), содержит блок 1 вводы-вывода, блок 2 управления, коммутаторы 3(1)-3( К), решающие блоки 4(1)-4(Х ), блоки 5(1)-5(К) запроса прерывания, блок приоритетного прерывания, системные адресные шины 7, системные выходные информационные шины 8, системные входные информационные шины 9, системные выходные управляющие шины 10, системную входную шину 11, внут ренние по отношению к решающему блоку 4 входные информационные шины 12,выходные информационные шины 13,адресные шины 14, выходные упра ляющие шины 15, входную управляющую ;шину 16, входные управляющие шины :Ч7(1)-17( К) и выходные управляющие шины 18(1)-18( К). Блок 5 запроса прерывания (фиг. содержит дешифратор 19 адреса, элемент И 20, триггер 21. Блок 6 приоритетного прерывания (фиг. 3) содержит регистр 22 запрос прерывания, регистр 23 текущего состояния, дешифратор 24 приоритета триггер 25 блокировки, элемент ИЛИ 26, элемент И 27, триггер 28 прерывания, регистр 29 управления, дешифратор 30 управления. Блок 2 управления (фиг. 4 и 7) содержит узел 31 памяти, регистр 32 адреса, буфер 33 ввода-вывода, груп пу ключей 33(1) и 33(2), регистр 34предьщущей итерации, счетчик 35команд, регистр 36 команд, сумма тор 37, дешифратор 38 команд, регистр 39 текущей итерации, распределитель 40 импульсов. Коммутатор 3 (фиг. 5) содержит дешифратор 41 адреса, регистр.42 вывода, ключи 43, элемент И 44, элемент И 45, ключи 46, регистр 47 ввода, элемент И 48, дешифратор 49 адреса, элемент И 50, триггер 51 Решающий блок 4 (фиг. 6 и 8) содержит регистр 52 результата итер ции, распределитель 53 импульсов, регистр 54 левой точки, дешифратор 55 команд, регистр 56 коэффициента сумматор 57, регистр 58 команд, счетчик 59 команд, регистр 60 право точки, буфер 61 ввода-вывода - две группы элементов И 61(1), 61(2), группу элемент9в 61(3), две группы ключей 61(4), 61(5), регистр 62 адреса, узел 63 памяти. Блок 2 управления через системны адресные шины 7, системные выходные информационные шины 8, системные входные информационные пганы 9, системные управляющие шины 10 соединен с коммутаторами 3(1)-3(К). Каждый решаю1ций блок 4 через выходные информационные шины 13, адресные шины 14, выходные управляющие шины 15 соединен с коммутатором 3, блоком 5 запроса прерывания. Кроме того, решающий блок 4 через входные информационные шины 12 и управляющую шину 16 соединен с коммутатором 3. Блок 6 приоритетного прерывания через входные управляющие шины 17(1)-17(k) и выходные управляющие шины 18х1)-18( ) соединен с блЬками запросов прерывания 5(1)-5(k)i а через системные информационные шины 8, 9 и системные управляющие шины 10, 11 - с блоком 2 управления, который, в свою очередь, соединен с блоком 1 ввода-вывода. Устройство работает следукщим образом. В исходном состоянии устройство подготовлено к работе, т.е. в системной памяти блока 2 управления и узлах 63(1)-63(К) памяти блоков ,4(1)-4(К ) записаны управляюпще программы (они могут быть в ПЗУ). рассмотрим работу устройства на примере решения одномерного уравнения параболического типа 3U Bu 81 Зх заданного на единичном отрезке (О 4 X . 1), аппроксимируемого .методом конзчных разностей tt J-tl uu,-2ui Для метода простой итерации t(m1 „ Г, и , -2, -номер итерации; -временной шаг -координатный шаг. (. I lm+-i невязка. Алгоритм решения методом простой итерации приведен на фиг. 9. 3 Решение задачи включают следующие этапыJ загрузку исходньк данных (коэффициентов, значений граничных условий и т.д.), из блока 1 вводавывода в узел 31 памяти блока 2 управленияi решение исходного уравнения в решающих блоках 4(1)-4(1с ) под управлением блока 2J выдачу полу ченного результата из узла 31 памяти блока 2 управления в блок 1 ввода-вывода. Блок 2 управления вырабатывает по шине 7 адрес коммутатора 3(1) первого решающего блока, по управляющей шине 10 - сигнал Запись УВВ (ЗП УВВ), ПОкоторому слово из узла 31 памяти блока 2 управления по информационной щине 8 записывается в регистр 42 вывода (фиг. 5). При этом в триггере 51 устанавливается 1, которая в виде запроса по шине 16 поступает в решающий блок 4(1). По сигналу с шины 16 решающий блок 4(1) обращается к комму татору 3(1) как к внешнему устройству, считывает информацию с регист ра 42 вывода через ключи 43 по шине 12(1) в узел 63(1) памяти и по шине 15 (сигнал СВР) сбрасывает триггер 51 в исходное состояние. Аналогично вся исходная информация (коэффициенты, значения граничных условий) загружается в узел 63(1) памяти пер вого решающего блока 4(1), которыйпоследней командой передаваемого массива запускается навыполнение .; первой итерации в соответствии с формулой (3). Затем блок 2 управления перекачивается через коммутатор 3(2) к второму решающему блоку 4(2), загружает исходной информацией узел 63(2) памяти и передает управление решающему блоку 4(2), которьш начинает выполнять собствен ную программу по формуле (3), а в это время блок 2 управления переклю чается к следующему блоку 4 и, таки образом, все 1( решающих блоков 4 со смещением во времени параллельно выполняют программы первого итерационного цикла (алгоритм работы решающего устройства блока 4 приведен на фиг. 12). Взаимодействие блока 2 управления с блоками 4(1) и 4(К ) осуществляется синхронно, т.е. по принципу запрос-ответ. После того, как выполнено решение в любом из решающих блоков 4 в первом 49IA итерационном цикле, решающий блок 4 сообщает об этом блоку 2 управления. Для этого решающий блок 4 записывает результат в регистр 47 коммутатора 3 и выставляет на шинах 14 адрес блока 5 запроса прерывания, на шинах 13 - соответствующий блоку 5 запроса прерьгеация код и по управляющему сигналу ЗП УВВ (шина 15) через дешифратор 19 адреса (фиг. 2) и элемент И 20 устанавливает в триггере 21 запрос прерывания, который по шине 18 передается блоку 6 приоритетного прерывания. По запросу прерывания в блоке 6 приоритетного прерывания формируется код, соответствующий данному решающему блоку 4, тот код по шине 9 передается в блок 2 управления, который подключается через соответствующий коммутатор 3 к соответствующему блоку 4 и по сигналу ЧТ УВВ (шина 10) через ключи 46 и информационные шины 9 считывает результат первой итерации из регистра 47 ввода в узел 31 памяти. Блок 6 формирует по шине 17 сигнал, который сбрасывает триггер 121 блока 5 в исходное состояние. Более подробный алгоритм работы ;блока 2 управления в режиме чтения из решающего блока 4 приведен на фиг. 10. i Далее, таким же образом, принимаются полученные на первой итерации значения остальных блоков 4 в бу- . ферную область памяти блока 2 управления, причем управляющая программа блока 2, недожидаясь окончания вычислений во всех блоках 4, отслеживает окончание работы соседних блоков 4, и, как только результат оказывается в буфершэй области, осуществляет перезагрузку полученной информации в освободившиеся решающие блоки 4 для выполнения следующей итерации, в то время как остальные блоки 4 заканчивают текущую итерацию. Таким образом, последовательно оставшиеся блоки 4 перехо1 вьшолнению следующей интерации. Каждый раз перед переходом к еледующей итерации блок 2 управления в соответствии с алгоритмом работы, приведенным на фиг. 11, и формулой (4) вычисляет невязку , Описанный итеративный процесс повторяется до тех пор, пока не будут получены значения функции для

151134949

каждого узла с заранее заданной точ- ляет повысить производительность устностью.ройства за счет организации асинхронТаким образом, введение новых ного взаимодействия решающих блоков функциональных блоков и связей позво- (фиг. 13).

WZJ

f6 Ш13

Фиг.2

В/юк lyui afifawno 1у еры8ания 6

PttiJ

.j

7 8 9 W

k k

6m t/праёления 2

J/

Т

J/Z/L

JJ

J2

. M-ebtB

Й///а

Jcf

36

J(

L.

ФигЛ

//

f

K1

У7:у5

jyf/зв

t.

nl

c

J7

ч

JC

a

Решающие/ 5/1ок

Шина обода-быбода

Шины Ввода-бывоВа Фиг.

ода61

I

V

I

Фиг.В

( Вход 3

.. .... - - Загрудка 8 t/зел памяти 6J i решающего Ьпока if Споком траблкния 2

- i,(fn) ,(in) ({функции U{ uUl V

полувоенных соответс/пбенно uj i-f-1 и / - / решающих бпикоб

Вычисление §5/10ке (по формуле 3) мочения Ul и хранятся f узле памяти 6дДанного

f/epedat a вы исленного значения 8 $лок у про6лени я 2

Вы исление § 5локе 2 по

формуле ()не8язки, dHat/ение функции хранящееся 8 узле памяти 31

Нет

1

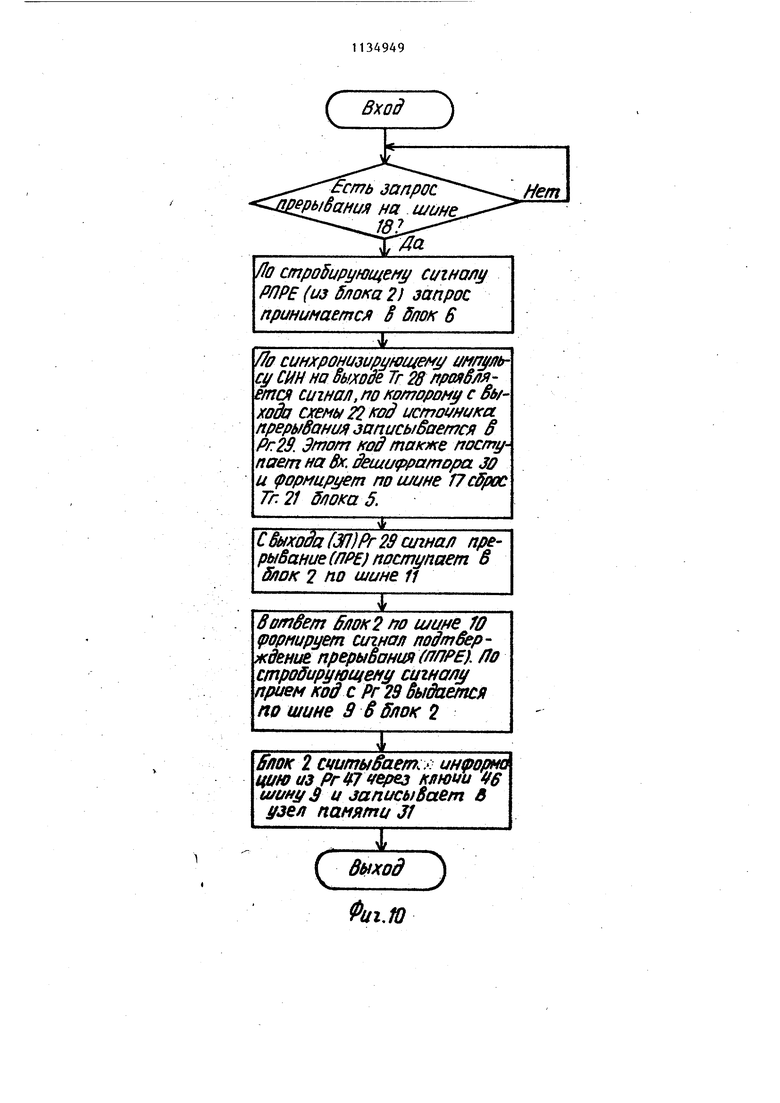

Свход J

сть запрос ь/ёания на шине

ffo cmpo5upyHiu4efft/ ct/гналу РПРЕ (из блока 21 запрос принимается S SnoK 6

ffo cuHXpOHUdupyfOtueftfi/ i/fifry/nr ci/ Ш/ на йьтде Тг 28 проявляется сигнал, по которону с Вь/хода схемы 22 код источника прерывания записывается о Рл29. Этот код поступает на 8х, deututffpamopa JO и (формирует по и/с/не Г7с5рос Тг.21 5лока 5.

С Выхода ()Рг 29 сигнал прерыВание(ПРЕ) поступает В 5пок 2 по шине 11

S ответ блок 2 по шине W (рорнирует сигнал по тбержденив прерывания (fJfJPE). По cmpoSupytoutefft/ cuwant/ прием код с Рг 29 Выдается по шине 9 В блок 2

/ffOfc 2 cwmbiBaem..; tit/№t/3 ключи 6 u/wy 3 tf JanucbiBaem д узел памяти J1

( dixod

Нет 18 Да Фи1,Ю

с лобные обозначения: УП -узел памяти Pnn-pewcfnp предыдущей итераци(/

РТИ-регистр текущей итерац1/1/ ССум атор

Фиг.11

Условные oSoMoveHujt:

J/Пузел памяти 63

РЯТ--регистр jieBoa /aovKt/ 69

Pftr-регистр правой moufo/ Sf

регистр KO9f y uiiiiemna JS

PP регистр ре ьяюта u/nepattoufg

CtyHMumopSJ

ЙП./2

Пуск

Пуск

mfi)L

РВЩщ

ш

ffP kffPE ЛР

kf7pe

Фиг.13

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Вычислительная система для решения дифференциальных уравнений | 1975 |

|

SU620980A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Вычислительная система для решения дифференциальных уравнений | 1975 |

|

SU565299A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1985-01-15—Публикация

1982-11-04—Подача