Изобретение относится к автоматике и вычислительной технике и может быть использовано при проектировании вычислительных системо .

Целью изобретения является повышение быстродействия.

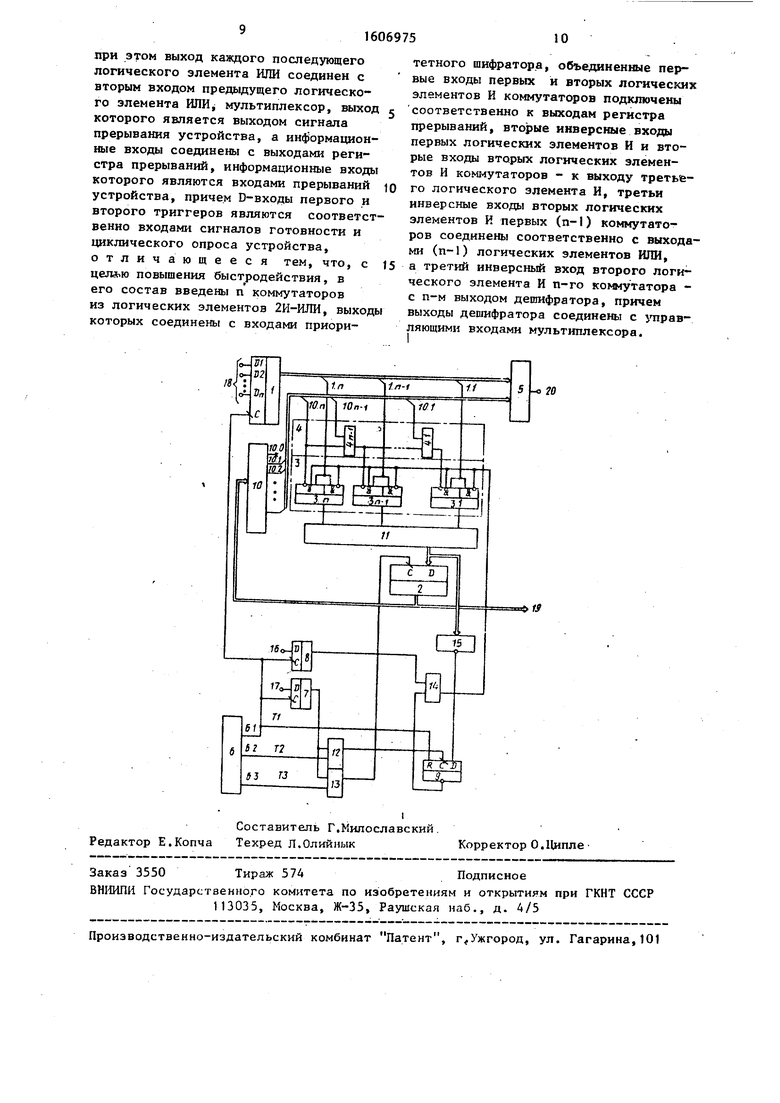

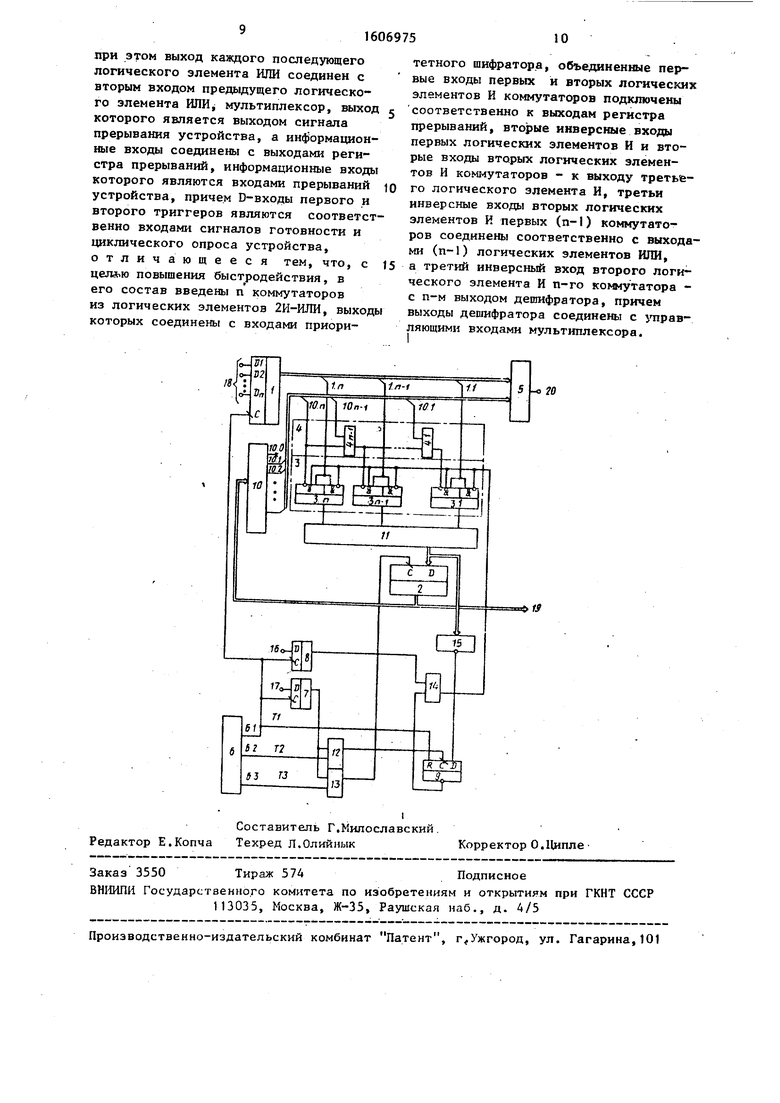

На чертеже приведена функциональная схема устройства для обработки прерываний.

Устройство содержит регистр 1 прерываний, регистр 2 кода прерывающего устройства, п коммутаторов 3«1-3.п, (п-1) логических элементов 4.1-4.(ii-l) ИЛИ, мультиплексор 5, генератор 6 тактовых импульсов, первый 7, второй 8 ,и третий 9 триггеры, дешифратор 10, приоритетный шифратор 11, первый 12, второй 13 и третий 14 логические элементы И, логический элемент ИЛИ-НЕ 15, вход 16 сигнала цикличес- кого опроса, вход 17 сигнала готов- устройства, входы 18 прерываний устройства, группу выходов 19

устройства кода периферийного устройства и выход 20 сигнала прерывания устройства с

Регистр 1 предназначен для приема и хранения сигналов прерываний от периферийных устройств. Каждый разряд регистра закреплен за одним устройством. Сигналы прерываний на устройство поступают по входам 18. Регистр 2 служит для хранения кода периферийного устройства, требующего прерывания и имеющего в данный момент выс- .ший по сравнению с другими периферийными устройствами приоритет (в режиме приоритетного опроса), либо обслуживаемого в текущий момент времени (в режиме циклического опроса).

Коммутаторы 3 осуществляют передачу сигналов прерываний с выходов регистра 1 прерываний на входы приоритетного шифратора 11 в режимах циклического опроса и прерываний по приоритету., В зависимости от комбинаций

(Л

Од

о9д

СО

чЗ

ел

гправЛяюидах сигналов на входах первого и второго логических элементов И коммутаторов они осуществляют либо передачу, либо маскирование входных сигналов. Логические элементы ИЛИ 4 служат для фррмирования управляющих сигналов на коммутаторе 3, маскирующих прохождение через них сигналов прерываний в режиме циклического оп- роса о.

Мультиплексор 5 передает сигнал прерывания от регистра 1 прерываний на выход 20 устройства

Генератор 6 тактовых импульсов .формирует на первом, втором и тре- тьем выходах три последовательности тактовых импульсов с соответствующими задержками , QZ т i относительно друг друга.

Первый триггер 7 предназначен для управления устройством при готовности процессора к обработке прерываний Сигнал готовности процессора для обработки преШ11ваний поступает на вход 17 устройства.

Второй триггер 8 служит для задания режима работы устройства. В режиме циклического опроса прерываний второй триггер 8 находится в единич- ном состоянии, при обработке прерываний по приоритету - в нулевом состоянии.

Третий триггер 9 для управления работой коммутаторов 3 в режим циклического опроса.

Дешифратор 10 предназначен для .формирования унитарного кода периферийного устройства, требующего прерывания, и управления коммутаторами 3 в различных режимах работы устройства.

Приоритетный шифратор 11 служит для формирования кода периферийного устройства, требующего прерывания и имеющего в текущий момент времени наивысший приоритет.

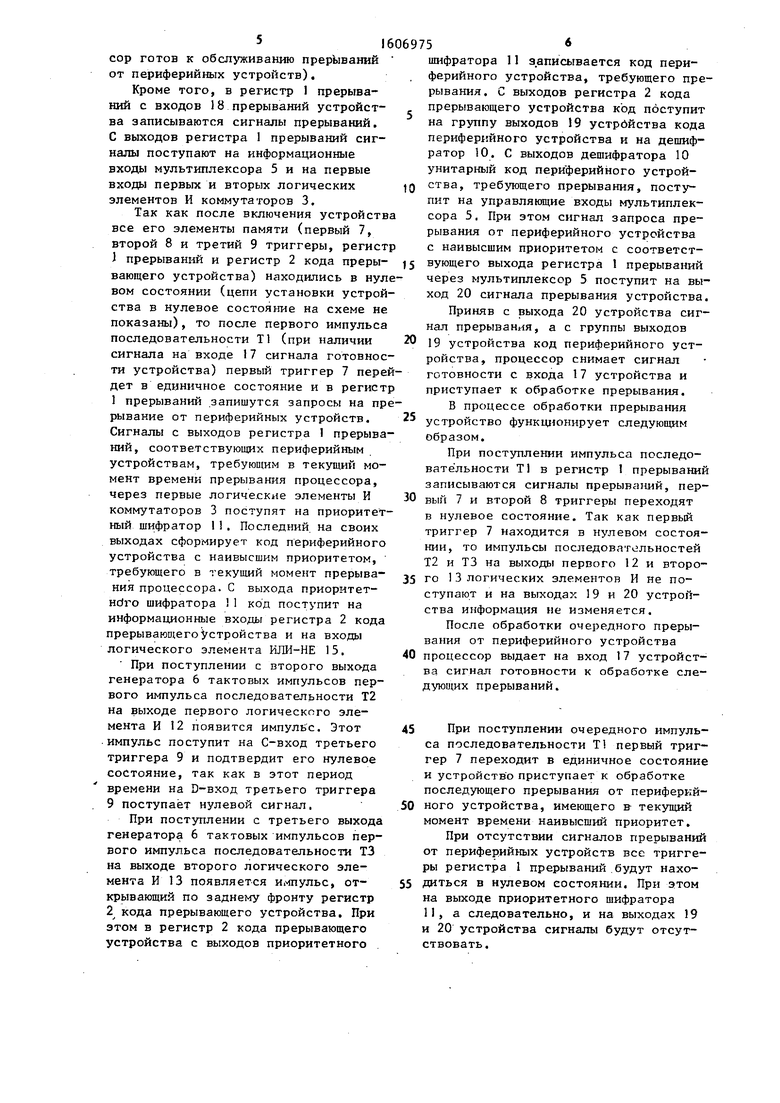

Дпя случая таблица соответст ВИЯ, описывающая функционирование приоритетного шифратора 11, имеет следующий вид:

,-- Продолжение таблицы

Входные сигналы Выходные сигналы

5

5 0

зО

35

дО

45

Q

Первый 12, второй 13 и третий 14 логические элементы И и логический элемент ИЛИ-НЕ 15 и обусловленные ими связи предназначены для формирования управляющих сигналов на регистр 2 кода прерывающего устройства, третий триггер 9 и коммутаторы 3.

На вход 16 сигнала циклического опроса устройства от процессора, обрабатывающего прерывание, в режиме циклического опроса периферийных устройств постоянно поступает сигнал. В режиме обслуживания процессором прерываний по приоритету сигнал на входе 16 отсутствует.

На входе 17 сигнала готовности устройства присутствует сигнал при готовности процессора обспуживать прерывания и отсутствует в противном случае.

На входы 1В прерываний от периферийных устройств поступают сигналы прерываний. Каждомупериферийному устройству в регистре 1 прерываний соответствует один триггер.

Устройство для обработки прерываний может функционировать в двух жимах: приоритетного опроса; циклического опроса.

В режиме приоритетного опроса на входе 16 сигнала циклического опроса устройства сигнал отсутствует. Генератор 6 тактовых импульсов формирует на первом, втором и третьем выходах последовательности импульсов Т1, Т2 и ТЗ. По первому импульсу последовательности Т1 подтверждается нулевое состояние второго триггера 8, а первый триггер 7 перейдет в единичное состояние, так как на D-вход последнего с входа 17 сигйала готовности устройства поступает сигнал (процесшифратора 11 записывается код периферийного устройства, требующего прерывания. С выходов регистра 2 кода прерывающего устройства код поступит на группу выходов 19 устрбйства кода периферийного устройства и на дешифратор 0. С выходов дешифратора 10 унитарный код периферийного устрой- д ства, требующего прерывания, посту пит на управляющие входы мультиплексора 5, При этом сигнал запроса прерывания от периферийного устройства с наивысшим приоритетом с соответстсор готов к обслуживанию прерываний от периферийных устройств).

Кроме того, в регистр 1 прерываний с входов 18 прерываний устройства записываются сигналы прерываний. С выходов регистра прерываний сигналы поступают на информационные входы мультиплексора 5 и на первые входы первых и вторых логических элементов И коммутаторов 3.

Так как после включения устройства все его элементы памяти (первый 7, второй 8 и третий 9 триггеры, регистр

J прерываний и регистр 2 кода преры- ,5 вующего выхода регистра 1 прерываний вающего устройства) находились в нуле- через мультиплексор 5 поступит на вы- вом состоянии (цепи установки устрой- ход 20 сигнала прерывания устройства, ства в нулевое состояние на схеме не Приняв с выхода 20 устройства сиг- показаны), то после первого импульса последовательности Т1 (при наличии 20 сигнала на входе 17 сигнала готовности устройства) первый триггер 7 перейдет в единичное состояние и в регистр 1 прерываний запишутся запросы на прерывание от периферийных устройств. 25 устройство функционирует следующим Сигналы с выходов регистра 1 прерыва- образом. НИИ, соответствующих периферийным устройствам, требуюишм в текущий момент времени прерывания процессора, через первые логические элементы И коммутаторов 3 поступят на приоритетный шифратор 11. Последний на своих выходах сформирует код периферийного устройства с наивысшим приоритетом, требующего в текущий момент прерывания процессора. С выхода приоритетнал прерывания, а с группы выходов 19 устройства код периферийного устройства, процессор снимает сигнал готовности с входа 17 устройства и приступает к обработке прерывания. В процессе обработки прерывания

30

Hdro шифратора 11 код поступит на информационные входы регистра 2 кода прерывающегоУстройства и на входы логического элемента Ш1И-НЕ 15.

При поступлении с второго выхо-да генератора 6 тактовых импульсов первого импульса последовательности Т2 на выходе первого логического элемента И 12 появится импульс. Этот импульс поступит на С-вход третьего триггера 9 и подтвердит его кулевое состояние, так как в этот период времени на D-вход третьего триггера 9 поступает нулевой сигнал.

При поступлении с третьего выхода генератора 6 тактовых импульсов первого импульса последовательности ТЗ на выходе второго логического эле- меита И 13 появляется и.vlпyльc, открывающий по заднему фронту регистр 2 кода прерывающего устройства. При этом в регистр 2 кода прерывающего устройства с выходов приоритетного

При поступлении импульса последовательности Т1 в регистр 1 прерываний записываются сигналы прерываний, первый 7 и второй 8 триггеры переходят в нулевое состояние. Так как первый триггер 7 находится в нулевом состоянии, то импульсы последовательностей Т2 и ТЗ на выходы первого 12 и второ- 35 го 13 логических элементов И не поступают и на выходах 19 и 20 устройства информация не изменяется.

После обработки очередного прерывания от периферийного устройства 40 процессор выдает на вход 17 устройства сигнал готовности к обработке следующих прерываний.

45 При поступлении очередного импульса последовательности Т первый триггер 7 переходит в единичное состояние и устройство приступает к обработке последующего прерывания от периферий50 ного устройства, имеющего в текущий момент времени наивысший приоритет.

При отсутствии сигналов прерываний от периферийных устройств все триггеры регистра 1 прерываний.будут нахо55 диться в нулевом состоянии. При этом на выходе приоритетного шифратора II, а следовательно, и на выходах 19 и 20 устройства сигналы будут отсутствовать.

1606975

шифратора 11 записывается код периферийного устройства, требующего прерывания. С выходов регистра 2 кода прерывающего устройства код поступит на группу выходов 19 устрбйства кода периферийного устройства и на дешифратор 0. С выходов дешифратора 10 унитарный код периферийного устрой- ства, требующего прерывания, посту пит на управляющие входы мультиплексора 5, При этом сигнал запроса прерывания от периферийного устройства с наивысшим приоритетом с соответствующего выхода регистра 1 прерываний через мультиплексор 5 поступит на вы- ход 20 сигнала прерывания устройства, Приняв с выхода 20 устройства сиг- устройство функционирует следующим образом.

вующего выхода регистра 1 прерываний через мультиплексор 5 поступит на вы- ход 20 сигнала прерывания устройства, Приняв с выхода 20 устройства сиг- устройство функционирует следующим образом.

нал прерывания, а с группы выходов 19 устройства код периферийного устройства, процессор снимает сигнал готовности с входа 17 устройства и приступает к обработке прерывания. В процессе обработки прерывания

,5 вующего выхода регистра 1 прерываний через мультиплексор 5 поступит на вы- ход 20 сигнала прерывания устройства, Приняв с выхода 20 устройства сиг- 20 25 устройство функционирует следующим образом.

30

При поступлении импульса последовательности Т1 в регистр 1 прерываний записываются сигналы прерываний, первый 7 и второй 8 триггеры переходят в нулевое состояние. Так как первый триггер 7 находится в нулевом состоянии, то импульсы последовательностей Т2 и ТЗ на выходы первого 12 и второ- 35 го 13 логических элементов И не поступают и на выходах 19 и 20 устройства информация не изменяется.

После обработки очередного прерывания от периферийного устройства 40 процессор выдает на вход 17 устройства сигнал готовности к обработке следующих прерываний.

При поступлении очередного импульса последовательности Т первый триггер 7 переходит в единичное состояние и устройство приступает к обработке последующего прерывания от периферийного устройства, имеющего в текущий момент времени наивысший приоритет.

При отсутствии сигналов прерываний от периферийных устройств все триггеры регистра 1 прерываний.будут находиться в нулевом состоянии. При этом на выходе приоритетного шифратора II, а следовательно, и на выходах 19 и 20 устройства сигналы будут отсутствовать.

В режиме циклического опроса периферийных устройств устройство функционирует следуюп5им образом.

На вход 16 устройства циклического опроса в этом режиме поступает сигнал от процессора. При готовности процессора к обслуживанию прерываний на вход 17 поступает сигнал готовности процессора.

При поступлении первого импульса последовательности Т1 от генератора 6 тактовых импульсов первый 7 и второй 8 триггеры переходят в единичное состояние, третий триггер 9 - в нуле- вое состояние, а в регистр 1 прерываний записываются сигналы прерываний от периферийных устройств. На выходе третьего логического элемента И 14 появляется единичный сигнал, открывающий -по второму входу вторые логические элементы И коммутаторов 3 и закрывающий по второму инверсному входу первые логические элемен- ты И этих коммутаторов.Сигналы с выходов первых j логических элементов ИЛИ 4 (где j - код периферийного устройства, записанный в регистре 2 кода прерывающего уст- ройства) закрывают соответствующие коммутаторы 3 по третьему инверсному входу вторых логических элементов И. Следовательно, сигналы только с К-х разрядов регистра 1 прерываний (где .) через соответствующие комму таторы 3 поступают на входы приоритетного шифратора 11. На выходе приоритетного шифратора 1 сформируется код периферийного устройства с наивысшим приоритетом.

После окончания обслуживания процессором текущего прерывания уст- ройство для обработки прерываний сможет обслуживать прерывания от периферийных устройств, приоритет ко- торых ниже, чем приоритет ранее обслуженного периферийного, устройства. После обслуживания периферийного устройства с наименьшим приоритетом на входах приоритетного шифратора 11 будут присутствовать нулевые сигн,алы При этом по импульсу последовательности Т2 третий триггер 9 перейдет в единичное состояние, в результате че го по второму входу третий логически элемент И 14 будет закрыт. Это приведет к включению коммутаторов 3 по .первым логическим элементам И, через которые информация с регистра 1 прерываний поступит на входы приоритетного шифратора 11. По импульсу последовательности ТЗ в регистр 2 кода прерывающего устройства запишется код периферийного устройства, требующего прерывания и имеющего в текущий момент времени наивысший приоритет.

Далее в этом режиме устройство функционирует аналогично описанном алгоритму.

Если необходимо обработать несколько прерываний подряд от одного периферийного устройства, то на выходе 20 сигнала прерывания устройства будет присутствовать единичный сигнал до тех пор, пока прерывания не будут обслужены. При этом процессор на вход 17 готовности устройства выдает сигнал только после отсутствия сигнала прерывания на выходе 20 устройства.

Формула изобретения

Устройство для обработки прерываний. Содержащее приоритетный шифратор, генератор тактовых импульсов, первый выход которого соединен с управляющим входом регистра прерываний, С-входами первого и второго триггеров и R-входом третьего триггера, второй выход -,с первым входом п(эрвого логического элемента И, третий выход - с первым входом второго логического элемента И, выход которого соединен с управляющим входом регистра кода прерывающего устройства, а второй вход - с вторым входом первого логического элемента И и единичным выходом первого триггера, при этом единичный выход второго триггера соединен с первым входом третьего логического элемента И, второй вход которого соединен с нулевым выходом третьего триггера, С-вход которого подключен к выходу первого логического элемента И, а D-вход - к выходу логического элемента ШШ-НЕ, при этом входы логического элемента ИЛИ-НЕ соединены с выходной группой приоритетного шиф- j aTopa и информационными, входами регистра кода прерывающего устройства, группа выходов которого образует выход кода периферийного устройства и соединена с входами дешифратора, п выходов которого соединены соответственно с первыми входами (п-1) логических элементов ШШ и вторым входом (n-l)-TO логического элемента ИЛИ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования сигналов прерывания | 1986 |

|

SU1341640A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Процессор | 1983 |

|

SU1213485A1 |

| Устройство для обмена информацией между ЭВМ и периферийными устройствами | 1989 |

|

SU1777145A2 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство управления | 1989 |

|

SU1654820A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1134936A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1462315A1 |

| Устройство для сопряжения микроЭВМ с внешним устройством | 1985 |

|

SU1283780A1 |

| Устройство приоритета | 1985 |

|

SU1269135A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при проектировании вычислительных систем. Цель изобретения - повышение быстродействия. Устройство содержит приоритетный шифратор, генератор импульсов, дешифратор, счетчик, мультиплексор, триггеры, элементы И, ИЛИ, ИЛИ-НЕ, регистр кода периферийного устройства и коммутаторы. 1 табл., 1 ил.

| Устройство для формирования сигналов прерывания | 1986 |

|

SU1341640A1 |

| ПРИБОР ДЛЯ ОПРЕДЕЛЕНИЯ РОВНОТЫ ХОЛСТА НА ТРЕПАЛЬНОЙ МАШИНЕ | 1934 |

|

SU42836A1 |

| Устройство двукратного усилителя с катодными лампами | 1920 |

|

SU55A1 |

Авторы

Даты

1990-11-15—Публикация

1986-07-18—Подача