Изобретение относится к вычислительной технике и может быть использовано для контроля цифровых блоков.

При проектировании цифровых бло - ков не всегда можно учесть разброс и флуктуацию временных характеристик цепей прохождения сигналов,, что случайным образом определяет верную и неверную последовательность сигналов обуславливая тем самымпоявление состязаний (гонок) этих сигналов, проявляющих себя в неустойчивых сбоях.

Цель изобретения - увеличение глубины контроля за счет обеспечения контроля i-ro процесса ( , . .. ,п), п - число контрольных точек контролируемого цифрового блока) в заданных допустимых пределах изменения.

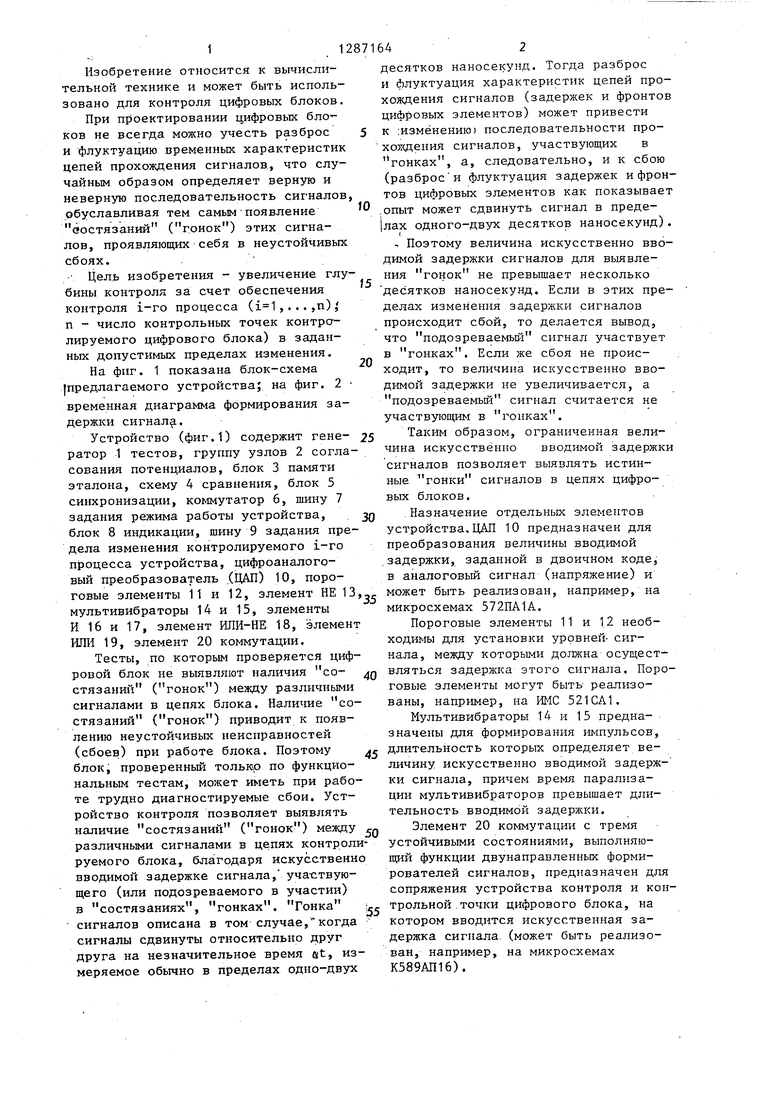

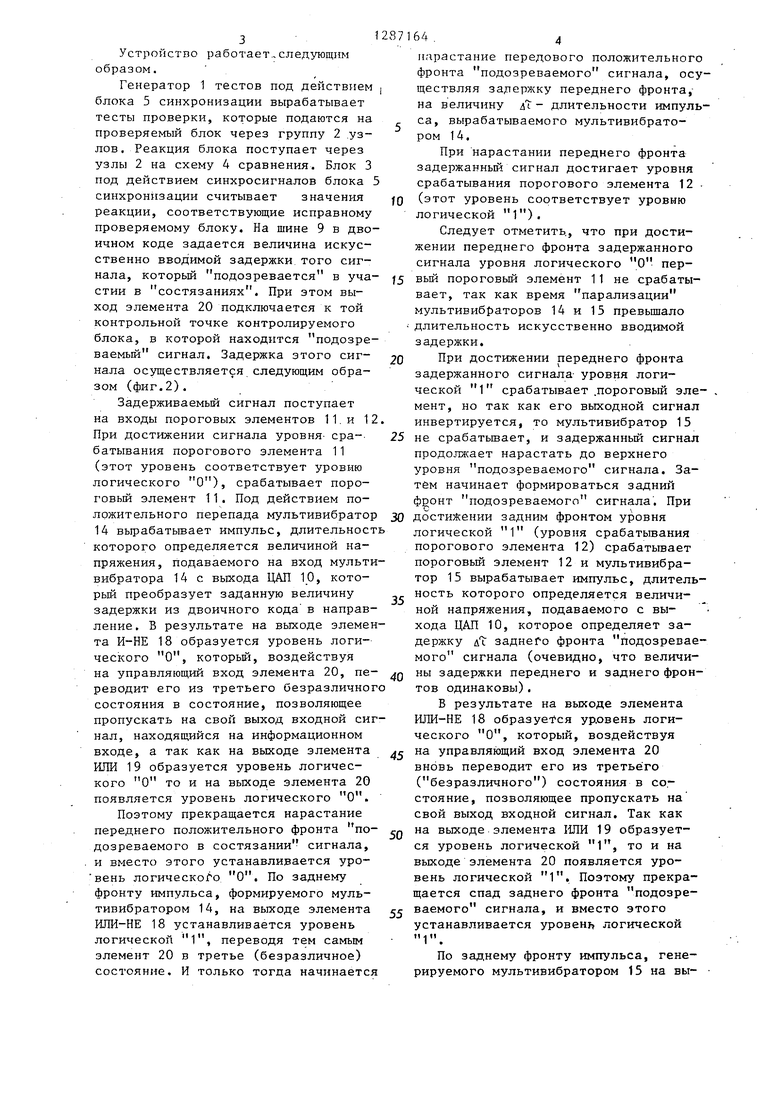

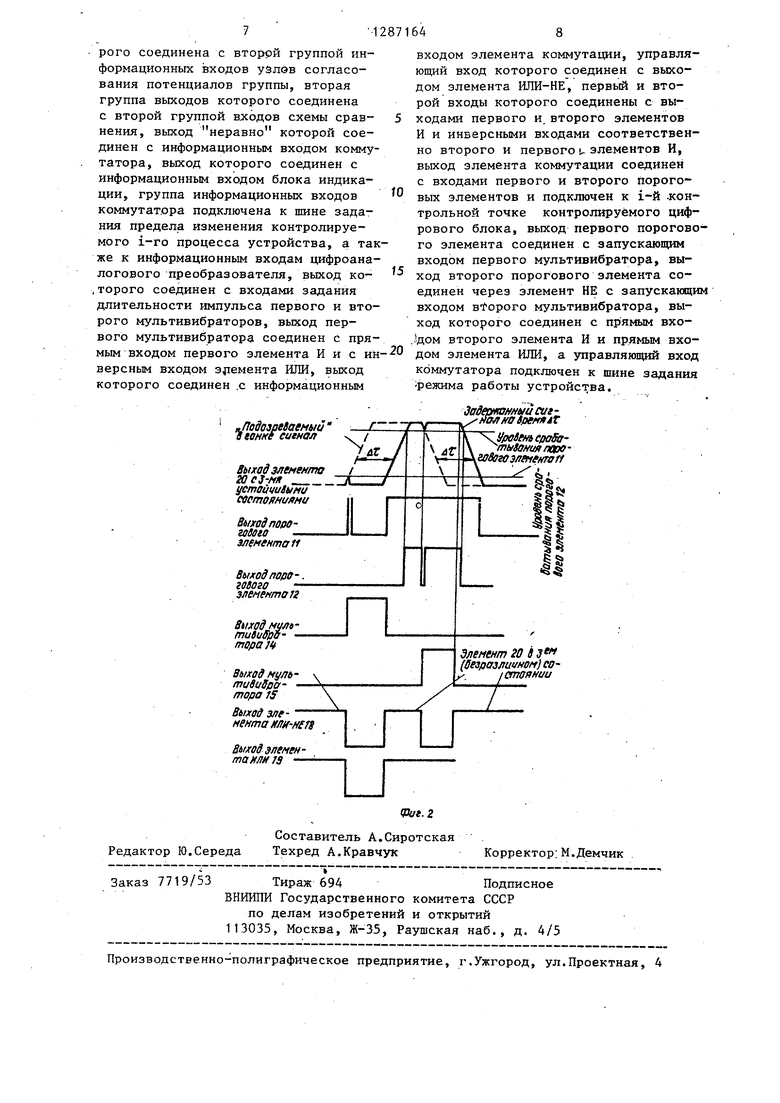

На фиг. 1 показана блок-схема предлагаемого устройства; на фиг. 2

временная диаграмма формирования задержки сигналу.

Устройство (фиг.1) содержит гене- ратор 1 тестов, группу узлов 2 согласования потенциалов, блок 3 памяти

эталона, схему 4 сравнения, блок 5 синхронизации, коммутатор 6, шину 7 задания режима работы устройства, блок 8 индикации, шину 9 задания предела изменения контролируемого i-ro процесса устройства, цифроаналого- вый преобразователь .(ЦДЛ) 10, пороговые элементы 11 и 12, элемент НЕ 13 мультивибраторы 14 и 15, элементы И 16 и 17, элемент ИЛИ-НЕ 18, элемент ИЛИ 19, элемент 20 коммутации.

Тесты, по которым проверяется цифровой блок не выявляют наличия со- стязанш (гонок) между различными сигналами в цепях блока. Наличие состязаний (гонок) приводит к появлению неустойчивых неисправностей (сбоев) при работе блока. Поэтому блок, проверенный только по функциональным тестам, может иметь при работе трудно диагностируемые сбои. Устройство контроля позволяет выявлять наличие состязаний (гонок) между различными сигналами в цепях контролируемого блока, благодаря искусственн вводимой задержке сигнала, участвующего (или подозреваемого в участии) в состязаниях, гонках. Гонка сигналов описана в том случае,когда сигналы сдвинуты относительно друг друга на незначительное время at, измеряемое обычно в пределах одно-двух

.

в, х

12871642

десятков наносекунд. Тогда разброс и флуктуация характеристик цепей прохождения сигналов (задержек и фронтов цифровых элементов) может привести 5 к .изменению) последовательности про- хоз: дения сигналов, участвующих в

гонках, а, следовательно, и к сбою (разброс и флуктуация задержек и фронтов цифровых элементов как показывает .опыт может сдвинуть сигнал в преде- лах одного-двух десятков наносекунд).

- Поэтому величина искусственно вводимой задержки сигналов для выявления гонок не превышает несколько десятков наносекунд. Если в этих пределах изменения задержки сигналов происходит сбой, то делается вывод, что подозреваемый сигнал участвует в гонках. Если же сбоя не происходит, то величина искусственно вводимой задержки не увеличивается, а сигнал считается не

подозреваемый

участвующим в гонках.

5

5

о

д п Таким образом, ограниченная величина искусственно вводимой задержки сигналов позволяет выявлять истинные гонки сигналов в цепях цифровых блоков.

.Назначение отдельных элементов устройства.ДАЙ 10 предназначен для преобразования величины вводимой задержки, заданной в двоичном коде, в аналоговый сигнал (напряжение) и может быть реализован, например, на микросхемах 572ПА1А.

Пороговые элементы 11 и 12 необходимы для установки уровней- сигнала, между которьми должна осуществляться задержка этого сигнала. Пороговые элементы могут быть реализованы, например, на ИМС 521СА1.

Мультивибраторы 14 и 15 предна- значены для формирования импульсов, длительность которых определяет величину искусственно вводимой задержки сигнала, причем время парализации мультивибраторов превышает длительность вводимой задержки.

Элемент 20 коммутации с тремя устойчивыми состояниями, выполняющий функции двунаправленных формирователей сигналов, предназначен для сопряжения устройства контроля и кон- - трольной точки цифрового блока, на котором вводится искусственная задержка сигнала, (может быть реализован, например, на микросхемах К589АП16).

3

Устройство работает,-следующим образом.

Генератор 1 тестов под действием блока 5 синхронизации вырабатывает тесты проверки, которые подаются на проверяемый блок через группу 2 .узлов. Реакция блока поступает через узлы 2 на схему 4 сравнения. Блок 3 под действием синхросигналов блока 5 синхронизации считывает значения реакции, соответствующие исправному проверяемому блоку. На шине 9 в двоичном коде задается величина искусственно вводимой задержки того сигнала, который подозревается в уча- стии в состязаниях. При этом выход элемента 20 подключается к той контрольной точке контролируемого блока, в которой находится подозреваемый сигнал. Задержка этого сиг- нала осуществляется следующим образом (фиг.2).

Задерживаемый сигнал поступает на входы пороговых элементов 11. и 12 При достижении сигнала уровня- ера-. батывания порогового элемента 11 (этот уровень соответствует уровню логического О), срабатывает поро- говьй элемент 11. Под действием положительного перепада мультивибратор 14 вьфабатывает импульс, длительност которого определяется величиной напряжения, подаваемого на вход мультивибратора 14 с выхода ЦАП 10, кото- рьш преобразует заданную величину задержки из двоичного кода в направление. В результате на выходе элемента И-НЕ 18 образуется уровень логического О, которьш, воздействуя на управляющий вход элемента 20, пе- реводит его из третьего безразличног состояния в состояние, позволяющее пропускать на свой выход входной сигнал, находящийся на информационном входе, а так как на выходе элемента ИЛИ 19 образуется уровень логического О то и на выходе элемента 20 появляется уровень логического О ,

Поэтому прекращается нарастание переднего положительного фронта по- дозреваемого в состязании сигнала, и вместо этого устанавливается уро- вень логического О. По заднему фронту импульса, формируемого мультивибратором 14, на выходе элемента ИЛИ-НЕ 18 устанавливается уровень логической 1, переводя тем самым элемент 20 в третье (безразличное) состояние. И только тогда начинается

64 .4

нарастание передового положительног фронта подозреваемого сигнала, осществляя задержку переднего фронта,- на величину м- длительности импулса, вырабатываемого мультивибратором 14.

При нарастании переднего фронта задержанный сигнал достигает уровня срабатывания порогового элемента 12 (этот уровень соответствует уровню логической 1).

Следует отметить., что при достижении переднего фронта задержанного сигнала уровня логического О первый пороговый элемент 11 не срабатывает, так как время парализации мультивибраторов 14 и 15 превьшало длительность искусственно вводимой задержки.

При достижении переднего фронта задержанного сигнала- уровня логической 1 срабатывает .пороговый элемент, но так как его выходной сигнал инвертируется, то мультивибратор 15 не срабатьшает, и задержанньй сигнал продояясает нарастать до верхнего уровня подозреваемого сигнала. Затем начинает формироваться задний подозреваемого сигнала. При достижении задним фронтом уровня логической 1 (уровня срабатывания порогового элемента 12) срабатывает пороговый элемент 12 и мультивибратор 15 вырабатывает импульс, длительность которого определяется величиной напряжения, подаваемого с выхода ЦАП 10, которое определяет задержку дТ заднего фронта подозреваемого сигнала (очевидно, что величины задержки переднего и заднего фронтов одинаковы).

Б результате на выходе элемента ИЛИ-НЕ 18 образуешься ур.овень логического О, который, воздействуя на управляющий вход элемента 20 вновь переводит его из третьего (беэразличного) состояния в со.- стояние, позволяющее пропускать на свой выход входной сигнал. Так как на выходе элемента 1ШИ 19 образуется уровень логической 1, то и на выходе элемента 20 появляется уровень логической 1. Поэтому прекращается спад заднего фронта подозреваемого сигнала, и вместо этого

устанавливается уровень логической

ti t II 1 .

По зал,нему фронту импульса, генерируемого мультивибратором 15 на вы-

ходе элемента ИЛИ-НЕ 18 устанавливается уровень логической 1, переводя тем самым элемент 20 в третье безразличное состояние. И только тогда начинается спад заднего фронта подозреваемого сигнала.. Так осущестЬляется задержка заднего фронта подозреваемого сигнала на величину At. В итоге подозреваемый

сигнал полностью задерживается на величину задержки д Г .

Выявление наличия состязания осуществляется следующим образом. Выход коммутационного элемента с тремя устойчивыми состояниями элемента 20 подключается к той точке контролируемо го объекта, в которой находится подозреваемьй в

состязаниях

сигнал (это может быть цепь объекта контроля). Затем задается величина задержки этого сигнала и генератор 1 тестов под действием блока 5 синхронизации вырабатывает тесты проверки. В случае совпадения эталонной реакции и реакции блока . по всем тестам при заданной задерж- ке, задается новое большое значение задержки, и вновь осуществляется проверка по всем тестам,. Пределы изменения величины задержки определяются конкретным типом логического блока, обуславливающим определенньш разброс и флуктуацию временных харатеристик его цепей.

Если в заданных пределах изменения задержки сигнала осуществляется прохолсдение всех тестов, то делаетс

сигнал н

, в ином

случае делается вывод о наличии состязания и месте его нахождения , что позволяет соответствующим образом корректировать схемные решения контролируемого блока. Таким обра- зрм, подключаясь к различным точкам контролируемого блока, его можно поностью проверить на наличие состявывод, что подозреваемьй участвует в состязаниях

Если рассмотреть входную комбинацию (00) на прямых входах элементов И 16 и 17, то можно увидеть, что в зтом случае на выходах обоих элементов И 16 и 17 будут присутствовать О и, следовательно, на выходе.. ИЛИ- НЕ 18 будет 1, которая переведет - элемент 20 в безразличное состояние. Это обстоятельство использовано в схеме устройства, что проиллюстрцро

5

0

5

вано временной диаграммой на фиг.2. Входную комбинацию 00 нельзя в данном случае рассматривать как запрещенную, так как этот код подается на входы элементов И 16 и 17.

Таким образом, элементы И 16 и 17 и элемент ИЛИ-НЕ 18 обеспечивает формирование сигналов, представленных на временной диаграмме.

Следует отметить, что о наличии постоянной логической 1 на выходе элемента ИЛИ 19 правомерно только для трех входных комбинаций 00, 01 и 11. При наличии же четвертой оставшейся входной комбинации 10 на выходе элемента ИЛИ 19 будет присутствовать уровень логического О (входной сигнал, равный логической 1 на первом входе ИЛИ 19 инвертируется и по ИЛИ складываются два входных сигнала, равных логическому О).

Таким образом, элемент ИЛИ 19 обеспечивает формирование сигналов, представленных на временной диаграмме на фиг. 2.

Формула изобретения

Устройство для контроля цифровых

блоков, содержащее блок синх;рониза- ции, схему сравнения, блок индикации, коммутатор, генератор тестов, блок памяти э талона, причем первый выход блока синхронизации соединен с син- хровходом генератора тестов, второй выход блока синхронизации соединен с Входом считывания блока памяти эталона, группа выходов которого соединена с первой группой входов схемы

сравнения, отличающееся тем, что, с целью увеличения глубины контроля за счет обеспечения контроля i-ro процесса (i-1,..., п , п .- число контрольных точек контролируемого цифрового блока) в заданных допустимых пределах изменения, устройство содержит группу узлов согласования потенциалов, цифроана- логовой преобразователь, два пороговых элемента, элемент НЕ, два элемента И, элемент ЙЛИ-НЕ, элемент ИЛИ, элемент коммутации и два мультивибратора, причем группа выходов генератора тестов соединена с первой группой входов узлов согласования потенциалов группы, первая группа выходов которого соединена с группой информационных входов контролируемого цифрового блока, группа выходов которого соединена с второй группой информационных входов узлов согласования потенциалов группы, вторая группа выходов которого соединена с второй группой входов схемы сравнения, выход неравно которой соединен с информационным входом коммутатора, выход которого соединен с информационным входом блока индикации, группа информационных входов коммутатора подключена к шине задания предела изменения контролируемого i-ro процесса устройства, а так же к информационным входам цифроана- логового преобразователя, выход ко- , торого соединен с входами задания длительности импульса первого и второго мультивибраторов, выход первого мультивибратора соединен с прямым входом первого элемента И и с ин версным входом элемента ИЛИ, выход которого соединен .с информационным

Редактор Ю.Середа

1)3аг.2

Составитель А.Сиротская Техред А.Кравчук

Заказ 7719/53 Тираж 694Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

10

15

20

входом элемента коммутации, управляющий вход которого соединен с выходом элемента ИЛИ-НЕ, первый и второй входы которого соединены с выходами первого и,второго элементов И и инверсными входами соответственно второго и первого и элементов И, выход элемента коммутации соединен с входами первого и второго пороговых элементов и подключен к i-й -контрольной точке контролируемого цифрового блока, выход первого порогового элемента соединен с запускающим входом первого мультивибратора, выход второго порогового элемента соединен через элемент НЕ с запускакщим входом второго мультивибратора, выход которого соединен с прямым вхо- ,)дом второго элемента И и прямым входом элемента ИЛИ, а управляющий вход коммутатора подключен к шине задания режима работы устройства.

Корректор;М.Демчик

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения сбоев синхронизируемых дискретных блоков | 1983 |

|

SU1125628A1 |

| Устройство для обнаружения сбоев синхронизируемой цифровой системы | 1984 |

|

SU1176332A1 |

| Устройство для контроля цифровых узлов | 1982 |

|

SU1059576A1 |

| Устройство для контроля цифровых объектов | 1986 |

|

SU1319037A2 |

| Генератор случайных чисел | 1982 |

|

SU1070547A1 |

| УПРАВЛЯЕМЫЙ ГЕНЕРАТОР ИМПУЛЬСОВ | 2003 |

|

RU2254670C1 |

| Устройство для контроля электромагнита | 1986 |

|

SU1388832A1 |

| Устройство для контроля логических узлов | 1981 |

|

SU993168A1 |

| Сигнатурный анализатор | 1987 |

|

SU1513450A1 |

| Устройство для контроля цифровых блоков | 1989 |

|

SU1793441A2 |

Изобретение относится к вычислительной технике и может быть использовано для контроля цифровых объектов. Целью изобретения является увеличение глубины контроля за счет обеспечения контроля i-ro процесса (,..., п, где п - число контрольных точек контролируемого блока) в заданных допустимых пределах изменения. Устройство содержит блок 5 синхронизации, генератор 1 тестов, узел 2 связи с объектом, схему 4 сравнения, эталонньй блок 3, коммутатор 6, переключатель 7, блок 8 индикации, блок 9 переключателей,, цифроаналоговый преобразователь 10, первый и второй пороговые элементы 11 и 12, первый и второй мультивибраторы 14 и 15, элемент НЕ 13, элементы И 16.1 и 16.2, элемент 11Ш 19, элемент ШМ-НЕ 18, элемент 20 коммутаций (с тремя устойчивыми состояниями) . Устройство позволяет проверить наличие состязаний между сигналами в цепях контролируемого блока. 2 ил. S (Л 1C 00 « а

| Устройство для контроля логических блоков цвм | 1976 |

|

SU633019A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля цифровых блоков | 1975 |

|

SU607218A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-01-30—Публикация

1985-04-09—Подача