Изобретение относится к контро льно-измерительной технике и может быть использовано для контроля логических узлов с последовательностными схемами.

Известно устройство для проверки логических узлов по заранее составленной тестовой последовательности, содержащее блок считывания программы проверки, регистр входных сигналов / блок формирователей входных сигналов, регистр контрольньзх вы- ; ходных сигналов и блок сравнения контрольных сигналов с выходными .сигнала1да1 проверяемого логического узла Ц .

Недостатком устройства является низкая достоверность контроля, обусловленная тем, что используемые регулярные контролирующие тесты не обеспечивают необходимой полноты охвата сложных цифровых узлов, содержащих 500 и более .логических вентилей.

Наиболее близким техническим ре- , шением к предлагаемому является устройство для контроля цифровых узлов, содержащее генератор тактовых импульсов, индикатор, задатчик логи ческого нуля, задатчик псевдослучайного кода, блок разделения фронтов входных сигналов, первые и вторые элементы И-НЕ, первый и второй формирователи логического узла и блок сравнения С 2.

Для уменьшения вероятности возникновения гонок фронтов в контрольном узле каждый новый входной набор передается на его входы поразрядно, . что не позволяет избежать гонок фрон хов, если в контролируемом узле имеются синхронизированные триггеры с запрещенными комбинациями входных сигналов, DV-триггеры с комбинационными схемами; на V-входах и т.п., что ограничивает область применения известного устройства.

Цель изобретения - расширение области применения устройства.

20

Поставленная цель достигается тек.- что в устройство для контроля логических узлов, содержащее генератор тактовых импульсов, индикатор, задатчик логического- нуля, эадатчик псевдослучайного кода, соединенный первыми выходами с первыми входами соответствующих первых элементов ИНЕ, выходы которых, соединены с первыми входами вторых элементов И-НЕ,

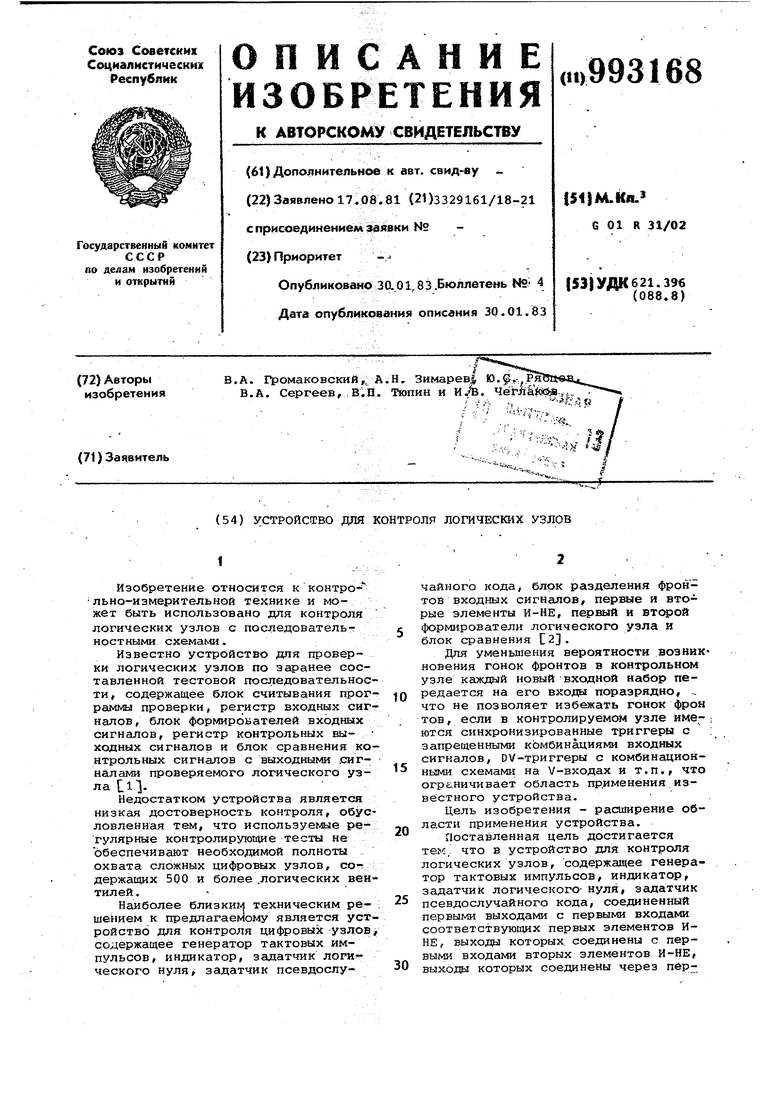

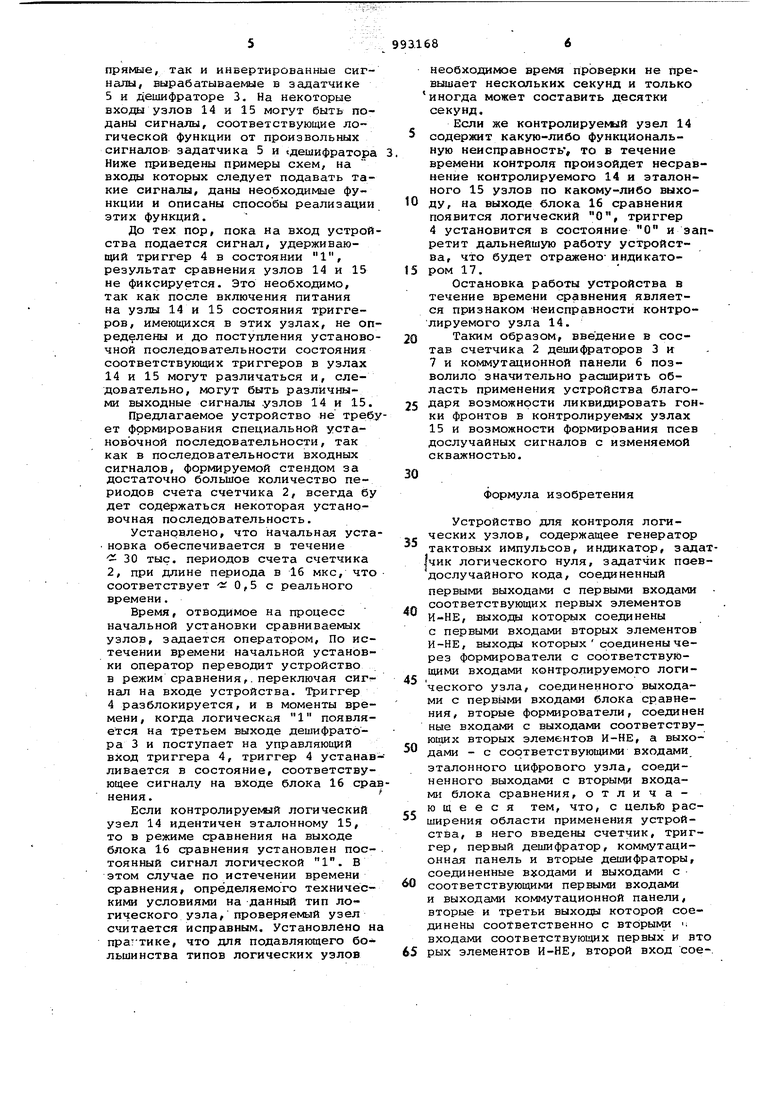

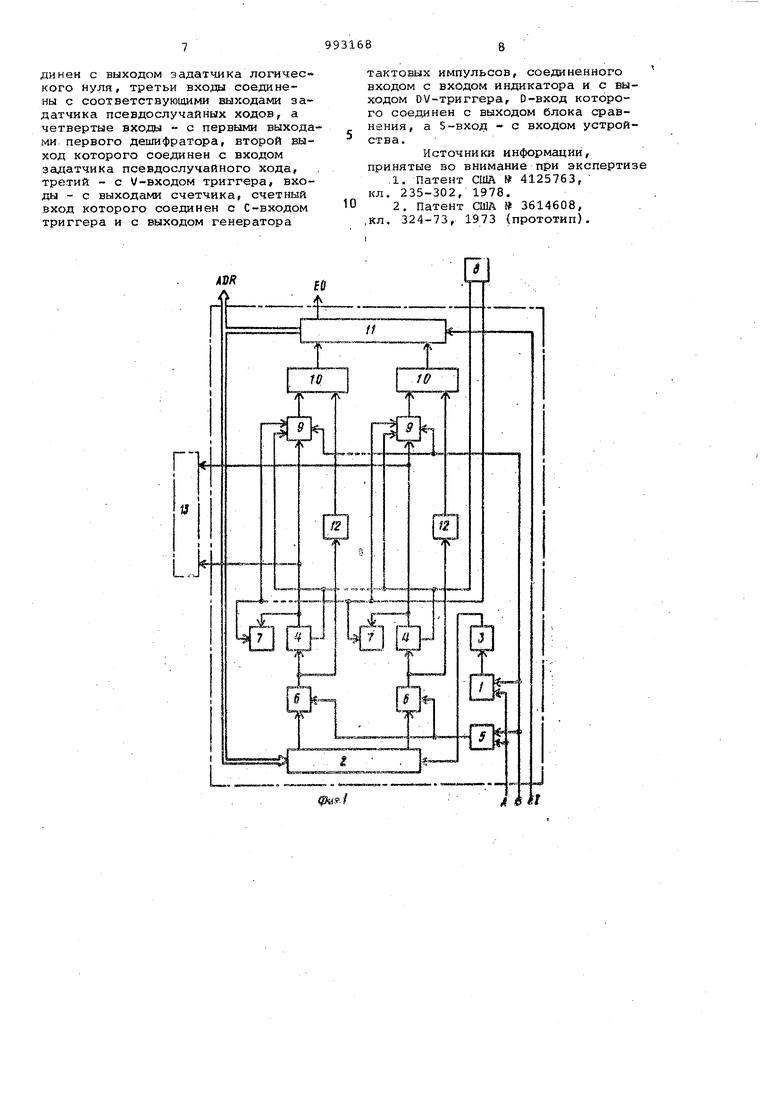

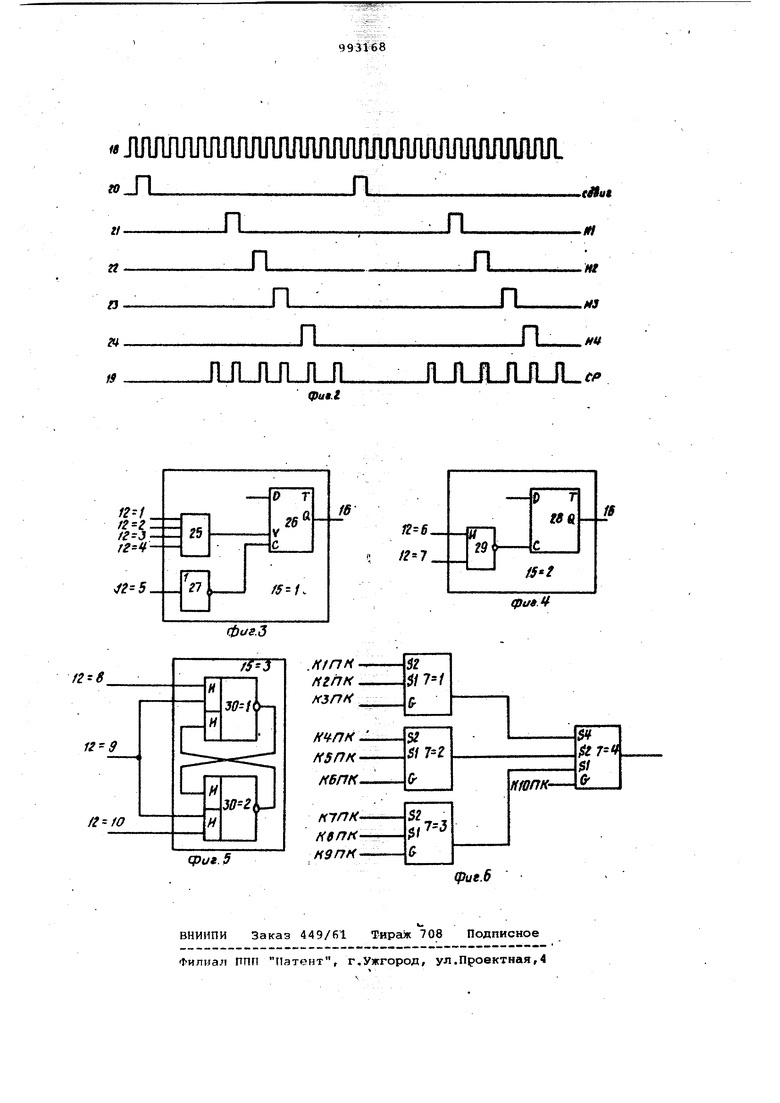

30 выходы которых соединены через первые формирователи с соответствующими входами контролируемого логического узла, соединенного выходами с первыми входами блока сравнения, вторые формирователи, соединенные входами с выходами соответствующих вторых элементов И-НЕ, а выходами с соответствующими входами эталонного цифрового узла, соединенного выходами с вторыми входами блока сравнения, введены счетчик, триггер первый дешифратор, коммутационная 1анель и вторые дешифраторы, соеди|ненные входами и выходами с соответ ствующими первыми входами и выxoдa iи коммутационной панели, вторые и тре тьи выходы которой соединены соответственно с вторыми входами соответствующих первых и вторых элемен тов И-НЕ, второй вход соединен с выходом задатчика логического нуля, третьи входы соединены с соответствующими выходами задатчика псевдослучайных кодов, а четвертые входы - с первыми выходами первого дешифратора, второй выход коюрого со динен с входом задатчика псевдослучайного кода, третий - с V-входом триггера, входы - с выходами счетчи ка, счетный вход которого соединен С-входом триггера и с выходом генератора тактовых импульсов, соединен ного входом с входом индикатора и с выходом DV-триггера, D-вход которог соединен с выходом блока сравнения, а S-вход - с входом устройства. На фиг.1 приведена блок-схема уст ройства; на фиг. 2 - временные диаграммы его работы; на фиг. 3 - 5 - пр меры функциональных схем контролируе мых узлов; на фиг. б - пример соединения дешифраторов устройства. Устройство содержит генератор 1 тактовых импульсов, счетчик 2, первый дешифратор 3, триггер 4, ЗсЩатЧи 5 псевдослучайного кода, коммутацион ную панель б, вторые дешифраторы 7, задатчик 8 логического нуля, логические блоки 9, первые элементы 10 И-НЕ, вторые элементы 11 И-НЕ, первый формирователь 12, второй формиро ватель 13,контролируемый логический узел 14, эталонный логический узел 15, блок 16 сравнения, индикатор 17 Кроме того, обозначены (фиг. 2): временная диаграмма 18 сигналов генератора 1, временная диаграмма 19 сигналов на третьем выходе дешифрат ра 3, временная диаграмма 20 сигнала на втором выходе дешифратора 3, вре менные диаграммы 21 - 24 на первых прямых выходах дешифратора 3, а так же (фиг. 3) произвольный логичес- кий блок 25, DV-триггер 26, инвертор 27, ov-триггер 28, элемент И 29 (фиг. 4); элементы И ИЛИ-НЕ 30 (фи г. 5 ) . Входы логических 15-1, 15-2, 15-3 узлов, соединенные с формирователями 12 блоков 9, обозначены 12-1-1210 (фиг. 3-5). Коммутационная панель 6 выполняется в виде расположенного в одной плоскости набора контактных гнезд, каждому входу и каждому выходу соответствует отдельное гнездо. Установкой перемычек, состоящих из нужного числа соединенных проводами контактных штырей, может быть осуществлена электрическая связь между произвольным количеством гнезд панели 6. Все шины, соединенные с выходными гнездами коммутационной панели 6, должны быть также подключены через резистор к шине питания. Это обеспечивает наличие на шине потенциала логической 1, если на соответствующих выходах коммутационной панели не подан какой-либо другой сигнал. Устройство работает следующим образом. В соответствии с подготовленной заранее проверочной документацией на коммутационной панели 6 устанавливаются перемычки, необходимые для проверки логического узла 15 данного типа. После этого подается питание на проверяемый 14 и эталонный 15 логические узлы. При этом на вход устройства подается сигнал, безусловно, устанавливающий триггер 4 в состояние 1. Логическая 1 на выходе триггера 4 разрешает работу генератора 1.Счетчик 2 считает импульсы генератора 1, дешифратор 3 преобразует выходные сигналы счетчика 2 в сигналы, временные диаграммы которых приведены на фиг. 2. . В начале каждого периода счета счетчика 2 вырабатывается сигнал на втором выходе дешифратора 3 (временная диаграмма 20). Этот сигнал поступает в задатчик 5, изменяющий по этому сигналу свое состояние. После этого на нескольких первых выходах дешифратора 3 вырабатываются импульсные сигналы (показаны на временных диаграммах 21 24); поступающие через панель 6 на входы дешифраторов 7. На каждый период счета счетчи ка 2 вырабатываются один набор многоразрядного псевдослучайного кода и набор импульсных сигналов. На отдельные входы логических узлов 14 и 15 могут быть поданы через элементы 10 и 11 соответствующие сигналы псевдослучайного кода из задатчика 5 без преобразования. На некоторые другие входы узлов 14 и 15 через коммутационную панель 6 и элементИ-НЕ 11 могут быть поданы как произвольные.

прямые, так и инвертированные сигналы, вырабатываемые в эадатчике 5 и дешифраторе 3. На некоторые входы узлов 14 и 15 могут быть поданы сигналы, соответствующие логической функции от произвольных сигналов- задатчика 5 и (дешифратора Ниже приведены примеры схем, на входы которых следует подавать такие сигналы, даны необходимые функции и описаны способы реализации этих функций.

До тех пор, пока на вход устройства подается сигнал, удерживающий триггер 4 в состоянии 1, результат сравнения узлов 14 и 15 не фиксируется. Это необходимо, так как после включения питания на узлы 14 и 15 состояния триггеров, имею1цихся в этих узлах, не определены и до поступления установочной последовательности состояния соответствующих триггеров в узлах 14 и 15 могут различаться и, следовательно, могут быть различными выходные сигналы узлов 14 и 15.

Предлагаемое устройство не требет формирования специальной установочной последовательности, так как в последовательности входных сигналов, формируемой стендом за достаточно большое количество периодов счета счетчика 2, всегда бу дет содержаться некоторая установочная последовательность.

Установлено, что начальная установка обеспечивается в течение 30 тыс. периодов счета счетчика 2, при длине периода в 16 мкс, что соответствует : 0,5 с реального времени.

Время, отводимое на процесс начальной установки сравниваемых узлов, задается оператором. По истечении времени начальной установки оператор переводит устройство в режим сравнения,.переключая сигнал на входе устройства. Триггер 4 разблокируется, и в моменты времени, когда логическая 1 появляется на третьем выходе дешифратора 3 и поступает на управляющий вход триггера 4, триггер 4 устанавливается в состояние, соответствующее сигналу на входе блока 16 сранения .

Если контролируемый логический узел 14 идентичен эталонному 15, то в режиме сравнения на выходе блока 16 сравнения установлен постоянный сигнал логической 1. В этом случае по истечении времени сравнения, определяемого техническими условиями на -данный тип логического узла, проверяемый узел считается исправным. Установлено н прат-тике, что для подавляющего большинства типов логических узлов

необходимое время проверки не превышает нескольких секунд и только иногда может составить десятки секунд.

Если же контролируе лй узел 14 содержит какую-либо функциональную неисправность, то в течение времени контроля произойдет несравнение контролируемого 14 и эталонного 15 узлов по какому-либо выхо0 ду, на выходе блока 16 сравнения появится логический О, триггер 4 установится в состояние О и запретит дальнейшую работу устройства, что будет отражено- индикато5 ром 17.

Остановка работы устройства в течение времени сравнения является признаком неисправности контролируемого узла 14.

0 Таким образом, введение в состав счетчика 2 дешифраторов 3 к 7 и коммутационной панели 6 позволило значительно расширить область применения устройства благо5 даря возможности ликвидировать гонки фронтов в контролируемых узлах 15 и возможности формирования псев дослучайных сигналов с изменяемой скважностью.

30

Формула изобретения

Устройство для контроля логических узлов, содержащее генератор

5 тактовых импульсов, индикатор, задат|чик логического нуля, задатчик псевдослучайного кода, соединенный первыми выходами с первыми входами соответствующих первых элементов

0 И-НЕ, выходы которых соединены с первыми входами вторых элементов И-НЕ, выходы которых соединены через формирователи с соответствующими входами контролируемого логи5ческого узла, соединенного выходами с первыми входами блока сравнения, вторые формирователи, соединен ные входами с выходами соответствующих вторых элементов И-НЕ, а выхо0дами - с соответствующими входами эталонного цифрового узла, соединенного выходами с вторыми входами блока сравнения, отличающееся тем, что, с цельй рас5ширения области применения устройства, в него введены счетчик, триггер, первый дешифратор, коммутационная панель и вторые дешифраторы, соединенные входами и выходами с 0соответствующими первыми входами и выходами коммутационной панели, вторые и третьи выходы которой соединены соответственно с вторыми входами соответствующих первых и вто

5 рых элементов И-НЕ, второй вход сое-.

динен с выходом задатчика логического нуля, третьи входы соединены с соответствующими выходами задатчика псевдослучайных ходов, а четвертые входы - с первыми выхода ш первого дешифратора, второй выход которого соединен с входом задатчика псевдослучайного хода, третий - с У-входом триггера, входы - с выходами счетчика, счетный вход которого соединен с С-входом триггера и с выходом генератора

тактовых импульсов, соединенного входом с входом индикатора и с выходом ОV-триггера, D-вход которого соединен с выходом блока сравнения, а S-вход - с входом устройства.

Источники информации, принятые во внимание при экспертиз

.1. Патент США 4125763, кл. 235-302, 1978.

2. Патент США № 3614608, ,кл. 324-73, 1973 (прототип).

«лллшшллшшпшиииииииишлшииишлл.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для поиска неисправностей в логических узлах | 1981 |

|

SU970283A1 |

| Устройство для проверки логических схем | 1977 |

|

SU717726A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Устройство для диагностики логических узлов | 1980 |

|

SU892445A1 |

| Устройство для контроля монтажа | 1986 |

|

SU1312616A1 |

| Устройство для контроля логических блоков | 1976 |

|

SU643877A1 |

| Устройство для контроля логических блоков | 1983 |

|

SU1101825A1 |

| Устройство для диагностирования логических блоков | 1986 |

|

SU1520518A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1386998A1 |

| Способ поиска дефектов в цифровых блоках и устройство для его осуществления | 1985 |

|

SU1260884A1 |

Авторы

Даты

1983-01-30—Публикация

1981-08-17—Подача