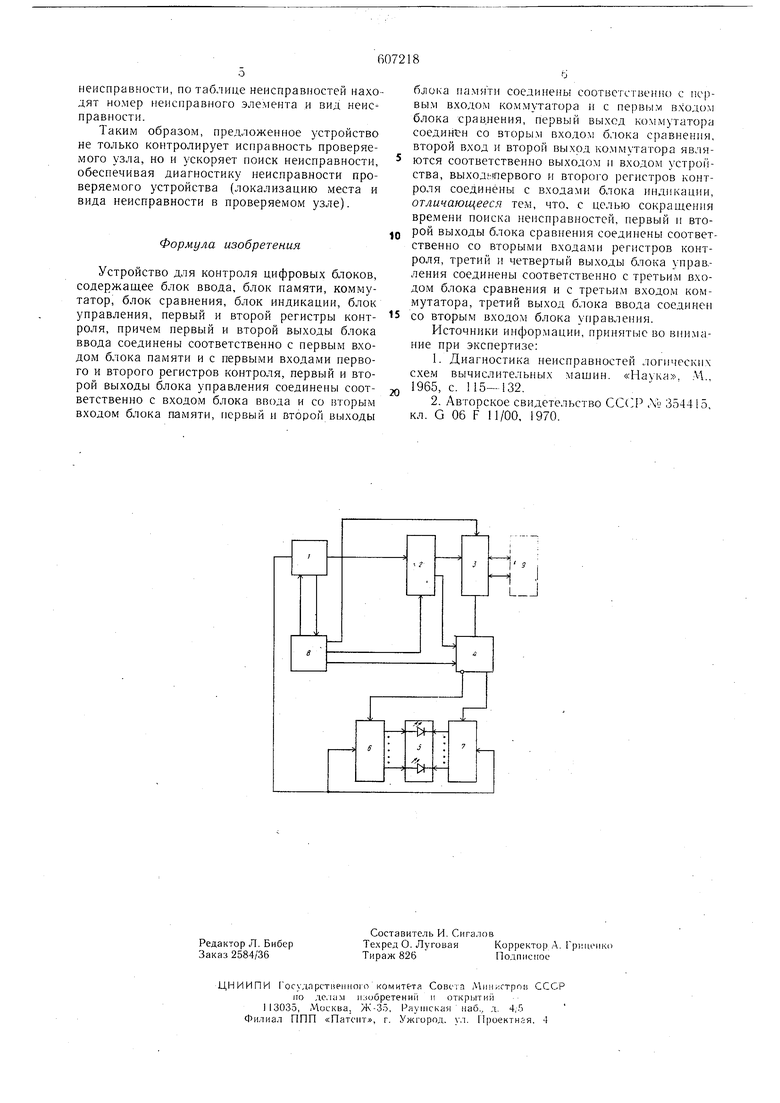

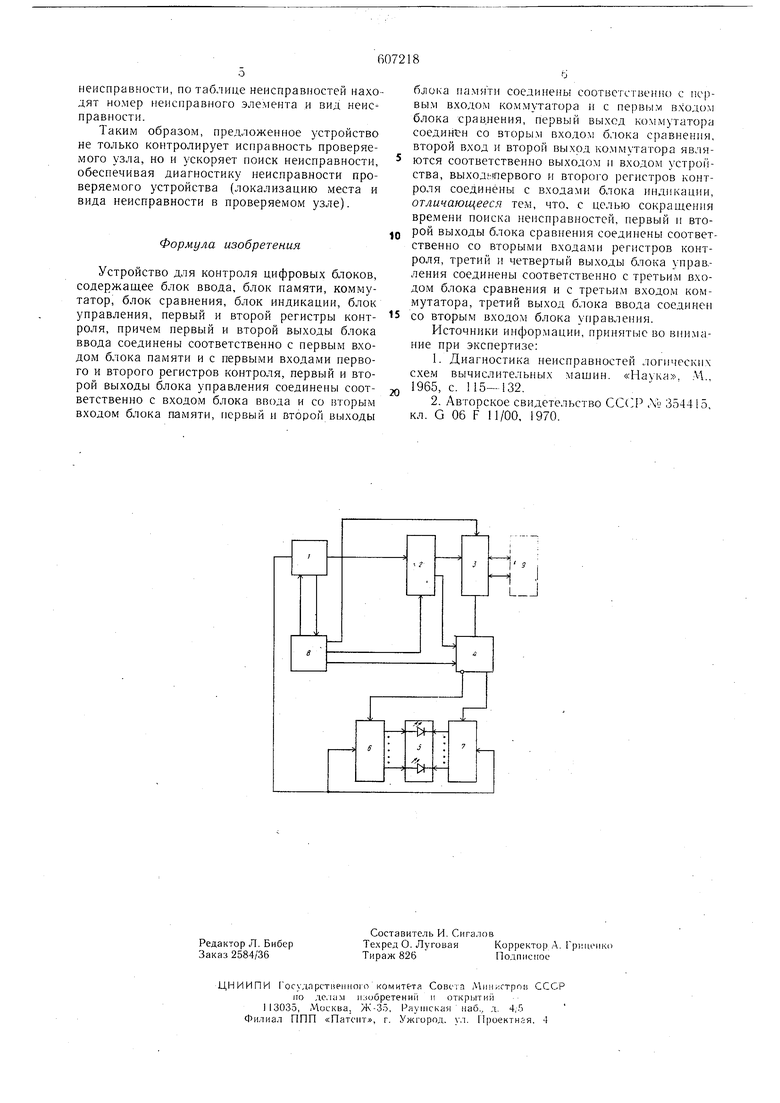

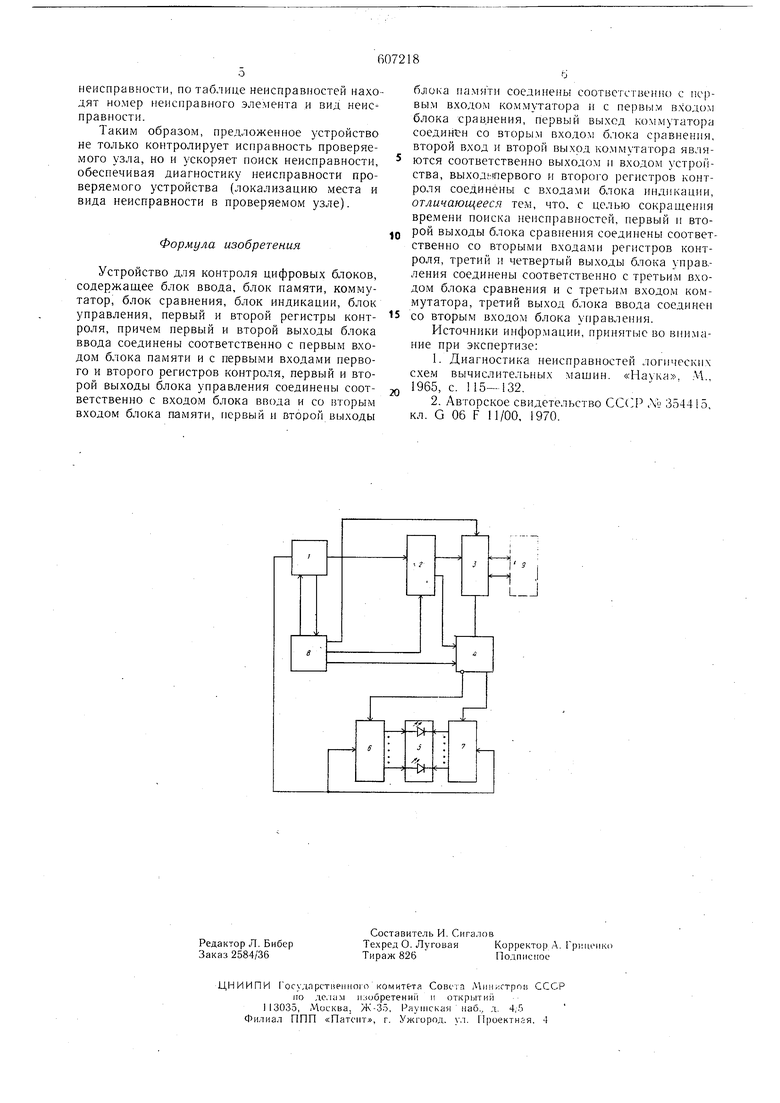

Изобретение отноеится к вычислительной технике, а именно, к уетройствам для контроля цифровых логических схем и диагностики неисправностей. Известны устройства для контроля цифровых блоков, содержащие блок ввода, блок сравнения, блок индикации, блок памяти 1. Недостатком известного устройства является малая степень автоматизации поиска неисправностей, так как при наличии большого числа неудачных исходов тестов просмотр словаря неисправностей, с целью локализации неисправного элемента занимает достаточно много времени. Наиболее близким к изобретению по технической сущности является устройство для КОЙТроля цифровых блоков, содержащее блок ввода, блок па.мяти, ко.ммутатор, блок сравнения, блок индикации, блок управления, первый и второй регистры контроля, причем первый и второй .выходы блока ввода соединены соответственно с первым входом блока памяти и с первыми входами первого и второго регистров контроля, первЫй и второй выходы блока унравления соединены соответственно со входом б.юка ввода и со вторы.м входом блока памяти, первый и второй выходы блока памяти соединены соответственно с первым входом коммутатора и с первым входом блока сравиения, перБ1лй выход коммутатора соединен со вторы.м в.ходом блока сравнения, второй вход и второй выход коммутатора являются соответственно выходо.м и входом устройства, выходы первого и второго регистров контроля соединены со входами блока индикации 2. Это устройство позволяет определить исправность проверяемого узла. Контроль исправности проверяемого узла осуществляется с помощью тестов, а именно, подачей на входы проверяемого узла последовательности входных наборов ипроверкой правильности реакции проверяемого узла. При наличии неисправности в блоке индикации отображается номер набора, на котором обнаружена неисправность и контакт проверяемого .узла, на котором реакция не соответствует эталону. При этом само устройство фиксирует только виещнее проявление неисправности (на каком внешнем контакте проявляется неисправность). Локализация места неисправности (диагностика) осуществляется в дальнейще.м с помощью диагностических словарей или таблиц. В диагностическом словаре перечислены Hcitcnpai ности, провсряем1 10 в каждом тестовом наборе. Имея сведения о всех наборах, на которых проявляется неисправность, с помощью диагностического словаря отыскивается неисправность. изобретения является сокращение времени поиска. Это достигается тем, что в предлагаемом устройстве первый и второй выходы блока сравнения соединены соответственно со вторыми входами регистров контроля, третий и четвертый выходы блока управления соединены соответственно с третьим входом блока сравнения и с третьим входом коммутатора, третий выход блока ввода соединен с вторым входом блока управления. Схема описываемого устройства для контроля цифровых блоков приведена на чертеже. Устройство состоит из блока ввода 1, блока памяти 2, коммутатора 3, блока, сравнения 4, блока индикации 5, первого регистра контроля 6, второго регистра контроля 7, блока управления 8. Блок ввода 1 предназначен для ввода с перфоленты тестовой информации, информации о входных (выходных) контактах, диагностическ.ой инфор.мации (номера неисправностей, проверяемых в каждом тесте) и командной информации. Блок памяти 2 предназначен для хранения и выдачи на проверяемый узел 9 тестовой инфор.мации. Блок памяти 2 разделен на две зоны: в одной хранятся стимулы (набор, подаваемый на входные контакты проверяемого узла 9), во второй - эталон (значения сигналов, которые должны появиться на выходах проверяемого узла 9, если он исправен). Коммутатор 3 предназначен для коммутации внещних контактов проверяемого узла 9, при этом входные контакты подключаются к выходам блока памяти 2 (к той части, где хранятся стимулы), выходные контакты подключаются к входам блока сравнения 4. Блок индикации 5 предназначен для индикации номеров неисправностей. Первый регистр контроля-6 и второй регистр контроля 7, которые в прототипе служат только для контроля по модулю 2 содержимого блока памяти, т.е. для контроля самого устройства, в предложенном устройстве предназначены для фиксации возможных неисправное тей (регистр контроля 6), для фиксации пррверенных неисправностей (регистр контроля 7). Блок управления 8 предназначен для организации работы всех узлов устройства. Устройство работает следующим образом. В исходном состоянии блок памяти 2, регистры контроля 6, 7 по командам с блока управления 8 установлены в нулевое состояние (цепи сброса не показаны). По команде с блока управления 8 тестовая информация (стимулы и эталоны) записываются в блок памяти 2. Стимулы из блока памяти 2 поступают через коммутатор 3 на входы проверяемого узла 9, а эталоны на первые входы блока сравнения 4. Реакция на тест проверяемого узла 9 через коммутатор 3 поступает на вторые входы блока сравнения 4. Управление работой коммутатора 3 осуществляется по сигнала. из блока управления 8. По результатам сравнения в зависимости от состояния проверяемого узла (исправен или неисправен) появится высокий потенциал на одном из вы.ходов блока сравнения 4. После подачи на входы проверяемого узла 9 очередного набора по ко.манде с блока управления 8 из блока ввода 1 начинает вводиться диагностическая информация, которая поступает на входы регистров контроля 6, 7. Диагностическая информация представляет позиционный код, длина которого (разрядность) равна общему количеству проверяемых неисправностей. Каждому номеру неисправности из списка неисправностей соответствует один разряд позиционного кода, причем только в разрядах позиционного кода, соответствующих проверяемым в данном тесте неисправностя.м, записаны «1. Каждому тестовому набору соответствует своя диагностическая информация. Во время проверки при подаче на входы проверяемого узла 9 теста на прямом выходе блока сравнения 4 появляется высокий потенциал, если на этом наборе неисправность в проверяемом узле 9 не проявляется. же неисправность проявляется, появится высокий потенциал на инверсном выходе бтока сравнения 4. Диагностическая информация записывается в регистры контроля 6 или 7; есди в данном тесте неисправность не проявляется - в регистр 7, . если проявляется - в регистр 6. После записи диагностической информации в регистры контроля 6 или 7 по команде из блока управления 8 в блок памяти 2 вводится очередной тест, который поступает затем на входы проверяемого узла 9, и начинается ввод диагностической информации данного теста. После прохождения всех тестов в,первом регистре контроля 6 установятся в «1 те разряды, которые соответствуют номерам неисправностей, проверяемых в «неисправных тестах. Во втором регистре контроля 7 установятся в «1 те разряды, которые соответствуют неисправностям, проверяемым в «исправных тес- тах («исправный тест - тест, в котором неисправность не проявляется, «неисправный тест - тест, в котором неисправность проверяемого узла проявляется). Таким образом, блок-сравнения 4 фиксирует наличие исправности (неисправности) проверяемого узла в каждом тесте, в . регистре 6 фиксируются возможные неисправности, в региctpe 7 фиксируются исключенные неисправности (неисправности, которые отсутствуют). Выходы регистров контроля 6, 7 подключены к блоку индикации 5, причем каждый индикаторный элемент (например светодиод) подключен к выходам одноименных разрядов регистров контроля 6, 7 и светится только в том случае, если на выходе первого регистра контроля 6 - высокий потенциал («1), а на соответствующем выходе второго регистра контроля 7 - низкий потенциал («О). После проверки будут светиться те индикаторные элементы, которые соответствуют неисправностям, проверяемым в «неисправных наборах, и отсутствующие в «исправных наборах. Зная номер

неисправности, по таблице неисправностей находят номер неисправного элемента и вид неисправности.

Таким образом, предложенное устройство не только контролирует исправность проверяемого узла, но и ускоряет поиск неисправности, обеспечивая диагностику неисправности проверяемого устройства (локализацию места и вида неисправности в проверяемом узле).

Формула изобретения

Устройство для контроля цифровых блоков, содержащее блок ввода, блок памяти, коммутатор, блок сравнения, блок индикации, блок управления, первый и второй регистры контроля, причем первый и второй выходы блока ввода соединены соответственно с первым входом блока памяти и с первыми входами первого и второго регистров контроля, первый и второй выходы блока управления соединены соответственно с входом блока ввода и со вторым входом блока памяти, первый и второй выходы

блока памяти соединены соотвегхтвенио с первым входом коммутатора с nepai iM входом блока сравнения, первый выход коммутатора соединен со вторым входом блока сравненпя, второй вход и второй выход коммутатора являются соответственно выходом и входом устройства, выходыпервого и второго регистров контроля соединены с входами блока индикации, отличающееся тем, что, с целью сокращения времени поиска неисправностей, первый п второй выходы блока сравнения соединены соответственно со вторыми входами регистров контроля, третий и четвертый выходы блока управ,ления соединены соответственно с третьим входом блока сравнения и с третьим входом коммутатора, третий выход блока ввода соединен со вторым входом блока унравления.

Источники информации, принятые во внимание при экспертизе:

1. Диагностика неисправностей логических схем вычислительных машин. . ..

1965,

15-- 132.

2. Авторское свидетельство СС( .N1 354415, кл. G 06 F 11/00, 1970.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков | 1978 |

|

SU746553A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU1012263A1 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1649544A2 |

| Устройство для контроля цифровых узлов | 1974 |

|

SU498619A1 |

| Устройство для контроля логических блоков | 1978 |

|

SU734694A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1247898A2 |

| Устройство для диагностики неисправностей цифровых блоков | 1981 |

|

SU1024925A1 |

| Устройство для тестового диагностирования логических блоков | 1976 |

|

SU661552A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для контроля и диагностики дискретных объектов | 1980 |

|

SU942025A1 |

Авторы

Даты

1978-05-15—Публикация

1975-07-18—Подача