112

Изобретение относится к вычихшиг тельной технике и может быть использовано для вычисления функции А/ Б + (1-1)4, i I-VN, при заданных Б, U и N, в частности для генерации адресов объектов, регулярно распо ложенных в памяти, по заданной базе (адресу первого объекта) и шагу, с которым следует объекты в памяти.

Цель изобретения - повьшение быстродействия ,

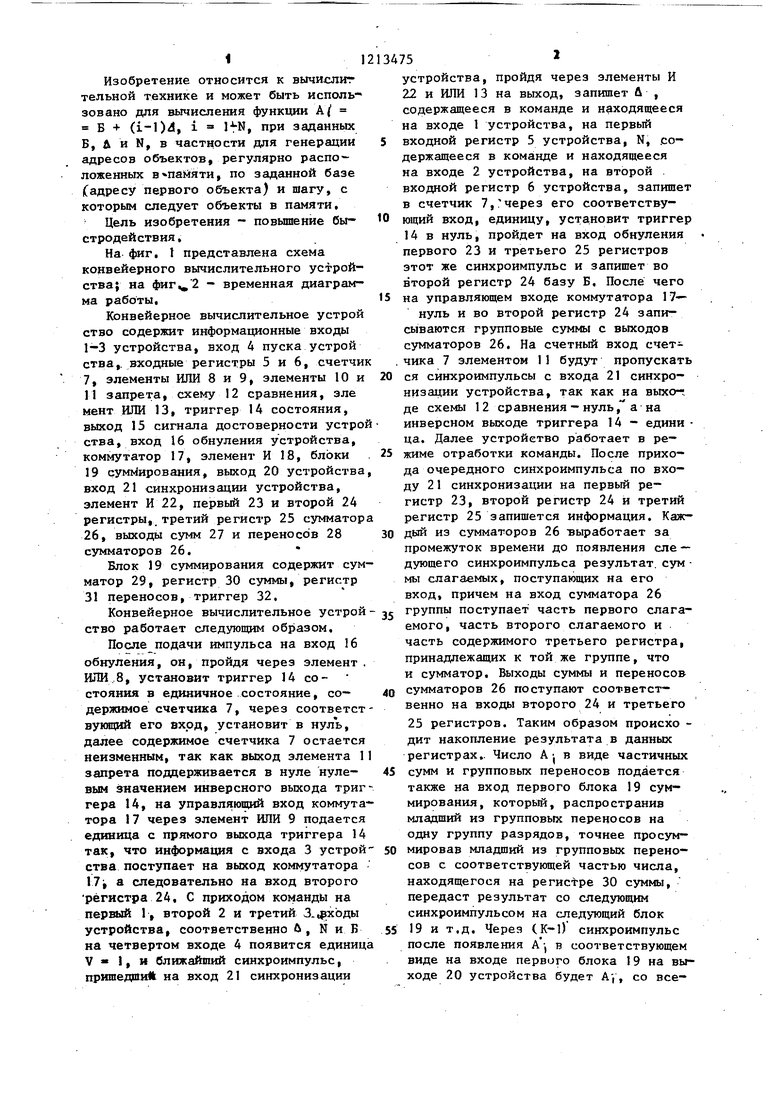

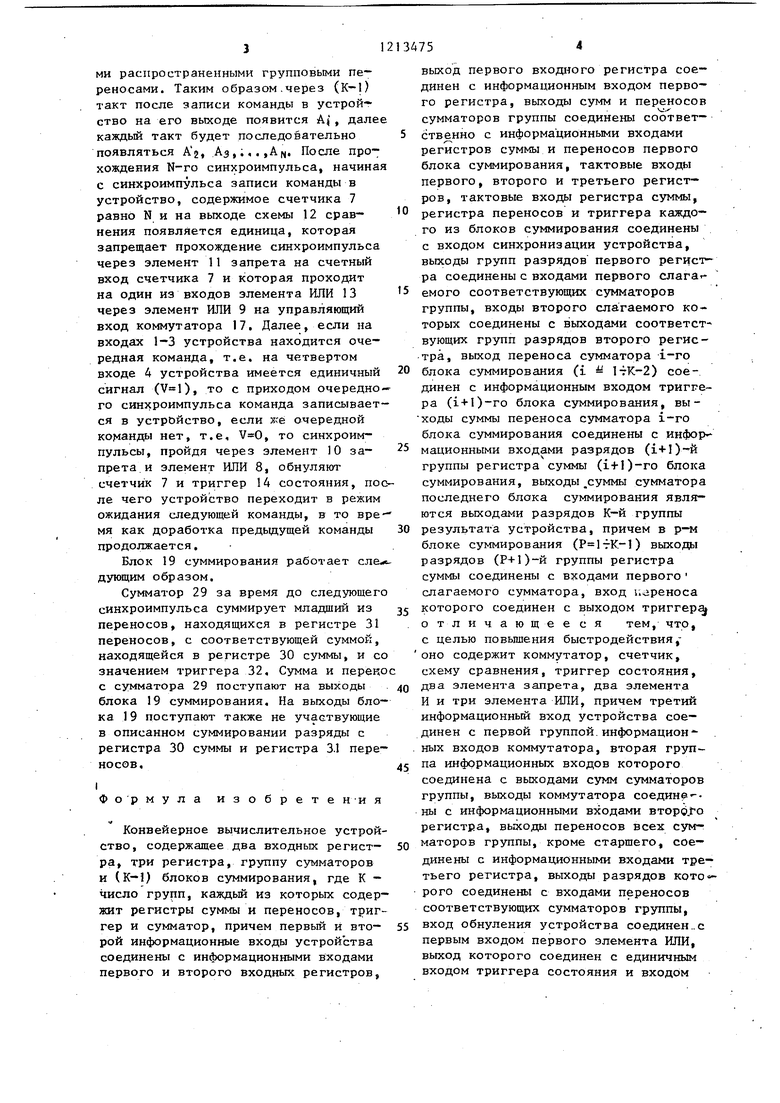

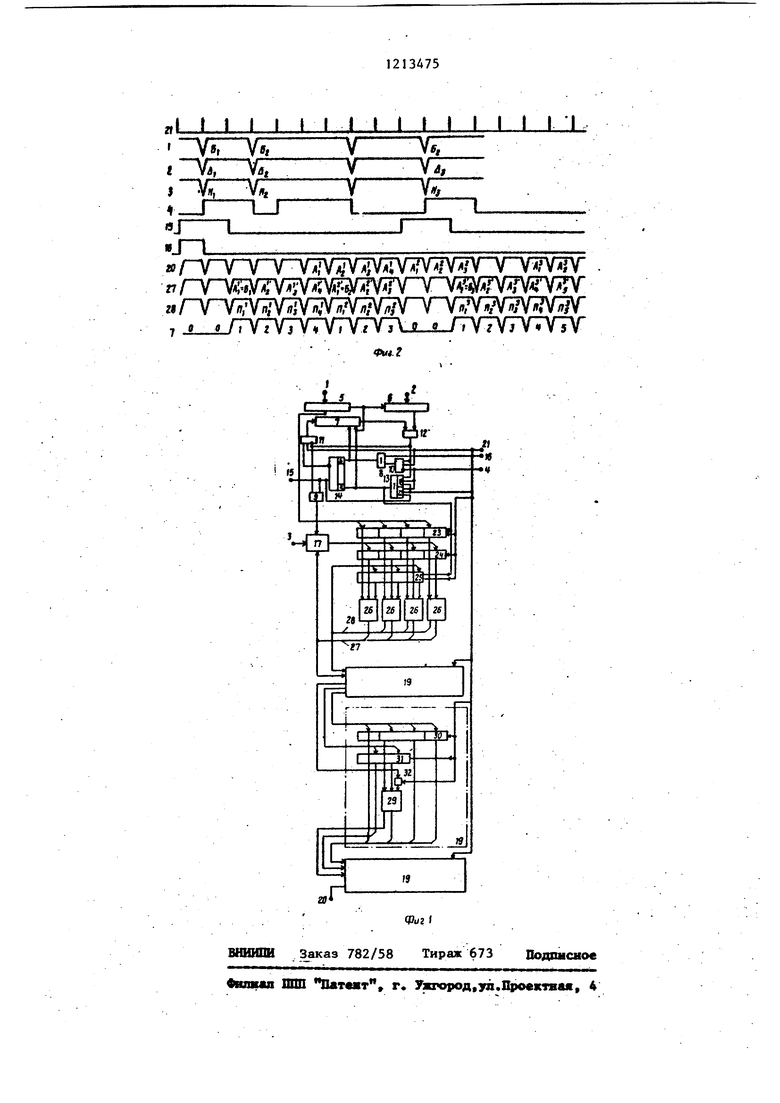

На фиг. 1 представлена схема конвейерного вычислительного устройства; на фиг ,, 2 - временная диаграмма работы.

Конвейерное вычислительное устрой ство содержит информационные входы 1-3 устройства, вход 4 пуска устрой ства,. входные регистры 5 и 6, счетчик 7, элементы ИЛИ 8 и 9, элементы 10 и 11 запрета, схему 12 сравнения, эле мент ИЛИ 13, триггер 14 состояния, выход 15 сигнала достоверности устрой ства, вход 16 обнуления устройства, коммутатор 17, элемент И 18, блоки 19 суммирования, выход 20 устройства, вход 21 синхронизации устройства, элемент И 22, первый 23 и второй 24 регистры, третий регистр 25 сумматора 26, выходы сумм 27 и переносов 28 сумматоров 26.

Блок 19 суммирования содержит сумматор 29, регистр 30 суммы, регистр 31 переносов, триггер 32,

Конвейерное вычислительное устрой - ство работает следующим образом.

После подачи импульса на вход 16 обнуления, он, пройдя через элемент, ИЛИ 8, установит триггер 14 состояния в единичное состояние, содержимое счетчика 7, через соответст- вунлций его вход, установит в нул ь, далее содержимое счетчика 7 остается неизменным, так как выход элемента 11 запрета поддерживается в нуле нулевым значением инверсного выхода триггера 14, на управляющий вход коммутатора I7 через элемент Ш1И 9 подается единица с прямого выхода триггера 14 так, что информация с входа 3 устройства поступает на выход коммутатора t7i а следовательно на вход второго регистра 24, С приходом команды на первый 1, второй 2 и третий З.хЬды устройства, соответственно U, N и Б на четвертом входе 4 появится единица V « I, и ближайший синхроимпульс, пришедший на вход 21 синхронизации

75

устройства, пройдя через элементы И 22 и ИЛИ 13 на выход, запишет U , содержащееся в команде и находящееся на входе 1 устройства, на первый

входной регистр 5 устройства, N, содержащееся в команде и находящееся на входе 2 устройства, на второй входной регистр 6 устройства, запишет в счетчик 7, через его соответствующий вход, единицу, установит триггер 14 в нуль, пройдет на вход обнуления первого 23 и третьего 25 регистров этот же синхроимпульс и запишет во второй регистр 24 базу Б, После чего

на управляющем входе коммутатора 17-

нуль и во второй регистр 24 записываются групповые суммы с выходов сумматоров 26, На счетный вход счет- чика 7 элементом 11 будут пропускать

ся синхроимпульсы с входа 21 синхронизации устройства, так как на выхо-; де схемы 12 сравнения - нуль, а на инверсном выходе триггера 14 - едини ца. Далее устройство работает в режиме отработки команды. После прихода очередного синхроимпульса по входу 21 синхронизации на первый регистр 23, второй регистр 24 и третий регистр 25 запишется информация. Каждый из сумматоров 26 выработает за промежуток времени до появления еле - д тещего синхроимпульса результат, сум мы слагаемых, поступающих на его вход, причем на вход сумматора 26

группы поступает часть первого слагаемого, часть второго слагаемого и часть содержимого третьего регистра, принадлежащих к той же группе, что и сумматор. Выходы суммы и переносов

сумматоров 26 поступают соответственно на входы второго 24 и третьего

25 регистров. Таким образом происхо - дит накопление результата в данных регистрах,. Число AJ в виде частичных

сумм и групповых переносов подается также на вход первого блока 19 суммирования, который, распространив младший из групповых переносов на одну группу разрядов, точнее просум-

мировав младший из групповых переносов с соответствующей частью числа, находящегося на регистре 30 суммы, передаст результат со следующим синхроимпульсом на следующий блок

19 и т.д. Через (К-1) синхроимпульс после появления А в соответствующем виде на входе первого блока 19 на выходе 20 устройства будет А ,, со всеми распространенными групповыми переносами. Таким образом.через (К-|) такт после записи команды в устрой- ство на его выходе появится Aj, далее каждьй такт будет последовательно появляться А г, АЗ,;..,AN. После прохождения N-ro синхроимпульса, начиная с синхроимпульса записи команды в устройство, содержимое счетчика 7 равно Ни на выходе схемы 12 срав- нения появляется единица, которая запрещает прохождение синхроимпульса через элемент 11 запрета на счетный вход счетчика 7 и которая проходит на один из входов элемента ИЛИ 13 через элемент ИЛИ 9 на управляющий вход коммутатора 17, Далее, если на входах 1-3 устройства находится очередная команда, т.е. на четвертом входе 4 устройства имеется единичный сигнал (), то с приходом очередного синхроимпульса команда записывается в устройство, если же очередной команды нет, т.е, , то синхроимпульсы, пройдя через элемент 10 за- прета.и элемент ИЛИ 8, обнуляют счетчик 7 и триггер 14 состояния, после чего устройство переходит в режим ожидания следующей команды, в то время как доработка предьщущей команды продолжается,

Блок 19 суммирования работает еледующим образом.

Сумматор 29 за время до следующего синхроимпульса суммирует младший из переносов, находящихся в регистре 31 переносов, с соответствующей суммой, находящейся в регистре 30 суммы, и со значением триггера 32. Сумма и переко с сумматора 29 поступают на выходы блока 19 суммирования. На вьгходы блока 19 поступают также не участвующие в описанном суммировании разряды с регистра 30 суммы и регистра 3.1 переносов.

I Фо рмула изобретен ия

Конвейерное вычислительное устройство, содержащее два входных регист- ра, три регистра, группу сумматоров и (К-1) блоков суммирования, где К - число групп, каждьй из которых содержит регистры суммы и переносов, триггер и сумматор, причем первьй и вто- рой информационные входы устройства соединены с информационными входами первого и второго входных регистров,

выход первого вход1 ого регистра соединен с информационным входом первого регистра, выходы сумм и переносов сумматоров группы соединены соответственно с информационными входами регистров суммы и переносов первого блока суммирования, тактовые входы первого, второго и третьего регистров, тактовые входы регистра суммы, регистра переносов и триггера каждого из блоков суммирования соединены с входом синхронизации устройства, выходы групп разрядов первого регистра соединены с входами первого слагат- емого соответствующих сумматоров группы, входы второго слагаемого которых соединены с выходами соответствующих групп разрядов второго регистра, выход переноса сумматора 1-го блока суммирования (i 1тК-2) соединен с информационным входом триггера (i + I)-ro блока суммирования, выХОДЫ суммы переноса сумматора i-ro блока суммирования соединены с инфор мационными входами разрядов ()-й группы регистра суммы (i+l)-ro блока суммирования, выходы ,суммы сумматора последнего блока суммирования являются выходами разрядов К-и группы результата устройства, причем в р-м блоке суммирования (Р 1тК-1) выходы разрядов (Р+1)-й группы регистра суммы соединены с входами первого слагаемого сумматора, вход u ipeHoca которого соединен с выходом TpHrrepaj отличающееся тем, что, с целью повышения быстродействия ,оно содержит коммутатор, счетчик, схему сравнения, триггер состояния, два элемента запрета, два элемента И и три элемента ИЛИ, причем третий информационный вход устройства соединен с первой группой, информацион

ных входов коммутатора, вторая группа информационных входов которого соединена с выходами сумм сумматоров группы, выходы коммутатора соедини- ны с информационными входами второго регистра, выходы переносов всех сумматоров группы, кроме старшего, соединены с информационными входами третьего регистра, выходы разрядов рого соединены с входами переносов соответствующих сумматоров группы, вход обнуления устройства соединен..с первым входом первого элемента ИЛИ, выход которого соединен с единичным входом триггера состояния и входом

сброса счетчика, установочный вход которого соединен с тактовыми входами первого и второго входных регистров, нулевым входом триггера состояния и входами обнуления первого и третьего регистров, единичный выход триггера состояния соединен с выходом отсут - ствия ошибки и с первым входом второго элемента ИЛИ, выход которого соединен с управляющим входом коммутатора второй вход первого элемента ИЛИ соединен с выходом первого элемента запрета, первый информационный вход которого соединен с первым вхо дом первого элемента И, вторым входом второго элемента ИЛИ, управляющим входом второго элемента запрета и с выходом схемы сравнения, первая

подключен к входу синхронизации устройства, вход пуска которого соединен с управляющим входом перво5 го элемента запрета, третьим входом первого элемента И и вторым входом второго элемента И, третий вход которого соединён с единичным выходом триггера состояния, нулевой вход

10 которого соединен с выходом третьего элемента ИЛИ, первый и второй входы которого соединены с выходами соответ- ствующих элементов И, выходы всех групп разрядов, кроме (1+1)-й, регист 15 ра суммы i-ro блока суммирования соединены у с информационными входами соответствующих групп разрядов ре- гистра суммы.(i+l)-ro блока суммирования, выходы; групп разрядов с пер

и вторая Группы входов которой соеди- 20 вой по (К-О-ю регистра суммы последнего блока суммирования являются вьг ходами соответствующих групп разрядов результата устройства, выходы регистра переносов, кроме младЩего,

25 i-ro блока суммирований соединены с соответствующими информационными вхо-- дами регистра переносов (i+I)-ro блока суммирования, причем в блоке суммирования младший выход ре30 гистра переносов соединен с входом второго слагаемого сумматора..

нены соответственно с выходом второго входного регистра и с выходами разрядов счетчика, счетный вход которого соединен с выходом второго элемента запрета, первый и второй информационные входы ко торого соединены соответственно с нулевым выхо- дом триггера состояния и с вторым информационным входом первого элемента .запрета, который соединен с вторым входом первого элемента И и с первым входом второго элемента И и

подключен к входу синхронизации устройства, вход пуска которого соединен с управляющим входом первого элемента запрета, третьим входом первого элемента И и вторым входом второго элемента И, третий вход которого соединён с единичным выходом триггера состояния, нулевой вход

которого соединен с выходом третьего элемента ИЛИ, первый и второй входы которого соединены с выходами соответ- ствующих элементов И, выходы всех групп разрядов, кроме (1+1)-й, регист ра суммы i-ro блока суммирования соединены у с информационными входами соответствующих групп разрядов ре- гистра суммы.(i+l)-ro блока суммирования, выходы; групп разрядов с пер

1 t 1 I I t I I I I t t I I t I I

rY YnrY V7 W ijrarJn rr

arr Vli YliiVliN i

7 jL jL/rVTVTVTVTYrVTVjL a.JTV7V7VTV

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство вычисления функции @ @ с исправлением ошибок | 1984 |

|

SU1288690A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Многофункциональный генератор двоичных последовательностей | 1981 |

|

SU991397A1 |

| Устройство параллельной обработки видеоинформации | 1989 |

|

SU1651299A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1985 |

|

SU1315969A1 |

| Устройство для реализации временных булевых функций | 1985 |

|

SU1290346A1 |

| Устройство для умножения | 1985 |

|

SU1278838A1 |

| Устройство для выполнения операций умножения и деления | 1980 |

|

SU955038A1 |

Изобретение относится к области вычислительной техники и может быть использовано для генерации адресов о бъектов по заданным базе и шагу. Целью изобретения является повьшение быстродействия устройства. Это дости- гается тем, что конвейерное вычислительное устройство, содержащее регистры, блоки суммирования, содержит коммутатор, счетчик, схему сравнения, триггер, два элемента И, два элемента ИЛИ и два элемента запр ета с соответ ствующими связями. 2 ил. § W с ю со 4ib сл

ВНШШИ Заказ 782/58 Тираж 673 Подписное шшш ШШ Патвшт, г. ,уп.Про«ктвая, 4

| Конвейерный сумматор | 1982 |

|

SU1067499A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Конвейерное устройство для выполне-Ния АРифМЕТичЕСКиХ ОпЕРАций НАдМНОжЕСТВОМ чиСЕл | 1979 |

|

SU849205A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-02-23—Публикация

1984-03-26—Подача