Изобретение относится к электронным приборам времени и может быть иснользо- вано в балансовых электронно-механических часах для поддержания незатухающих колебаний балансового осциллятора.

Целью изобретения является повышение точности хода часов за счет стабилизации амплитуды колебаний баланса, снижения средней потребляемой мощности и микроминиатюризации устройства.

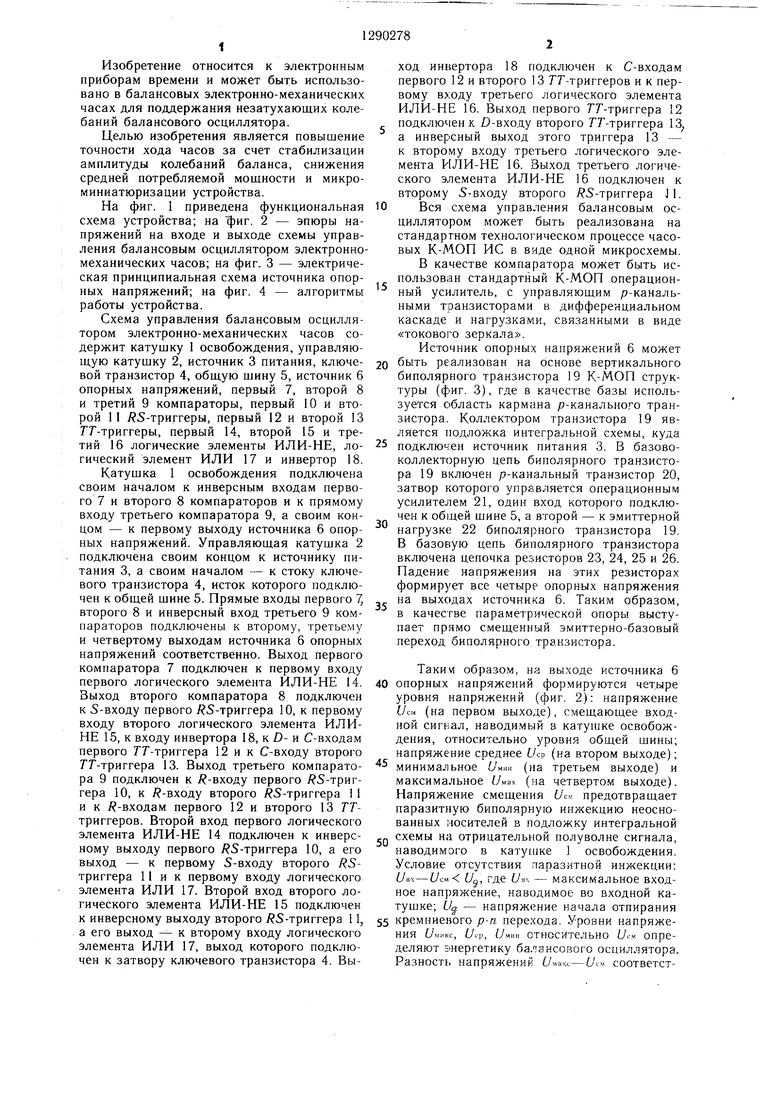

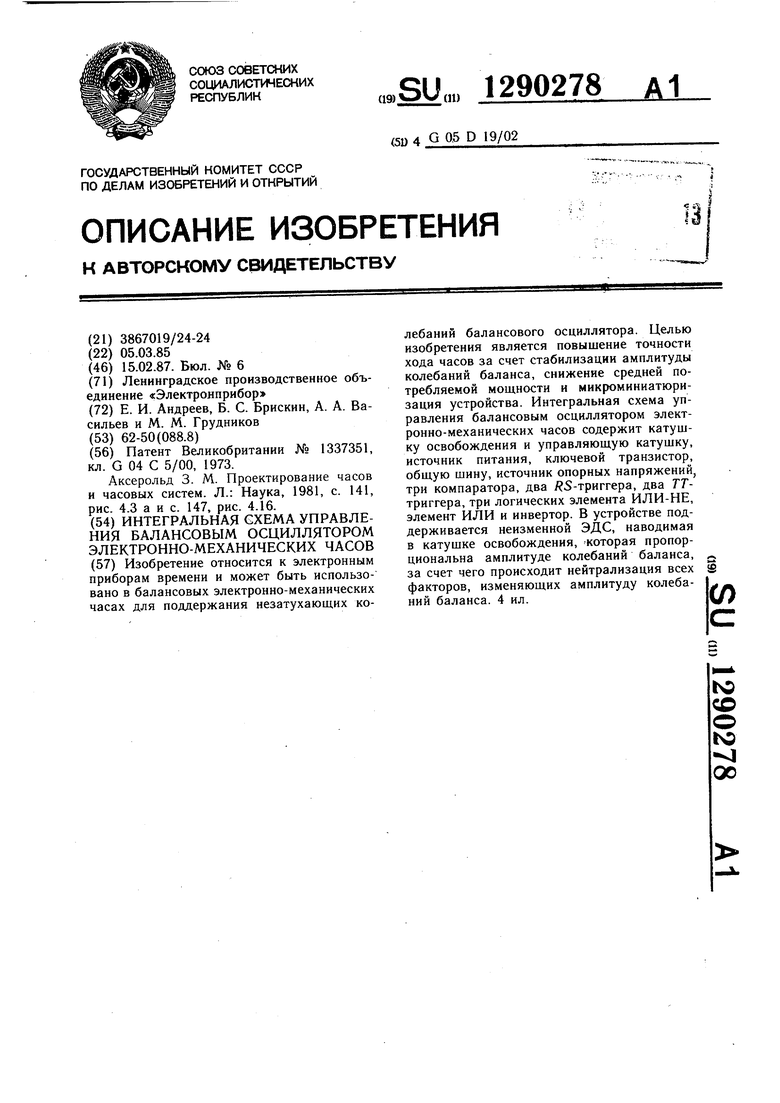

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - эпюры напряжений на входе и выходе схемы управления балансовым осциллятором электронно- механических часов; на фиг. 3 - электрическая принципиальная схема источника опорных напряжений; на фиг. 4 - алгоритмы работы устройства.

Схема управления балансовым осциллятором электронно-механических часов содержит катущку 1 освобождения, управляющую катушку 2, источник 3 питания, ключевой транзистор 4, общую щину 5, источник 6 опорных напряжений, первый 7, второй 8 и третий 9 компараторы, первый 10 и второй 11 / 5-триггеры, первый 12 и второй 13 ГГ-триггеры, первый 14, второй 15 и третий 16 логические элементы ИЛИ-НЕ, логический элемент ИЛИ 17 и инвертор 18.

Катушка 1 освобождения подключена своим началом к инверсным входам первого 7 и второго 8 компараторов и к прямому входу третьего компаратора 9, а своим концом - к первому выходу источника 6 опорных напряжений. Управляющая катущка 2 подключена своим концом к источнику питания 3, а своим началом - к стоку ключевого транзистора 4, исток которого подключен к общей щине 5. Прямые входы первого 1, второго 8 и инверсный вход третьего 9 компараторов подключены к второму, третьему и четвертому выходам источника 6 опорных напряжений соответственно. Выход первого компаратора 7 подключен к первому входу первого логического элемента ИЛИ-НЕ 14. Выход второго компаратора 8 подключен к S-входу первого / 5-триггера 10, к первому входу второго логического элемента ИЛИ- НЕ 15, к входу инвертора 18, к D- и С-входам первого ГГ-триггера 12 и к С-входу второго ГГ-триггера 13. Выход третьего компаратора 9 подключен к / -входу первого / 5-триг- гера 10, к / -входу второго j S-триггера 1 1 и к У -входам первого 12 и второго 13 П- триггеров. Второй вход первого логического элемента ИЛИ-НЕ 14 подключен к инверсному выходу первого / 5-триггера 10, а его выход - к первому S-входу второго RS- триггера 11 и к первому входу логического элемента ИЛИ 17. Второй вход второго логического элемента ИЛИ-НЕ 15 подключен к инверсному выходу второго 5-триггера 11, а его выход - к второму входу логического элемента ИЛИ 17, выход которого подключен к затвору ключевого транзистора 4. Вы

0

5

0

5

ход инЕ(ертора 18 подключен к С-входам первого 12 и второго 13 ГГ-триггеров и к первому входу третьего логического элемента ИЛИ-НЕ 16. Выход первого ГГ-триггера 2 подключена D-входу второго ГГ-триггера 13 а инверсный выход этого триггера 13 - к второму входу третьего логического элемента ИЛИ-НЕ 16. Выход третьего логического элемента ИЛИ-НЕ 16 подключен к второму S-входу второго S-триггера J1.

Вся схема управления балансовым осциллятором может быть реализована на стандартном технологическом процессе часовых К-МОП ИС в виде одной микросхемы.

В качестве компаратора может быть использован стандартный К-МОП операционный усилитель, с управляющим р-каналь- ными транзисторами в дифференциальном каскаде и нагрузками, связанными в виде «токового зеркала.

Источник опорных напряжений 6 может быть реализован на основе вертикального биполярного транзистора 19 К-МОП структуры (фиг. 3), где в качестве базы используется область кармана р-канального транзистора. Коллектором транзистора 19 является подложка интегральной схемы, куда подключен источник питания 3. В базово- коллекторную цепь биполярного транзистора 19 включен р-канальный транзистор 20, затвор которого управляется операционным усилителем 21, один вход которого подключен к об1дей шине 5, а второй - к э.миттерной нагрузке 22 биполярного транзистора 19. В базовую цепь биполярного транзистора вк.лючена цепочка резисторов 23, 24, 25 и 26. Падение напряжения на этих резисторах формирует все четыре опорных напряжения на выходах источника 6. Таким образом, в качестве параметрической опоры выступает прямо смещенный эмиттерно-базовый переход биполярного, транзистора.

Таким образом, на выходе источника 6

опорных напряжений формируются четыре уровня напряжений (фиг. 2): напряжение UfM (на первом выходе), смещающее входной сигнал, наводи.мый в катушке освобождения, относительно уровня общей шины; напряжение среднее Уср (на втором выходе);

минимальное б мил (на третьем выходе) и максимальное (Умах (на четвертом выходе). Напряжение смещения (Ус..- предотвращает паразитную биполярную инжекцию неоснованных носителей в подложку интегральной

схемы на отрицательной полуволне сигнала, наводимого в катушке 1 освобождения. Условие отсутствия паразитной инжекции: t/Bx-(Уем {Jg, где t/as - максимальное входное напряжение, наводимое во входной катушке; t/ - напряжение начала отпирания

кремниевого р-п перехода. Уровни напряжения О мнкс, /7fp, Умнн относительно i/см определяют энергетику балансового осциллятора. Разность напряжения (Умаю. - соответствует уровню стабилизируемой ЭДС, наводимой магнитной системой баланса в катушке 1 освобождения. Уровень стабилизируемой ЭДС однозначно связан с амплитудой баланса, которая, следовательно, тоже стабилизируется системой (t/макс-Ucp - напряжение, определяющее ширину основного рабочего импульса в управляющей катуш- не 2 балансового осциллятора, U«m-t/см - напряжение, определяющее порог запуска балансового осциллятора).

В дальнейшем изложении отсчет уровней напряжения на катушке освобождения и входах компараторов ведется от уровня (/см, принимая его за нулевой уровень.

Качественное функционирование схемы управления балансовым осциллятором иллюстрируется эпюрами напряжений (фиг. 2) на начальных концах катушки 1 освобождения (кривая 1) и управляющей катущки 2 (кривая 2). Если колебательная система выведена из состояния равновесия и в катушке 1 освобождения навелась ЭДС, превышающая порог срабатывания компаратора 8 напряжения минимального уровня, то на управляющей катушке 2 формируется импульс напряжения, длительность которого

вень напряжения. При этом на инверсном выходе / 5-триггера 10 устанавливается «нулевой уровень напряжения (), на выходах логических элементов ИЛИ- НЕ 14 и 15 тоже «нулевой уровень напря женин. На входы ТТ-триггеров 12 и 13 приходит сигнал сдвига, а на выходе логического элемента ИЛИ-НЕ 16 - сигнал «О. Вне зависимости от состояния / 5-тригге- ра 11 на выходе элемента ИЛИ 17 «нулевой

10 уровень напряжения. Транзистор 4 заперт и импульс в управляющей катушке 2 отсутствует. Если баланс выведен из состояния покоя и ЭДС, наводимая в катушке 1 освобождения, в результате колебания относительно положения равновесия превышает порог срабатывания i/мии, то компаратор 8 возбуждается, и на его выходе появляется «нулевой уровень напряжения. В зависимости от состояния / 5-триггера 11 сигнал возбуждения компаратора 8 может либо пройти, либо не пройти на выход логического элемента ИЛИ-НЕ 15. Если , на выходах логических элементов ИЛИ-НЕ 15 и ИЛИ 17 устанавливаются «единичные уровни напряжения и длительность импульса напряжения в управляющей катушке 2 становится равной

15

20

соответствует длительности возбуждения 25 времени возбуждения компаратора 8 (;„-1)

30

35

40

компаратора 8 /ц-ti. Энергия механического импульса, форм.ируемого магнитной системой баланса, значительно превосходит энер- гиб, отбираемую часовым механизмом, и амплитуда колебаний баланса непрерывно возрастает. С возрастанием амплитуды колебаний баланса растет и ЭДС. наводимая в катушке 1 освобождения. Когда ЭДС становится равной уровню срабатывания (Умакс компаратора 9, длительность импульса напряжения на управляющей катушке 2 становится равной tz ()- Затем схема переходит в режим формирования стационарного импульса . В виду синусоидальной формы ЭДС в катушке 1 освобождения и небольшой разности порогов срабатывания (t/макс-(Уср) компараторов 7 и 8 характеристика регулирования амплитуды носит нелинейный характер. Система регулирования амплитуды носит астатический характер, т. е. воздействие всегда перекомпенсирует изменение амплитуды колебаний баланса. Схема управления балансовым осциллятором имеет четыре ступени формирования длительности импульса напряжения в управляющей катушке, что позволяет ей быстро адаптироваться к изменению нагрузки на минутной оси часового механизма. Работу схемы управления балансовым осциллятором иллюстрирует алгоритм (фиг. 4).

Устройство функционирует следующим образом.

Если , то на выходах логических элементов ИЛИ-НЕ 15 и ИЛИ 17 «нулевой уровень напряжения, транзистор 4 заперт и импульс напряжения на управляющую катушку 2 не поступает. При этом, однако, производится установка 7Т-триггера 12 в «единичное состояние () и сдвиг информации с выхода первого 7Г-триггера на выход второго ГГ-триггера 13 (). После двукратного подряд повторения таких сигналов в катущке 1 освобождения на выходе элемента ИЛИ-НЕ 16 устанавливается «единичный уровень напряжения и RS- триггер 11 устанавливается в состояние . После этого третий и все последующие аналогичные сигналы в катушке освобождения обязательно вызывают импульсы напряжения на управляющей катущке. Когда ЭДС, наводимая в катушке 2 освобождения, превысит порог срабатывания компаратора 9 ({Увх(/макс), последний возбуждается. На выходе компаратора 9 появляется «единичный уровень напряжения, который прерывает формирование импульса в катушке 2, на вливает 5-триггер 11 в состояние , а 7 7 -триггеры 12 и 13 в состояние и . ТТ-триггеры 12 и 13совмест- JQ но с элементами 18 и 16 выполняют функцию сдвигового регистра. На вход сдвигового регистра непрерывно записывается информация с выхода компаратора 8 и эта информация стирается в момент возбуждения компаратора 9. Такая схема не позволяет сразу же после самого узкого импульса tu-/3 перейти к самому широкому импульсу , что обеспечивает плавность регулирования амплитуды баланса и невозможность его

45

При отсутствии ЭДС наводимой в катуш- ке 1 освобождения, баланс в состоянии покоя на выходах компараторов 7 и 8 «единичный, а на выходе компаратора 9 «нулевой уро

вень напряжения. При этом на инверсном выходе / 5-триггера 10 устанавливается «нулевой уровень напряжения (), на выходах логических элементов ИЛИ- НЕ 14 и 15 тоже «нулевой уровень напряженин. На входы ТТ-триггеров 12 и 13 приходит сигнал сдвига, а на выходе логического элемента ИЛИ-НЕ 16 - сигнал «О. Вне зависимости от состояния / 5-тригге- ра 11 на выходе элемента ИЛИ 17 «нулевой

0 уровень напряжения. Транзистор 4 заперт и импульс в управляющей катушке 2 отсутствует. Если баланс выведен из состояния покоя и ЭДС, наводимая в катушке 1 освобождения, в результате колебания относительно положения равновесия превышает порог срабатывания i/мии, то компаратор 8 возбуждается, и на его выходе появляется «нулевой уровень напряжения. В зависимости от состояния / 5-триггера 11 сигнал возбуждения компаратора 8 может либо пройти, либо не пройти на выход логического элемента ИЛИ-НЕ 15. Если , на выходах логических элементов ИЛИ-НЕ 15 и ИЛИ 17 устанавливаются «единичные уровни напряжения и длительность импульса напряжения в управляющей катушке 2 становится равной

5

0

5 времени возбуждения компаратора 8 (;„-1)

5 времени возбуждения компаратора 8 (;„-1)

0

5

0

5

Если , то на выходах логических элементов ИЛИ-НЕ 15 и ИЛИ 17 «нулевой уровень напряжения, транзистор 4 заперт и импульс напряжения на управляющую катушку 2 не поступает. При этом, однако, производится установка 7Т-триггера 12 в «единичное состояние () и сдвиг информации с выхода первого 7Г-триггера на выход второго ГГ-триггера 13 (). После двукратного подряд повторения таких сигналов в катущке 1 освобождения на выходе элемента ИЛИ-НЕ 16 устанавливается «единичный уровень напряжения и RS- триггер 11 устанавливается в состояние . После этого третий и все последующие аналогичные сигналы в катушке освобождения обязательно вызывают импульсы напряжения на управляющей катущке. Когда ЭДС, наводимая в катушке 2 освобождения, превысит порог срабатывания компаратора 9 ({Увх(/макс), последний возбуждается. На выходе компаратора 9 появляется «единичный уровень напряжения, который прерывает формирование импульса в катушке 2, на вливает 5-триггер 11 в состояние , а 7 7 -триггеры 12 и 13 в состояние и . ТТ-триггеры 12 и 13совмест- Q но с элементами 18 и 16 выполняют функцию сдвигового регистра. На вход сдвигового регистра непрерывно записывается информация с выхода компаратора 8 и эта информация стирается в момент возбуждения компаратора 9. Такая схема не позволяет сразу же после самого узкого импульса tu-/3 перейти к самому широкому импульсу , что обеспечивает плавность регулирования амплитуды баланса и невозможность его

5

«забалтывания. В то же время такая схема позволяет легко перенести «ачало формирования импульса на уровень L MHH в момент запуска балансового осциллятора. Схема стабилизации амплитуды баланса с помощью четырех градаций длительности импульсов, каждый из которых может еще изменяться в широких пределах, позволяет отказаться от стабилизации амплитуды напряжения импульса в управляющей обмотке. Это приводит к повыщению КПД схемы и, как следствие, увеличению времени работы часов без смены батареи. При этом ресурс батареи возрастает вдвое. Большой коэффициент усиления схемы за счет использования компараторов и астатический принцип регулирования амплитуды баланса позволяют улучшить степень стабилизации амплитуды и тем самым повысить точность хода часов в условиях дестабилизирующих факторов. Схема управления не содержит конденсаторов большой емкости и может быть реализована в виде одной микросхемы на стандартном технологическом процессе часовых К-МОП-ИС.

Формула изобретения

Интегральная схема управления балансовым осциллятором электронно-механических часов, содержащая катушку освобождения и последовательно соединенные управляющую катушку, коммутирующий транзистор и общую шину, отличающаяся тем, что, с целью повышения точности хода часов за счет стабилизации амплитуды колебаний баланса, снижения средней потребляемой мощности и микроминиатюризации устройства, в него введены источник опорных напряжений с четырьмя выходами, последовательно соединенные первый компаратор, первый элемент ИЛИ-НЕ и элемент ИЛИ,

выход которого подключен к затвору коммутирующего транзистора, последовательно соединенные второй компаратор и второй элемент ИЛИ-НЕ, инверсный выход которого соединен с вторым входом элемента ИЛИ, введены также последовательно соединенные инвертор и третий элемент ИЛИ-НЕ, а также первый и второй / 5-триггеры, первый и второй 7Г-триггеры и третий компаратор, прямой вход которого соединен с инверсным входом второго компаратора и одновременно подключен через катушку освобождения к первому выходу источника опорных напряжений и инверсному входу первого компаратора, прямой вход которого соединен с вторым выходом источника опорных напряжений, третий выход которого соединен с прямым входом второго компаратора, выход которого подключен к 5-входу первого / 5-триггера, входу инвертора, и /)-входу и С-входу первого ТТ-триггера и С-входу

0 второго 2Т-триггера, четвертый выход источника опорных напряжений соединен с инверсным входом третьего компаратора, выход которого подключен к / -Бходу первого RS- триггера, к -входу второго 5-триггера, к / -входу первого ГГ-триггера и / -входу

5 второго 7Т-триггера, инверсный С-вход которого подключен к инвертору, а -вход - к выходу пер вого ТТ-триггера, инверсный С-вход которого также подключен к выходу инвертора, второй вход первого элемента ИЛИ-НЕ соединен с инверсным выходом первого / 5-триггера, а выход первого элемента ИЛИ-НЕ соединен с первым S-входом второго Я5-триггера, второй S-вход которого соединен с выходом третьего элемента ИЛИ-НЕ, второй вход которого подключен

,. к инверсному выходу второго ГГ-триггера, инверсный выход второго / 5-триггера соединен с вторым входом второго элемента ИЛИ- НЕ.

0

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения самовозбуждения блоков привода электронно-механических балансных часов | 1986 |

|

SU1365043A1 |

| Схема магнитоэлектрического привода балансового осциллятора | 1974 |

|

SU503204A1 |

| Импульсный понижающий стабилизатор постоянного напряжения | 1990 |

|

SU1786477A1 |

| Устройство имитации движения баланса электронно-механических часов | 1984 |

|

SU1249474A1 |

| ДВУХТАКТНЫЙ ТРАНЗИСТОРНЫЙ ИНВЕРТОР | 1993 |

|

RU2046527C1 |

| Элемент памяти | 1989 |

|

SU1642521A2 |

| Способ стабилизации амплитуды колебаний балансового осциллятора с магнитоэлектрическим приводом | 1982 |

|

SU1138784A1 |

| Элемент памяти | 1987 |

|

SU1474736A1 |

| Устройство для измерения амплитуды колебаний баланса механических часов | 1985 |

|

SU1254430A1 |

| СИСТЕМА ВОЗБУЖДЕНИЯ СИНХРОННОГО ГЕНЕРАТОРА С УПРАВЛЯЕМОЙ ДВУНАПРАВЛЕННОЙ ВНЕШНЕЙ ФОРСИРОВКОЙ | 2021 |

|

RU2781107C1 |

Изобретение относится к электронным приборам времени и может быть использовано в балансовых электронно-механических часах для поддержания незатухающих колебаний балансового осциллятора. Целью изобретения является повышение точности хода часов за счет стабилизации амплитуды колебаний баланса, снижение средней потребляемой мощности и микроминиатюризация устройства. Интегральная схема управления балансовым осциллятором электронно-механических часов содержит катущ- ку освобождения и управляющую катушку, источник питания, ключевой транзистор, общую шину, источник опорных напряжений, три компаратора, два / 5-триггера, два ТТ- триггера, три логических элемента ИЛИ-НЕ, элемент ИЛИ и инвертор. В устройстве поддерживается неизменной ЭДС, наводимая в катушке освобождения, которая пропорциональна амплитуде колебаний баланса, за счет чего происходит нейтрализация всех факторов, изменяющих амплитуду колебаний баланса. 4 ил. ;о (Л 1C со О 1C 00

Л

10/

КС

UcM % О

A

8ы1.

UHUH /

X

t2

iz

i4

/

J

iiu t3)

te.3

Ла

ш 1коднвгоимп.не

, 1

-

Нет

. /

JM

f

Оышного инп. нет

1

H-SZSSItAiZ.

т

f

4-Д-% г- CZ

//ш.х «J-/

I Qt-Q.u.- 1

- состояние dd/xoffa Qi

Л- триеге/ а 12 / rrpe /di/ще/

| Индукционная печь для непрерывной плавки окислов | 1986 |

|

SU1337351A2 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| М | |||

| Проектирование часов и часовых систем | |||

| Л.: Наука, 1981, с | |||

| Топливник с глухим подом | 1918 |

|

SU141A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Раздвижной паровозный золотник со скользящими по его скалке поршнями и упорными для них шайбами | 1922 |

|

SU147A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-02-15—Публикация

1985-03-05—Подача