Ј

Јъ

vl

00 0

114747

Изобретение относится к автомата- ке и вычислительной технике и может быть использовано в устройствах с сохранением информации при перерывах напряжения питания.

Цель изобретения - увеличение быстродействия элемента памяти.

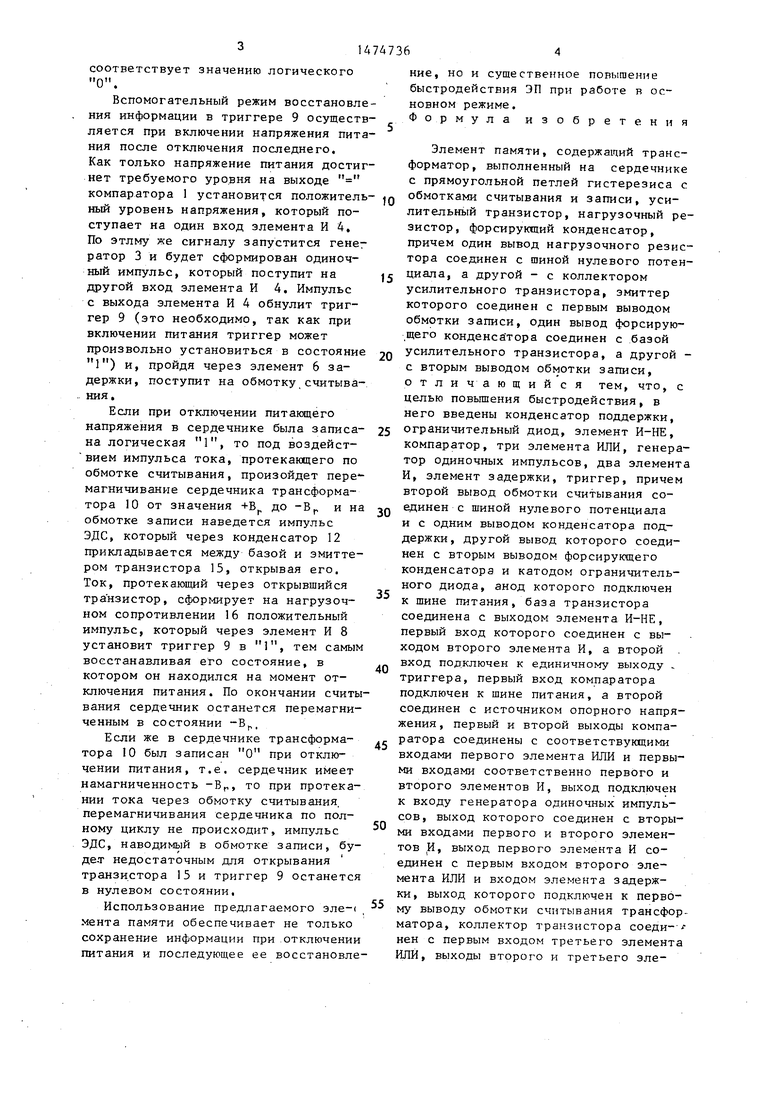

На чертеже представлена функциональная схема элемента памяти.tO

Элемент памяти содержит компаратор 1, первый 2 элемент ИЛИ, генератор 3 одиночных импульсов, первый 4 и второй 5 элементы И, элемент 6 задержки, второй 7 и третий 8 элементы 15 отключении напряжения питания. В ИЛИ, триггер 9, трансформатор 10, вы- любом случае напряжение на шине питапамяти. Смена информации (запись 1 или О) осуществляется по входам или .

Во вспомогательном режиме производится либо перезапись информации, хранящейся в триггере 9, в трансформатор 10 при отключении напряжения питания, либо восстановление информации в триггере 9 путем ее считывания с сердечника трансформатора 10 при включении питания.

Вспомогательный режим используется как при аварийном, так и плановом

| название | год | авторы | номер документа |

|---|---|---|---|

| Элемент памяти | 1989 |

|

SU1642521A2 |

| Элемент памяти | 1984 |

|

SU1265854A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| ТАЙМЕР С КОНТРОЛЕМ | 1990 |

|

RU2037872C1 |

| ФОТОПРИЕМНЫЙ ИНТЕГРАЛЬНЫЙ ЭЛЕМЕНТ ПАМЯТИ | 1993 |

|

RU2043665C1 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1990 |

|

SU1780487A1 |

| Триггер | 1990 |

|

SU1791850A1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 1980 |

|

SU852131A1 |

| Энергонезависимая ячейка памяти | 1979 |

|

SU845287A1 |

| Генератор импульсов переменной амплитуды | 2017 |

|

RU2647700C1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах с сохранением информации при перерывах напряжения питания. Цель изобретения- увеличение быстродействия элемента памяти. Поставленная цель достигается за счет введения компаратора 1, трех элементов ИЛИ 2,7,8, двух элементов И 4,5, генератора 3, конденсатора 13, диода 14, элемента И-НЕ 11, элемента задержки 6, триггера 9, что позволяет в режиме чтения-записи использовать в качестве элемента хранения информации триггер 9, а для сохранения информации при отключении питания используется трансформатор 10, сердечник которого имеет прямоугольную петлю гистерезиса. 1 ил.

полненный на сердечнике с прямоугольной петлей гистерезиса, с обмотками записи и считывания, элемент И-НЕ 11, форсирующий конденсатор 12, конденсатор 13 поддержки, ограничительный диод 14, усилительный транзистор 15, нагрузочный резистор 16. Здесь же показаны шина напряжения питания +ЕП, шина опорного напряжения Uon , входы записи Зп О и Зп 1 выходы элемента памяти Вых,0, Вых. Г

выходы компаратора:

, а также первый и второй равно и 4 - меньше.

Сигнал в виде положительного перепада напряжения на первом выходе компаратора появляется при +ЕП - 11ОЦ , когда, напряжение питания возрастает от 0 до Еп. Перепад напряжения на втором выходе i. компаратора появляется, когда напряжение питания, уменьшаясь от +ЕП до 0, стане равным иоп . Величина напряжения Uor) выбирается несколько меньше +ЕЛ.

В исходном состоянии (при нормальном напряжении питания) на выходе А элемента И-НЕ 11 - высокий потенциал, обусловленный уровнем логическог О с выхода элемента И 5. При этом транзистор 15 закрыт, с нагрузочного резистора 16 снимается сигнал логического О, конденсатор 13 заряжен до +Eh, диод 14 открыт и напряжение подано на эмиттер транзистора 15. Сердечник трансформатора находится состоянии Ва.

Элемент памяти может работать в двух режимах: основном и вспомогател

НОМ.

В основном режиме (при нормальном напряжении питания) информация хранится в триггере 9 и снимается с выходов Вых. 1 и Вых. О элемента

ния +Е уменьшается от +Е„

л у i-jt-л JJIUCLC; 1 f j i i и п ДО v/ И j

когда оно достигает величины U Uon , на выходе компаратора 1 появляется положительный перепад напряжения, Воздействие данного перепада напряжения через элемент ИЛИ 2 обеспечивает формирование импульса на выходе генератора 3 одиночных импульсов, который поступает на вход элемента И 5, подготовленный к срабатыванию уровнем логической 1 с выхода V компаратора 1. Импульс с выхода элемента И 5 поступает на первый вход элемента

И-НЕ 11.

Если в триггере 9 записана 1 (к моменту выключения напряжения),

5

0

е

0

то этот сигнал 1 будет подан на второй вход элемента И-НЕ 11, В результате элемент И-НЕ 11 сработает и сформирует отрицательный импульс, который поступает на базу транзистора 15, открывая его. Через обмотку записи трансформатора 10, открытый транзистор 15 и резистор 16 протекает импульс тока, который перемагничива- ет сердечник трансформатора 10 от исходного значения намагниченности -Вр до +ВГ.

Конденсатор 13 поддержки поддерживает ток, протекающий по обмотке J записи.

После отключения напряжения питания сердечник трансформатора сохранит намагниченность +В р.

Если же в триггере 9 к моменту отключения питания записан О, то элемент И-НЕ 11 не срабатывает (на втором входе этого элемента будет уровень логического О) и на его выходе будет высокий потенциал. Транзистор 15 закрыт и в сердечнике трансформатора 10 сохранится исходное состояние намагниченности -Вг, что

соответствует значению логического О.

Вспомогательный режим восстановления информации в триггере 9 осуществляется при включении напряжения питания после отключения последнего. Как только напряжение питания достигнет требуемого уровня на выходе компаратора 1 установится положительный уровень напряжения, который поступает на один вход элемента И 4, По этлму же сигналу запустится генег ратор 3 и будет сформирован одиночный импульс, который поступит на другой вход элемента И 4. Импульс с выхода элемента И 4 обнулит триггер 9 (это необходимо, так как при включении питания триггер может произвольно установиться в состояние 1) и, пройдя через элемент 6 задержки, поступит на обмотку считывания.

Если при отключении питающего напряжения в сердечнике была записана логическая 1, то под воздейст- вием импульса тока, протекающего по обмотке считывания, произойдет магничивание сердечника трансформатора 10 от значения +ВГ до -Вг и на обмотке записи наведется импульс ЭДС, который через конденсатор 12 прикладывается между базой и эмиттером транзистора 15, открывая его. Ток, протекающий через открывшийся транзистор, сформирует на нагрузочном сопротивлении 16 положительный импульс, который через элемент И 8 установит триггер 9 в 1, тем самым восстанавливая его состояние, в котором он находился на момент отключения питания. По окончании считывания сердечник останется перемагниченным в состоянии -Вр.

Если же в сердечнике трансформатора 10 был записан О при отключении питания, т.е. сердечник имеет намагниченность -Вг, то при протекании тока через обмотку считывания, перемагничивания сердечника по полному циклу не происходит, импульс ЭДС, наводимый в обмотке записи, будет недостаточным для открывания транзистора 15 и триггер 9 останется в нулевом состоянии.

Использование предлагаемого эле- мента памяти обеспечивает не только сохранение информации при отключении питания и последующее ее восстановле0

5

0

5

0

5

0

5

0

5

ние, но и существенное повышение быстродействия ЭП при работе в основном режиме. Формула изобретения

Элемент памяти, содержащий трансформатор, выполненный на сердечнике с прямоугольной петлей гистерезиса с обмотками считывания и записи, усилительный транзистор, нагрузочный резистор, форсирующий конденсатор, причем один вывод нагрузочного резистора соединен с шиной нулевого потенциала, а другой - с коллектором усилительного транзистора, эмиттер которого соединен с первым выводом обмотки записи, один вывод форсирующего конденса тора соединен с базой усилительного транзистора, а другой - с вторым выводом обмотки записи, отличающийся тем, что, с целью повышения быстродействия, в него введены конденсатор поддержки, ограничительный диод, элемент И-НЕ, компаратор, три элемента ИЛИ, генератор одиночных импульсов, два элемента И, элемент задержки, триггер, причем второй вывод обмотки считывания соединен с шиной нулевого потенциала и с одним выводом конденсатора поддержки, другой вывод которого соединен с вторым выводом форсирующего конденсатора и катодом ограничительного диода, анод которого подключен к шине питания, база транзистора соединена с выходом элемента И-НЕ, первый вход которого соединен с выходом второго элемента И, а второй вход подключен к единичному выходу .. триггера, первый вход компаратора подключен к шине питания, а второй соединен с источником опорного напряжения, первый и второй выходы компаратора соединены с соответствующими входами первого элемента ИЛИ и первыми входами соответственно первого и второго элементов И, выход подключен к входу генератора одиночных импульсов, выход которого соединен с вторыми входами первого и второго элементов И, выход первого элемента И соединен с первым входом второго элемента ИЛИ и входом элемента задержки, выход которого подключен к первому выводу обмотки считывания трансформатора, коллектор транзистора соеди- f пен с первым входом третьего элемента ИЛИ, выходы второго и третьего эле514747366

ментов ИЛИ подключены к установочным дами элемента памяти, а вторые входы R- и S-входам триггера соответствен- второго и третьего элементов ИЛИ явно, прямой и инверсный выходы кото- ляются входами записи элемента памя- рого являются соответствующими выхо- ти.

| Авторское свидетельство СССР У 1234883, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Элемент памяти | 1984 |

|

SU1265854A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1989-04-23—Публикация

1987-04-27—Подача