Изобретение относится к системам обработки и хранения информации, в частности экстремальных значений параметров, и может быть использовано в устройствах для амплитудных измерений в машиностроении.

Цель изобретения - упрощение устройства.

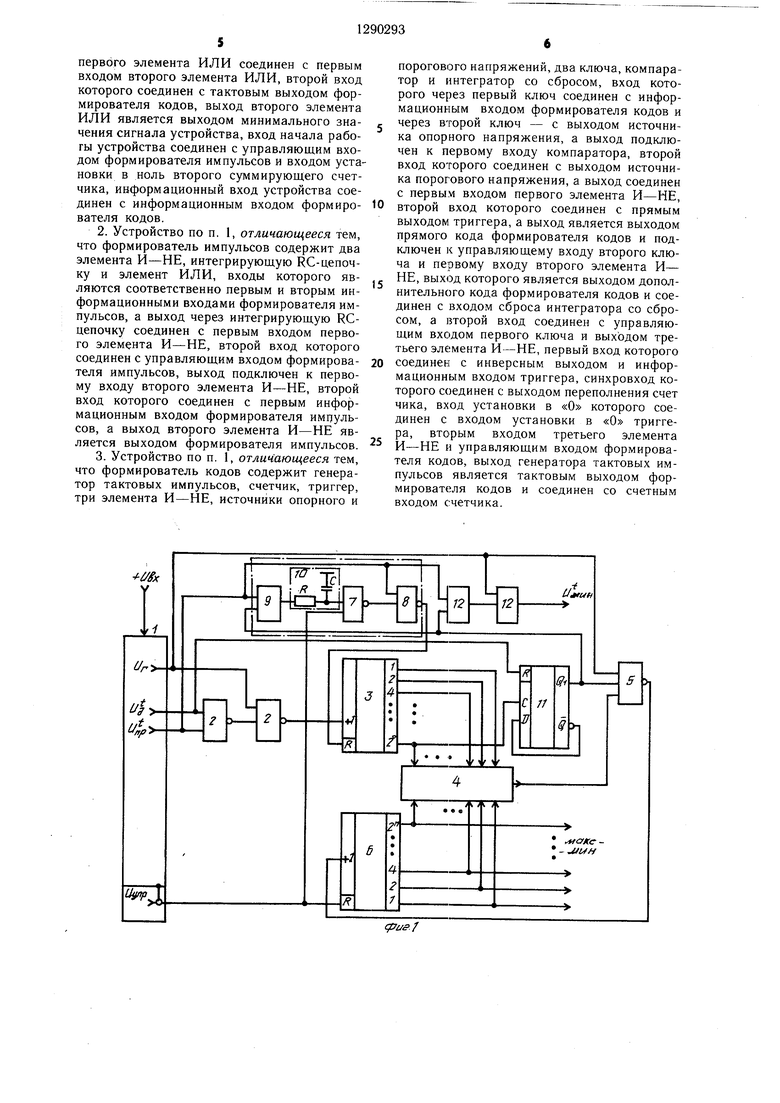

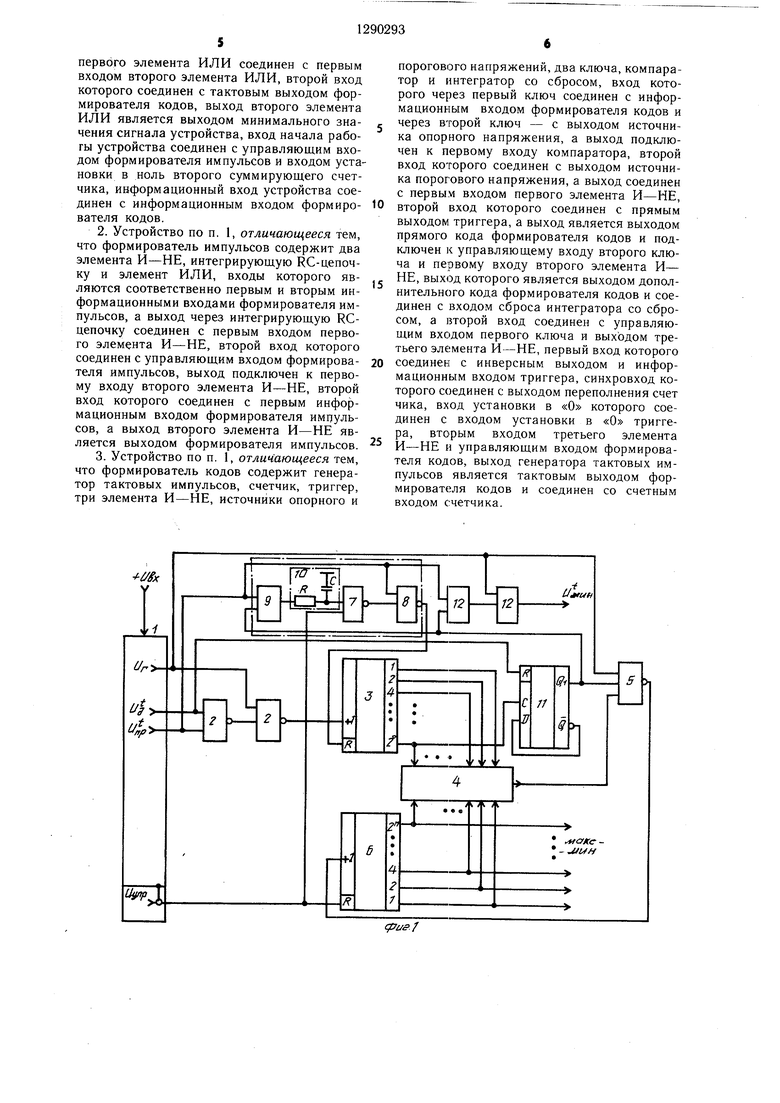

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 - функциональная схема формирователя кодов; на фиг. 3- 5 - временные диаграммы работы устройства.

Устройство содержит формирователь 1 кодов, элементы И-НЕ 2, счетчик 3, схему 4 сравнения, элемент И-НЕ 5, счетчик 6, формирователь импульсов, включающий элементы И-НЕ 7 и 8, элемент ИЛИ 9, интегрирующую RC-цепочку 10, триггер 11, элементы ИЛИ 12.

Формирователь кодов содержит интегратор 13, ключи 14 и 15, источник 16 опорного напряжения, компаратор 17, источник 18 порогового напряжения, элемент И-НЕ 19, триггер 20, элемент И-НЕ 21, ключ 22 интегратора, элемент И-НЕ 23, счетчик 24, генератор 25 импульсов.

Устройство работает следующим образом.

В исходном состоянии, когда на щине управления присутствует нулевой уровень напряжения, все триггеры и счетчики обнулены. На Щ ине дополнительного кода устанавливается тоже нулевой уровень, так как на всех входах элемента И-НЕ 21 (фиг. 2) присутствуют единичные уровни напряжения. На шине прямого кода устанавливается единичный уровень. С выхода генератора 25 на шину генератора поступают прямоугольные импульсы. Оба ключа 14 и 15 разомкнуты, так как на их управляющие входы поступают единичные уровни напряжения с выходов элементов И-НЕ 23 и 19 соответственно, а ключ 22 замкнут, так как на его управляющий вход поступает нулевой уровень.

Ключ 22 обнуляет интегратор. При поступлении на управляющую шину в момент to {см. фиг. 5) единичного уровня счетчик 24 начинает подсчитывать импульсы. На выходе элемента И-НЕ 23 формируется нулевой уровень, который замыкает ключ 14, а через элемент И-НЕ 21 размыкает ключ 22, так как на щине дополнительного кода формируется единичный уровень напряжения. На выходе интегратора 13 (см. фиг. 5) наблюдается интегрирование входного сигнала. В этот момент (to) компаратор 17 формирует на выходе единичный уровень напряжения. Затем счетчик 24 переполнится и импульс переполнения переключит триггер 20 в единичное состояние. Это вызывает переключение ключей 14 и 15, так как на вход ключа 14 приходит единичный уровень, а на вход ключа 15 - нулевой. В результате

на вход интегратора подается отрицательное образцовое напряжение и на выходе интегратора в период (ti-12) наблюдается интегрирование образцового напряжения. Напряжение на выходе интегратора 13 сравнивается с пороговым Ии и к-омпаратор 17 формирует на своем выходе нулевой уровень, который через элемент И-НЕ 19 размыкает ключ 15. При этом на шине дополнительного кода через элемент И-НЕ 2 устанавливается нулевой уровень, который замыкает ключ 22. Счетчик 24 продолжает подсчитывать импульсы генератора 25 и при очередном переполнении счетчика 24 триггер 20 переключится вновь в нулевое состояние. На ишне дополнительного кода устанавливается единичный уровень, который размыкает ключ 22. Ключ 4 замыкается и начинается второй цикл преобразования.

Как видно из фиг. 5, прямой код в первом цикле преобразования формируется с момента ti и до момента ta, а дополнительный код - с момента t и до момента 1з; во втором цикле соответственно прямой код с момента t4 и Да ts, а дополнительный - с ts и до is и т.д. Каждый код представляется импульсами

нулевого уровня, соответствующей длительности на соответствующих щинах формирования кодов.

iaKHvi образом, после запуска устройства первый нулевой уровень, длительность которого соответствует коду а на фиг. 3, приходит по шине прямого кода. В результате в счетчик 3 записывается с шины генератора через элемент И-НЕ 2 число импульсов, равное коду а. Так как переполнения счетчика 3 при этом не происходит, то по окончании нулевого уровня на шине прямого кода формирователь импульсов на элементах ИЛИ 9, И-НЕ 7 и 8 и интегрирующей RC-цепи 10 формирует короткий отрицательный импульс, который устанавлива0 ет счетчик 3 вновь в нулевое состояние. Следующий нулевой уровень напряжения появляется на шине дополнительного кода. В результате в счетчик 3 также через элемент И-НЕ 2 записывается число импульсов, равное дополнительному к-оду (N-a)

первого цикла преобразования. Во втором цикле первым формируется прямой код Ь. Поэтому к дополнительному коду первого цикла (N-а), хранящемуся в счетчике 3, дозаписывается прямой код b второго цикла.

Q При этом происходит переполнение счетчика 3 и триггер 11 переключается в единичное состояние. На выходе схемы 4 сравнения устанавливается единичный уровень напряжения, когда содержимое счетчика 3 станет равно или больше содержимого счетчи5 ка 6. Так как содержимое счетчика 6 было равно нулю, то после переполнения счетчика 3 в оба счетчика 3 и 6 запищется остаток (Ь - а); в счетчик 6 он запишется

через элемент И-НЕ 5. Единичный уровень напряжения с прямого выхода триггера 11 после переполнения счетчика 3 проходит на вход элемента .ИЛИ 9 и формирует на выходе элемента И-НЕ 7 нулевой уровень. Поэтому при переходе уровня напряжения на шине прямого кода с нулевого на единичный установочный импульс на выходе элемента И-НЕ 8 не формируется и состояние счетчика 3 в момент окончания прямого кода а не изменяется.

Следовательно, дополнительный код {N- -Ь) второго цикла преобразования суммируется в счетчике 3 с хранимой там разностью (Ь-а): (N-b)4-(b-а) N-а, где (N-а) - дополнительный код меньшего на данный момент значения аналогового сигнала. В дальнейшем при записи в счетчик 3 дополнительного кода очередного числа в счетчике 3 фиксируется и некоторое время хранится дополнительный код минимального из всех предшествуюш,их чисел. Нулевой уровень каждого дополнительного кода устанавливает триггер 11 по установочному Р-входу в нулевое состояние. После записи в счетчик 3 прямого кода с третьего цикла преобразования в счетчике будет храниться число (с-а), так как (N-а)+с с-а.

В период записи в счетчик 3 остатка (с-а) содержимое счетчика 3 было меньше хранимого в счетчике 6 числа (Ь-а), поэтому на выходе схемы сравнения был нуле- вой уровень, который закрывал элемент И-НЕ 5. Это продолжалось до момента, пока содержимое обоих счетчиков не сравнялось. После этого заполнение счетчиков 3 и б стало происходить одновременно и в счетчике 6 после записи прямого кода с также будет храниться число (с-а).

Таким образом в счетчике 6 выделяется максимальная разность между текущим и минимальным предшествующим числом (кодом) . Как видно из фиг. 4 и 3, число е меньше числа а, поэтому при записи прямого кода е переполнения счетчика 3 не происходит и по окончании е на выходе элемента И-НЕ 8 формируется короткий нулевой уровень, который устанавливает счетчик 3 в нулевое состояние. После этого в счетчик 3 записывается дополнительный код (N-е). В дальнейшем в счетчике 3 после его переполнения в период записи очередного прямого текущего кода формируется разность между этим текущим кодом и минимальным числом е. С приходом кода k в счетчиках 3 и 6 формируется размах сходного сигнала (к-е).

Устройство запоминает максимальный размах входного аналогового сигнала, если сигнал периодический или его максимальное значение следует после минимального. Максимальный размах аналогового сигнала хранится в счетчике 6 и его в любой момент можно вывести на индикацию или обработку. Минимальное значение сигнала хранится в счетчике 3 в динамическом виде и его можно выделить, например, во время записи в счетчик 3 очередного прямого кода, а именно с начала прямого кода и до переполнения счетчика 3 (фиг. 4). В устройстве это осуществляется с помощью двух элементов ИЛИ 12. На выходе второго элемента ИЛИ 12 можно наблюдать в каждом цикле преобразования пачки импульсов. Число импульсов в этих пачках равно минимальному значению входного сигнала. Таким образом, предложенное устройство запоминает минимальное значение любогр входного сигнала и максимальный размах возрастающего или периодического сигнала.

Формула изобретения

1. Устройство для определения экстремаль - ных значений аналогового сигнала, содержащее формирователь импульсов, формирователь кодов, первый выход которого соединен с первыми входами первого и второго элементов И-НЕ, выходы которых подключены к информационным входам соответственно первого и второго элементов памяти, выходы первого элемента памяти соединены с первой группой входов схемы сравнения, отличающееся тем, что, с целью упрощения устройства, элементы памяти выполнены на суммирующих счетчиках, суммирующие входы которых являются информационными входами элементов памяти, первый выход формирователя кодов является тактовым выходом формирователя кодов и устройство дополнительно содержит третий элемент И- НЕ, два элемента ИЛИ и триггер, вход начальной установки которого соединен с выходом дополнительного кода формирователя кодов и с первым входом третьего элемента И-НЕ, второй вход которого соединен с выходом прямого кода формирователя кодов и с первым входом первого элемента ИЛИ, первым информационным входом формирователя импульсов, а выход третьего элемента И,-НЕ подключен к второму входу первого элемента И-НЕ, выход формирователя импульсов соединен с входом установки в ноль первого суммирующего счетчика, выход переполнения которого подключен к синхровходу триггера, инверсный выход которого соединен с его информационным входом, а прямой выход соединен с вторым информационным входом формирователя импульсов, вторым входом первого элемента ИЛИ и вторым входом второго элемента И - НЕ, третий вход которого подключен к выходу схемы сравнения, вторая группа входов которой- соединена с выходами второго суммирующего счетчика и является группой информационных выходов устройства, выход

первого элемента ИЛИ соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с тактовым выходом формирователя кодов, выход второго элемента ИЛИ является выходом минимального значения сигнала устройства, вход начала рабо- гы устройства соединен с управляющим входом формирователя импульсов и входом установки в ноль второго суммирующего счетчика, информационный вход устройства соединен с информационным входом формирователя кодов.

2.Устройство по п. 1, отличающееся тем, что формирователь импульсов содержит два элемента И-НЕ, интегрирующую RC-цепоч- ку и элемент ИЛИ, входы которого являются соответственно первым и вторым информационными входами формирователя импульсов, а выход через интегрирующую RC- цепочку соединен с первым входом первого элемента И-НЕ, второй вход которого соединен с управляющим входом формирователя импульсов, выход подключен к первому входу второго элемента И-НЕ, второй вход которого соединен с первым информационным входом формирователя импульсов, а выход второго элемента И-НЕ является выходом формирователя импульсов.

3.Устройство по п. 1, отличающееся тем, что формирователь кодов содержит генератор тактовых импульсов, счетчик, триггер, три элемента И-НЕ, источники опорного и

0

5

порогового напряжений, два ключа, компаратор и интегратор со сбросом, вход которого через первый ключ соединен с информационным входом формирователя кодов и через второй ключ - с выходом источника опорного напряжения, а выход подключен к первому входу компаратора, второй вход которого соединен с выходом источника порогового напряжения, а выход соединен с первым входом первого элемента И-НЕ, второй вход которого соединен с прямым выходом триггера, а выход является выходом прямого кода формирователя кодов и подключен к управляющему входу второго ключа и первому входу второго элемента И- НЕ, выход которого является выходом дополнительного кода формирователя кодов и соединен с входом сброса интегратора со сбросом, а второй вход соединен с управляющим входом первого ключа и выходом третьего элемента И-НЕ, первый вход которого соединен с инверсным выходом и информационным входом триггера, синхровход которого соединен с выходом переполнения счет чика, вход установки в «О которого соединен с входом установки в «О триггера, вторым входом третьего элемента И-НЕ и управляющим входом формирователя кодов, выход генератора тактовых импульсов является тактовым выходом формирователя кодов и соединен со счетным входом счетчика.

Изобретение относится к системам обработки и хранения информации, в частности экстремальных значений параметров, и может быть использовано в устройствах для амплитудных измерений в машиностроении. Цель изобретения - упрощение устройства. Устройство содержит формирователь кодов, элементы И-НЕ, ИЛИ, счетчики, схему срав-- нения, формирователь импульсов на элементах И-НЕ, ИЛИ, интегрирующей RC-цепоч- ке. Формирователь кодов выполнен по схеме АЦП двухтактного интегрирования и содержит интегратор, ключи источника опорного и порогового напряжения, элементы И-НЕ, триггер, генератор импульсов. Устройство запоминает максимальный размах входного аналогового сигнала, если сигнал периодический или если его максимальное значение следует после минимального. 2 з.п. ф-лы, 5 ил. ю со о |С QO ОЭ

./

gyus3

фиа.

Редактор М. Дылын Заказ 7901/45

Составитель Е. Иванова

Техред И. ВересКорректор А. Зимокосов

Тираж 673Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб:, д. 4/5 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Устройство для сравнения двоичных чисел | 1978 |

|

SU744553A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 760087, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-15—Публикация

1985-03-18—Подача