,113

Изобретение относится к вычислительной технике и может найти применение при построении быстродействующих универсальных ЭВМ, работающих Б двоично-десятичной системе счисле- ния.

Целью изобретения является повышение быстродействия.

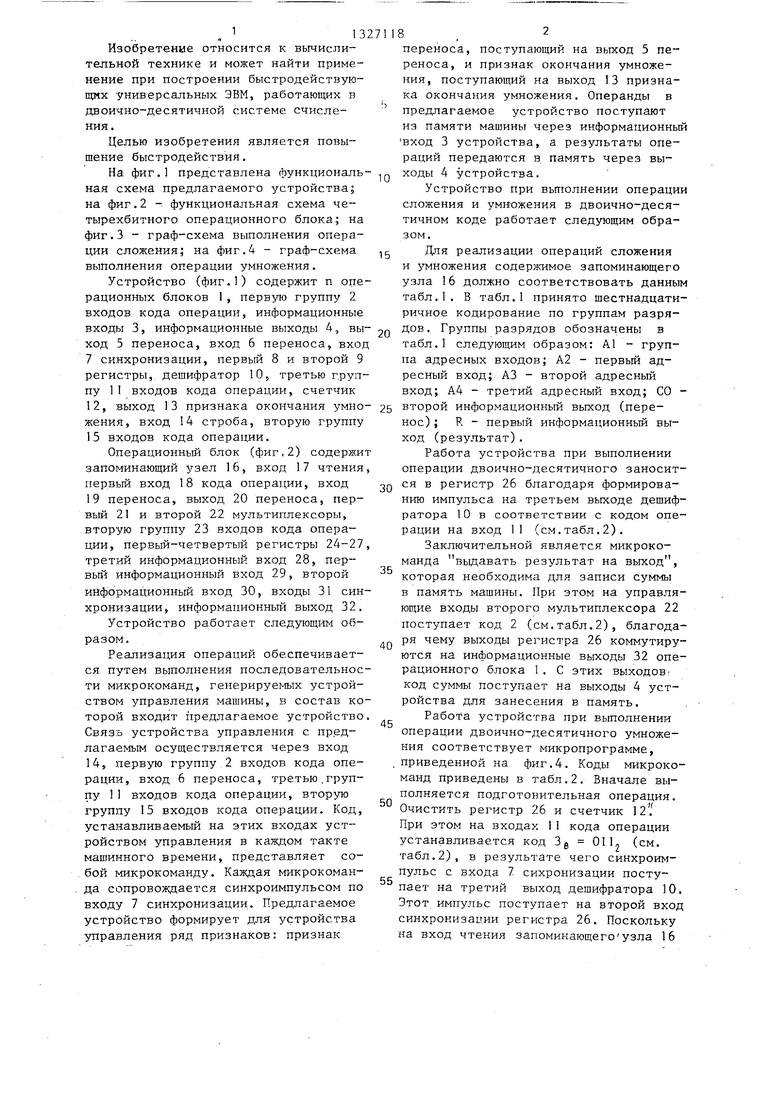

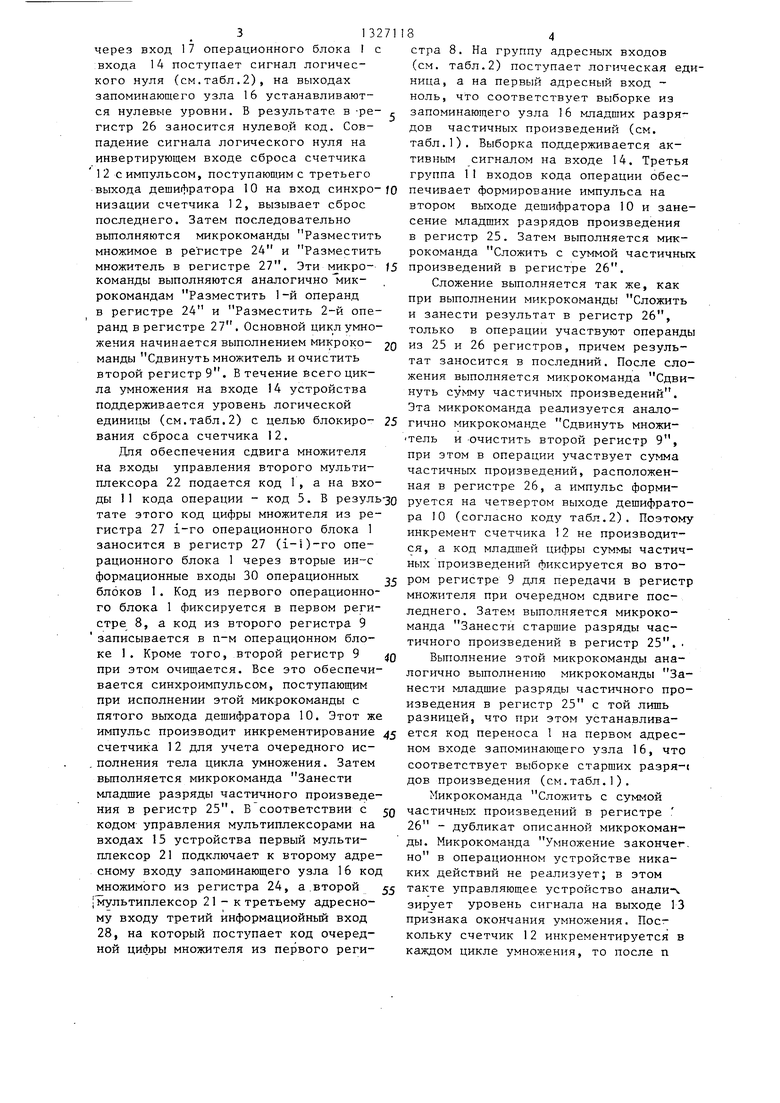

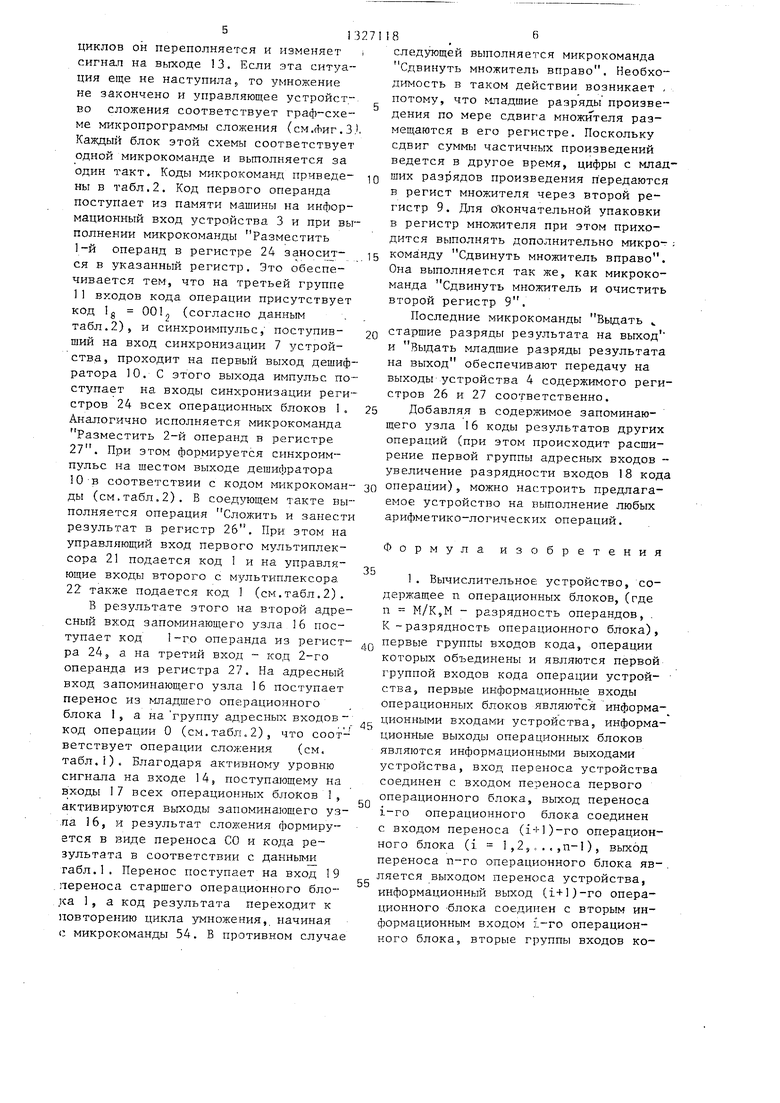

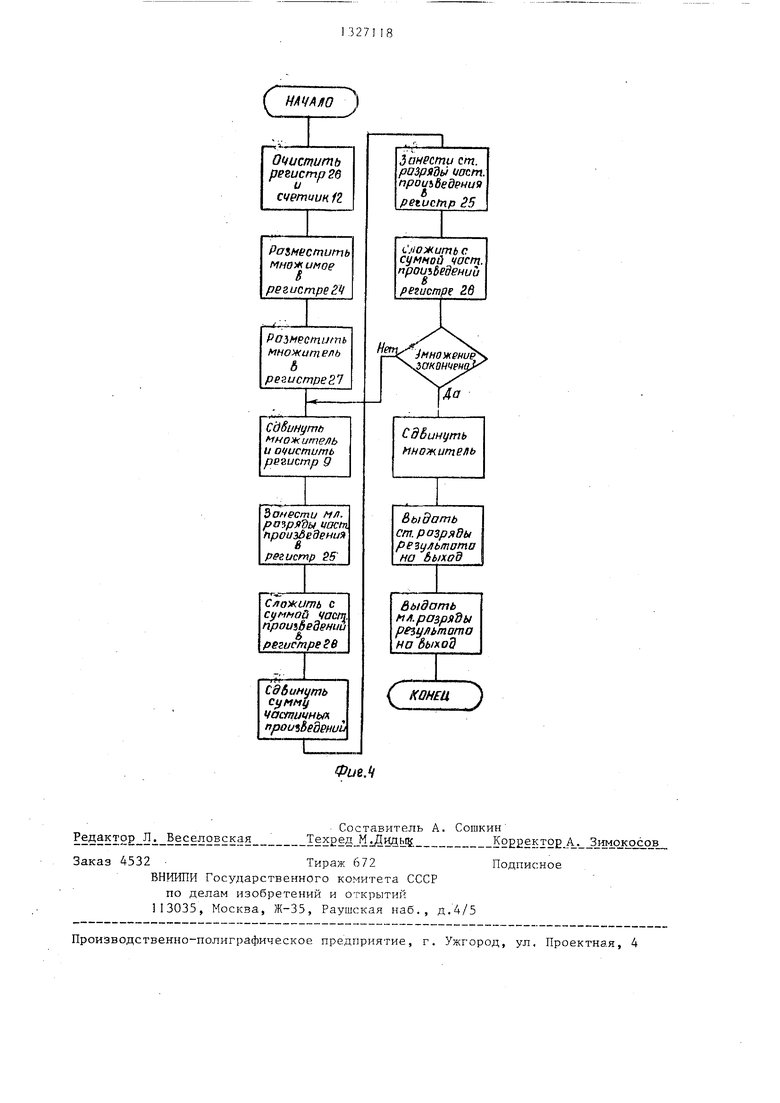

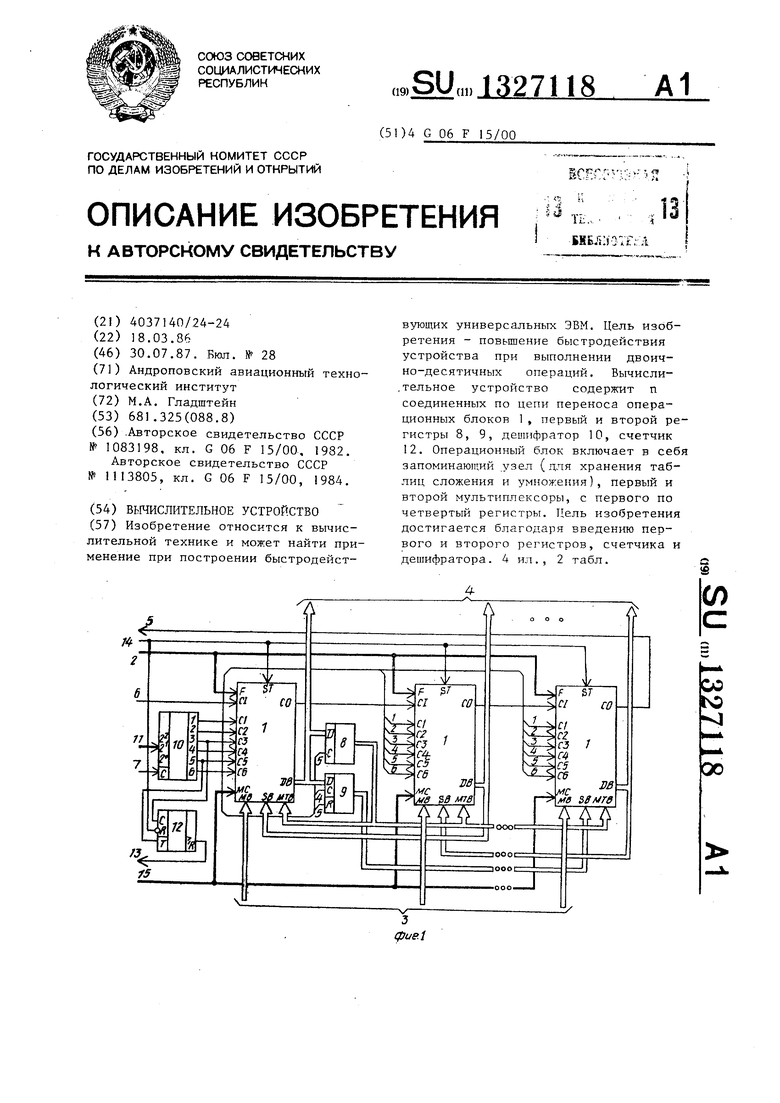

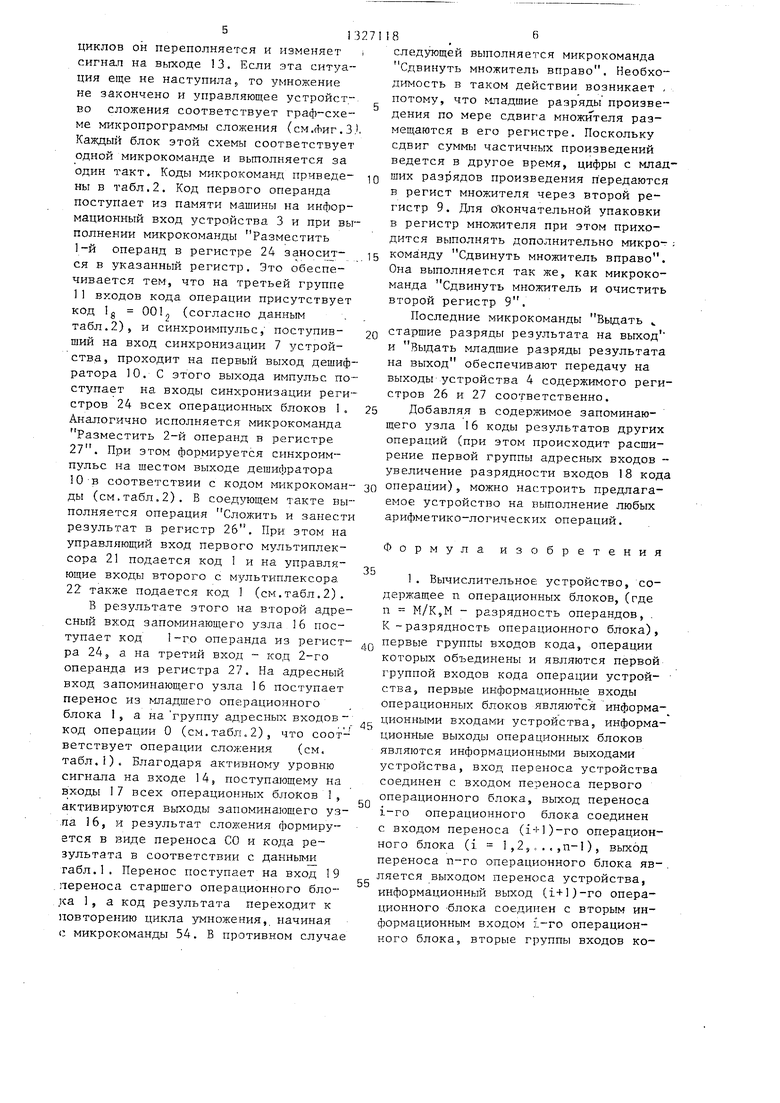

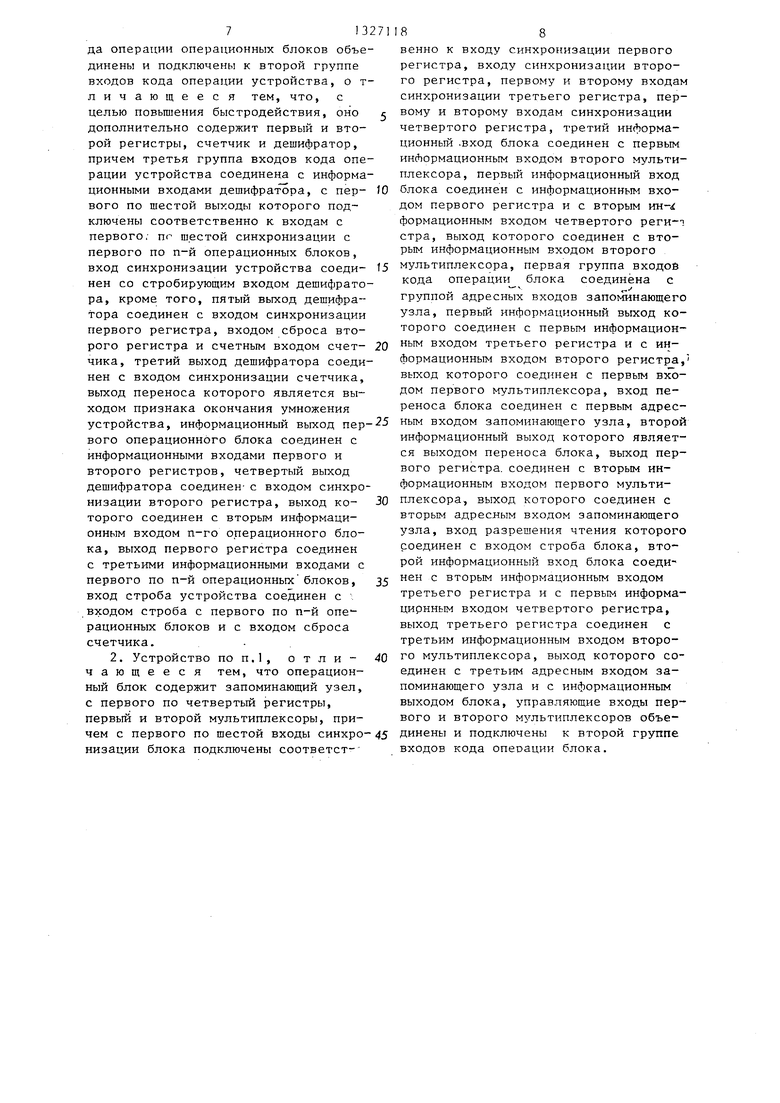

На фиг,1 представлена функциональная схема предлагаемого устройства; на фиг.2 - функциональная схема четырехбитного операционного блока; на фиг.З - граф-схема выполнения операции сложения; на фиг.4 - граф-схема выполнения операции умножения.

Устройство (фиг.1) содержит п операционных блоков 1, первую группу 2 входов кода операции, информационные входы 3, информационные выходы 4, выход 5 переноса, вход 6 переноса, вход 7 синхронизации, первый 8 и второй 9 регистры, дешифратор 10, третью группу 1I входов кода операции, счетчик 12, выход 13 признака окончания умно жения, вход 14 строба, вторую группу 15 входов кода операции.

Операционный блок (фиг,2) содержи запоминающий узел 16, вход 17 чтения первый вход 18 кода операции, вход 19 переноса, выход 20 переноса, первый 21 и второй 22 мультиплексоры, вторую группу 23 входов кода операции, первый-четвертый регистры 24-27 третий информационный вход 28, пер- вьш информационный вход 29, второй информационный вход 30, входы 31 синхронизации, информационный выход 32.

Устройство работает следующим образом.

Реализация операций обеспечивается путем выполнения последовательности микрокоманд, генерируемых устройством управления машины, в состав которой входит предлагаемое устройство Связь устройства управления с предлагаемым осуществляется через вход 14, первую группу 2 входов кода операции, вход 6 переноса, третью.группу 11 входов кода операции, вторую группу 15 входов кода операции. Код, устанавливаемый на этих входах устройством управления в каждом такте машинного времени, представляет собой микрокоманду. Каждая микрокоманда сопровождается синхроимпульсом по входу 7 синхронизации. Предлагаемое устройство формирует для устройства управления ряд признаков: признак

0

5

0

25

0

35

40

45

50

55

переноса, поступающий на выход 5 переноса, и признак окончания умножения, поступающий на выход 13 признака окончания умножения. Операнды в предлагаемое устройство поступают из памяти машины через информационный вход 3 устройства, а результаты операций передаются в память через выходы 4 устройства.

Устройство при выполнении операции сложения и умножения в двоично-десятичном коде работает следующим образом.

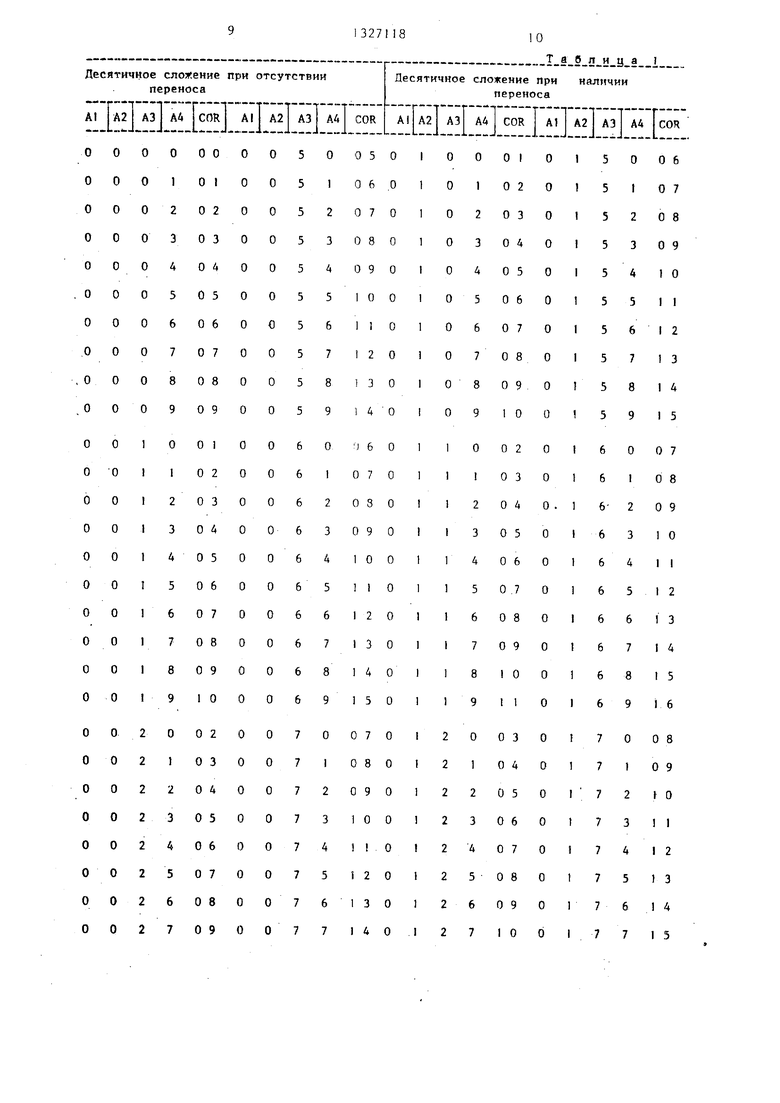

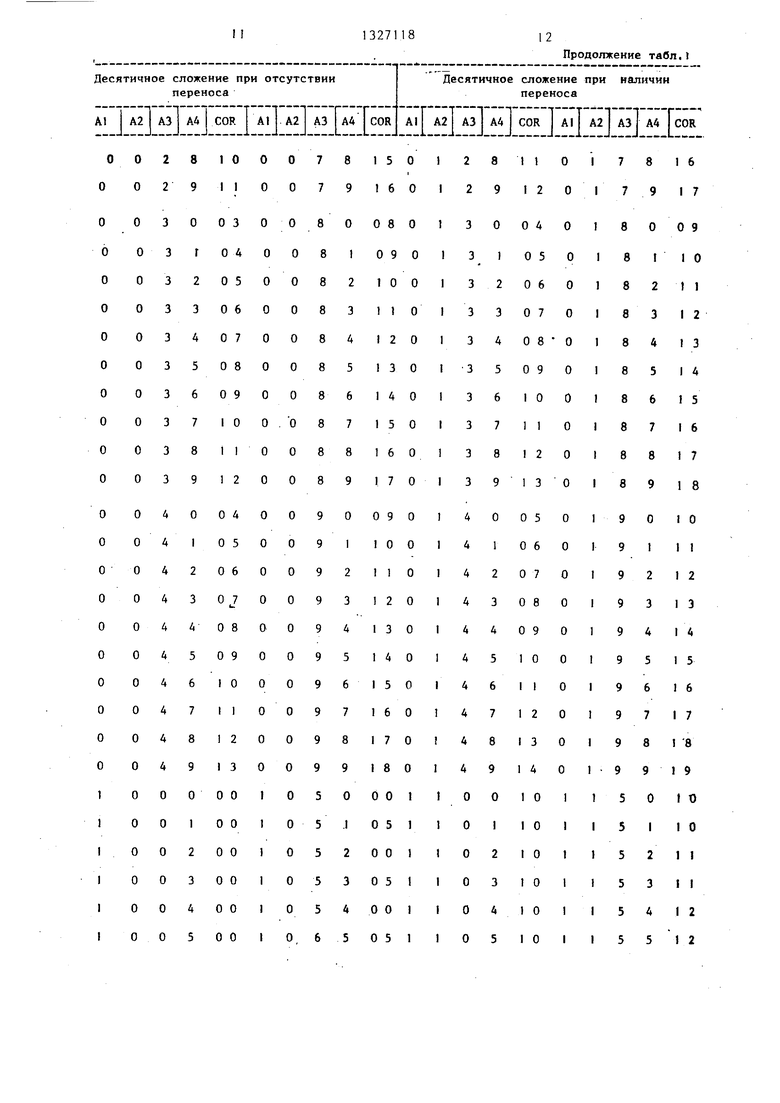

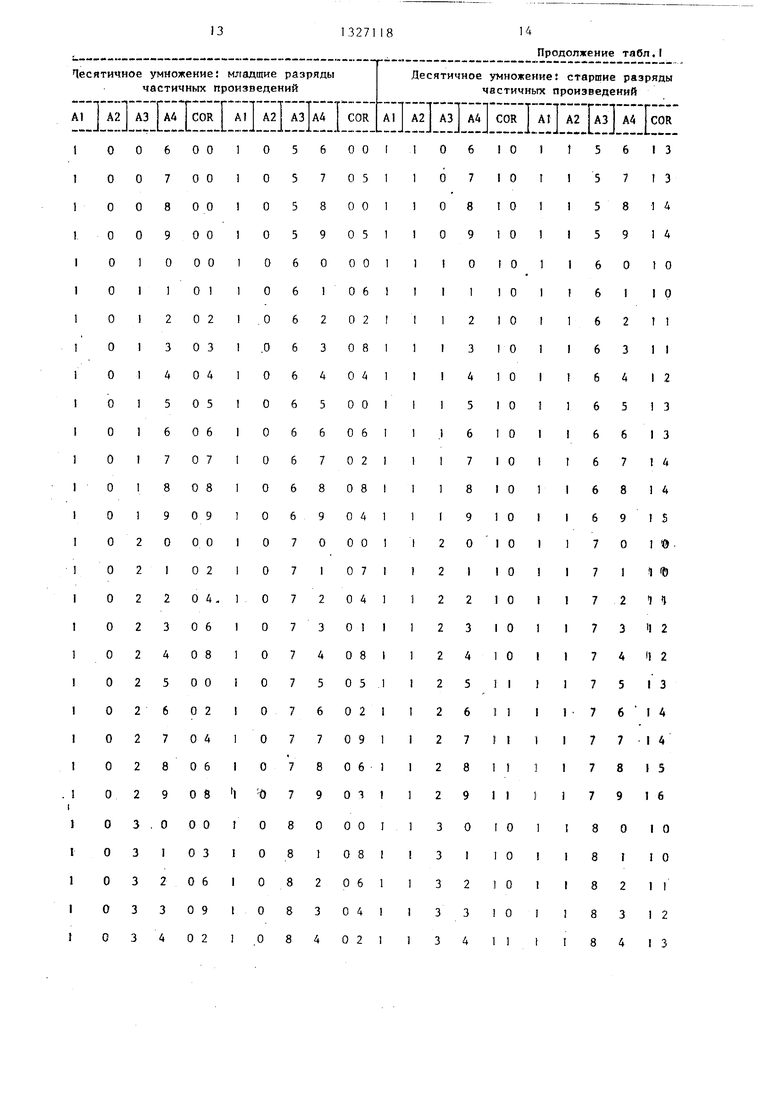

Для реализации операций сложения и з множения содержимое запоминающего узла 16 должно соответствовать данным табл.1. В табл.1 принято шестнадцатиричное кодирование по группам разрядов. Группы разрядов обозначены в табл.1 следующим образом; А1 - группа адресных входов; А2 - первый адресный вход; A3 - второй .адресный вход; А4 - третий адресный вход; СО - второй информационный выход (перенос) ; R - первый информационньй выход (результат).

Работа устройства при выполнении операции двоично-десятичного заносится в регистр 26 благодаря формированию импульса на третьем выходе дешифратора 10 в соответствии с кодом операции на вход 11 (см.табл.2).

Заключительной является микрокоманда выдавать результат на выход, которая необходима для записи суммы в память машины. При этом на управляющие входы второго мультиплексора 22 поступает код 2 (см.табл.2), благодаря чему выходы регистра 26 коммутируются на информационные выходы 32 операционного блока 1. С этих выходов I код суммы поступает на выходы 4 устройства для занесения в память.

Работа устройства при выполнении операции двоично-десятичного умножения соответствует микропрограмме, приведенной на фиг.4. Коды микрокоманд приведены в табл.2. Вначале выполняется подготовительная операция. Очистить регистр 26 и счетчик 12. При этом на входах 11 кода операции устанавливается код 3g Oil. (см. табл.2), в результате чего синхроимпульс с входа 7 сихронизации поступает на третий выход дешифратора 10. Этот импульс поступает на второй вход синхронизации регистра 26. Поскольку на вход чтения запоминающего узла 16

3132

через вход 17 операционного блока с :входа 14 поступает сигнал логического нуля (см.табл.2), на выходах запоминающего узла 16 устанавливаются нулевые уровни. В результате в -ре- гистр 26 заносится нулевой код. Совпадение сигнала логического нуля на инвертирующем входе сброса счетчика 12 с импульсом, поступающим с третьего выхода дешифратора 10 на вход синхронизации счетчика 12, вызывает сброс последнего. Затем последовательно вьшолняются микрокоманды Разместить множимое в регистре 24 и Разместить множитель в регистре 27. Эти микро- команды выполняются аналогично рокомандам Разместить 1-и операнд в регистре 24 и Разместить 2-й операнд в регистре 27, Основной умножения начинается выполнением микроко- манды Сдвинуть множитель и очистить второй регистр 9. В течение всего цикла умножения на входе 14 устройства поддерживается уровень логической единицы (см.табл.2) с целью блокиро- вания сброса счетчика 12.

Для обеспечения сдвига множителя на входы управления второго мультиплексора 22 подается код 1, а на входы 1 кода операции - код 5. В резуль тате этого код цифры множителя из регистра 27 i-ro операционного блока 1 заносится в регистр 27 (i-i)-ro операционного блока 1 через вторые ин-с формационные входы 30 операционных блоков 1. Код из первого операционного блока 1 фиксируется в первом регистре 8, а код из второго регистра 9 записывается в п-м операционном блоке 1 . Кроме того, второй регистр 9 при этом очищается. Все это обеспечивается синхроимпульсом, поступающим при исполнении этой микрокоманды с пятого выхода дешифратора 10. Этот же импульс производит инкрементирование счетчика 12 для учета очередного ис- .полнения тела цикла умножения. Затем выполняется микрокоманда Занести младшие разряды частичного произведения в регистр 25. В соответствии с кодом управления мультиплексорами на входах 15 устройства первый мультиплексор 21 подключает к второму адресному входу запоминающего узла 16 код множимого из регистра 24, а.второй мультиплексор 21 - к третьему адресному входу третий йнформациойньй вход 28, на который поступает код очередной цифры множителя из первого реги84

стра 8. На группу адресных входов (см. табл.2) поступает логическая едница, а на первый адресный вход - ноль, что соответствует выборке из запоминающего узла 16 младших разрядов частичных произведений (см. табл.1). Выборка поддерживается активным сигналом на входе 14. Третья группа 11 входов кода операции обеспечивает формирование импульса на втором выходе дешифратора 10 и занесение младших разрядов произведения в регистр 25. Затем выполняется микрокоманда Сложить с суммой частичных произведений в регистре 26.

Сложение выполняется так же, как при выполнении микрокоманды Сложить и занести результат в регистр 26, только в операции участвуют операнды из 25 и 26 регистров, причем результат заносится в последний. После сложения выполняется микрокоманда Сдвинуть сумму частичных произведений. Эта микрокоманда реализуется аналогично микрокоманде Сдвинуть множи- тель и ОЧИСТИТЬ второй регистр 9, при этом в операции участвует сумма частичных произведений, расположенная в регистре 26, а импульс формируется на четвертом выходе дешифратора 10 (согласно коду табл.2). Поэтому инкремент счетчика 12 не производится, а код младшей цифры суммы частичных произведений фиксируется во втором регистре 9 для передачи в регистр множителя при очередном сдвиге последнего. Затем выполняется микрокоманда Занести старшие разряды частичного произведений в регистр 25. .

Выполнение этой микрокоманды аналогично выполнению микрокоманды Занести младшие разряды частичного произведения в регистр 25 с той лишь разницей, что при этом устанавливается код переноса 1 на первом адресном входе запоминающего узла 16, что соответствует выборке старших разря- дов произведения (см.табл.1).

Микрокоманда Сложить с суммой частичных произведений в регистре 26 - дубликат описанной микрокоманды. Микрокоманда Умножение закончег. но в операционном устройстве никаких действий не реализует; в этом такте управляющее устройство анали-х. зирует уровень сигнала на выходе 13 признака окончания умножения. Поскольку счетчик 12 инкрементируется в каждом цикле умножения, то после п

513

циклов он переполняется и изменяет сигна.п на выходе 13. Если эта ситуация еще не наступила то умножение не закончено и управляющее устройство сложения соответствует граф-схе- ме микpoпpoгpa гмы сложения (см.сЬиг. 3, Каждый блок этой схемы соответствует одной микрокоманде и выполняется за один такт. Коды микрокоманд приведены в табл.2. Код первого операнда поступает из памяти машины на информационный вход устройства 3 и при выполнении микрокоманды Разместить 1-й операнд в регистре 24 заноси - ся в указанный регистр. Это обеспечивается тем, что на третьей группе 11 входов кода операции присутствует код Ig OOlj (согласно данным табл.2) 5 и синхроимпульс, поступивший на вход синхронизации 7 устройства, проходит на первый выход дешифратора 10. С этого выхода импульс поступает на входы синхронизации регистров 24 всех операционных блоков 1. Аналогично исполняется микрокоманда Разместить 2-й операнд в регистре 27. При этом формируется синхроимпульс на шестом выходе дешифратора 0 в соответствии с кодом микрокоман- ды (см.табл.2). В соедующем такте выполняется операция Сложить и занести результат в регистр 26. При этом на управляющий вход первого мультиплексора 21 подается код 1 и на управля- юш;ие входы второго с мультиплексора 22 также подается код 1 (см.табл.2).

В результате этого на второй адресный вход запоминающего узла 16 поступает код 1-го операнда из регистра 24, а на третий вход - код 2-го операнда из регистра 27. На адресный вход запоминающего узла 16 поступает перенос из младшего операционного блока I , а на группу адресных входов - код операции О (см,табл.2), что соответствует операции сложения (см. табл.1) Благодаря активному уровню сигнала на входе 14j поступающему на входы 17 всех операционных блоков I, активируются выходы запоминающего узла 16, и результат формируется в виде переноса СО и кода результата в соответствии с данным и табл.. Перенос поступает на вход 19 переноса старшего операционного блока 1, а код результата переходит к 1овторению цикла умножения, начиная с микрокоманды 54. В противном случае

5

0

5

1

о

5

0

5

0

5

18 .

следующей выполняется микрокоманда Сдвинуть множитель вправо. Необходимость в таком действии возникает , потому, что младшие разряды произведения по мере сдвига множителя размещаются в его регистре. Поскольку сдвиг суммы частичных произведений ведется в другое время, цифры с младших разрядов произведения п ередаются в регист множителя через второй регистр 9. Для о1сончательной упаковки в регистр мноясителя при этом приходится выполнять дополнительно микро- ; команду Сдвинуть множитель вправо. Она выполняется так же, как микрокоманда Сдвинуть множитель и очистить второй регистр 9.

Последние микрокоманды Выдать старшие разряд 51 результата на выход и Выдать младшие разряды результата на выход обеспечивают передачу на выходы устройства 4 содержимого регистров 26 и 27 соответственно.

Добавляя в содержимое запоминающего узла 16 коды результатов других операций (при этом происходит расширение первой группы адресных входов - увеличение разрядности входов 18 кода операции), можно настроить предлагаемое устройство на выполнение любых арифметико-логических операций.

Формула изобретения

1. Вычислительное устройство, содержащее п операционных блоков, (где п М/К,М - разрядность операндов, . К -разрядность операционного блока), первые группы входов кода, операции которых объединены и являются первой группой входов кода операции устрой- ства, первые информационные входы операционных блоков являются информационными входами устройства, информационные выходы операционных блоков являются информационными выходами устройства, вход переноса устройства соединен с входом переноса первого операционного блока, выход переноса i-ro операционного блока соединен с входом переноса (i+l)-ro операционного блока (i 1 ,2, ,: . . ,n-I), выход переноса п-го операционного блока яв-, ляется выходом переноса устройства, информационный выход (i+l)-ro операционного -блока соединен с вторым информационным входом L-ro операционного блока, вторые группы входов ко713

да операции операционных блоков объединены и подключены к второй группе входов кода операции устройства, о т личающееся тем, что, с целью повышения быстродействия, оно дополнительно содержит первый и второй регистры, счетчик и дешифратор, причем третья группа входов кода операции устройства соединена с информационными входами дешифратора, с пер- вого по шестой выходы которого подключены соответственно к входам с первого; пг шестой синхронизации с первого по п-й операционных блоков, вход синхронизации устройства соеди- нен со стробирующим входом дешифратора, кроме того, пятый выход дешифратора соединен с входом синхронизации первого регистра, входом сброса второго регистра и счетным входом счет- чика, третий выход дешифратора соединен с входом синхронизации счетчика, выход переноса которого является выходом признака окончания умножения устройства, информационный выход иер вого операционного блока соединен с информационными входами первого и второго регистров, четвертый выход дешифратора соединен- с входом синхронизации второго регистра, выход ко- торого соединен с вторым информационным входом п-го операционного блока, выход первого регистра соединен с третьими информационными входами с первого по п-й операционных блоков, вход строба устройства соединен с входом строба с первого по п-й операционных блоков и с входом сброса счетчика.

2. Устройство по П.1, о т л и - чающееся тем, что операционный блок содержит запоминаюш;ий узел, с первого по четвертый регистры, первый и второй мультиплексоры, причем с первого по шестой входы синхронизации блока подключены соответст88

венно к входу синхронизации первого регистра, входу синхронизации второго регистра, первому и второму входам синхронизации третьего регистра, первому и второму входам синхронизации четвертого регистра, третий информационный .вход блока соединен с первым информационным входом второго мультиплексора, первый информационный вход блока соединен с информационным входом первого регистра и с вторым ин- формационным входом четвертого реги-т стра, выход которого соединен с вторым информационным входом второго мультиплексора, первая группа входов кода операции блока соединена с группой адресных входов запоминаюш;его узла, первый информационный выход которого соединен с первым информационным входом третьего регистра и с информационным входом второго регистра, вьгход которого соединен с первым входом первого мультиплексора, вход переноса блока соединен с первым адресным входом запоминающего узла, второй информационный выход которого является выходом переноса блока, выход первого регистра, соединен с вторым информационным входом первого мультиплексора, выход которого соединен с вторым адресным входом запоминающего узла, вход разрешения чтения которого соединен с входом строба блока, второй информационный вход блока соединен с вторым информационным входом третьего регистра и с первым информа- цирнным входом четвертого регистра, выход третьего регистра соединен с третьим информационным входом второго мультиплексора, выход которого соединен с третьим адресным входом запоминающего узла и с информационным выходом блока, управляющие входы первого и второго мультиплексоров объединены и подключены к второй группе входов кода операции блока.

Продолжение табл.1

О

О

О

О

1

1

1

1

1

1 1

1

1

1

2 2 2 2 2 2 3 3

3

3

3

600 1 700 1

800 1

900

000

1О 1

202

303

404

505

О

1О

1О

)О

1О

1о

I.0

1.0

1о

1о

о 6 I

6

7071

8081

9091

000I

1021

204.1 306 4081 5001 602I 7041 8061

9 OS l i) 000 10 10310 206 I О 3 09 О 40210

56

57

58

59

6О 61 62 63 64 65 66 67 68

69

7О 71 72 73 74 75 76 77 78

79

8О 81 82 83 84

ОО

О5

ОО

О5

ОО

О6

О2

О8

О4

ОО

О6

О2

О8

О4

ОО

О7

О4

О1

О8

О5

О2

О9

О6

О3

Оо

о8

О6

О4

О2

Продолжение табл.I

1

I I

1

1

I

1

1

1

1

I

I

О6

67

О8

О9

О

2 3 4 5 6 7 8 9 О 1

22

23

24

25

26

27

28

29 3

31 32 33 34

О

IО

Iо

Iо

1о

Iо

1о

1о

го

1о

1о

1о

1о

Iо

1о

1о

Iо

1с

Iо

1о

1 I 1 1 I I t I 1

Iо

1о

Iо

iо

1t

II

11

1I

1I

II

I1

1I

If

I1

II

1I

1I

tI

II

1I

I1

1I

II

11

II

II

11

11

5 5 5 6 6

6I3

7I3

814

914

010

1Iq

2t1

6311 64 12 6513 66 13 6714 68 14

69 1 S 70 1 (И

i fO 1 1 7342

74 II 2 7513 7 6 I 4 7 714 78 15 7916

1 I 80 10

1181

I I

I I

I 0 8 2 11 8312

I 3

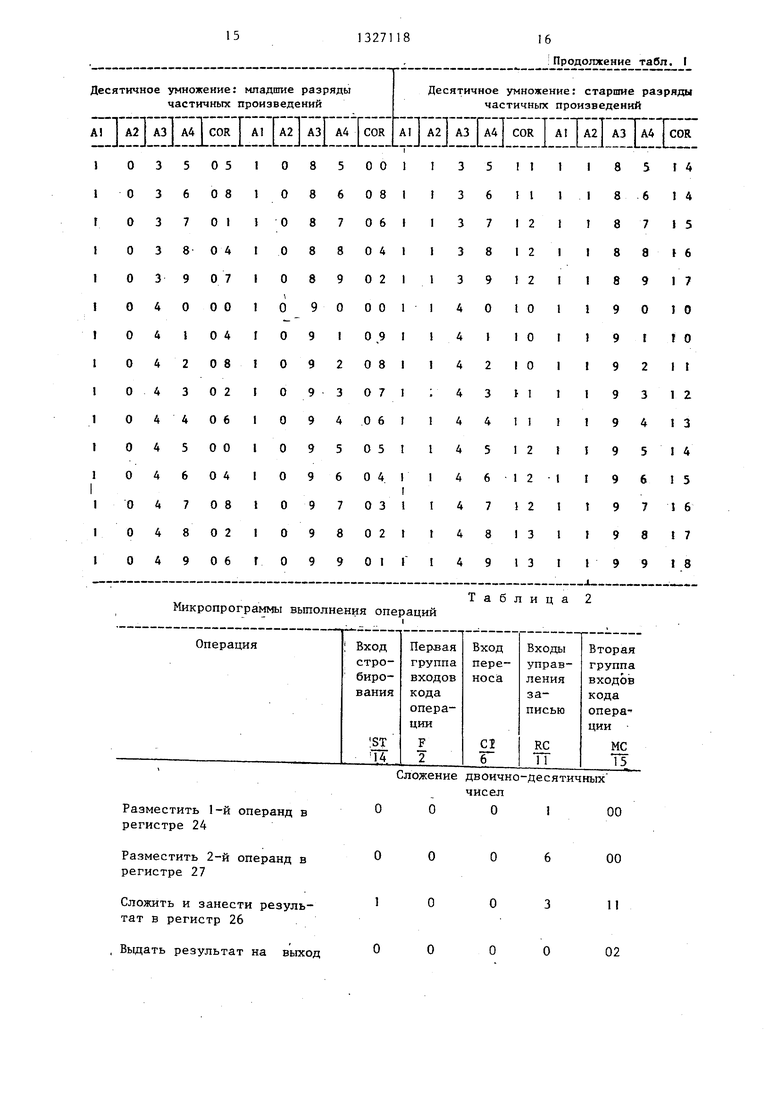

Микропрограммы выполнения операций

Разместить 1-й операнд в регистре 24

Разместить 2-й операнд в регистре 27

Сложить и занести результат в регистр 26

Выдать результат на выход

:Продолжение табл. I

Таблица 2

Сложение двоично-десятичных чисел

000100

ОО

00

11

02

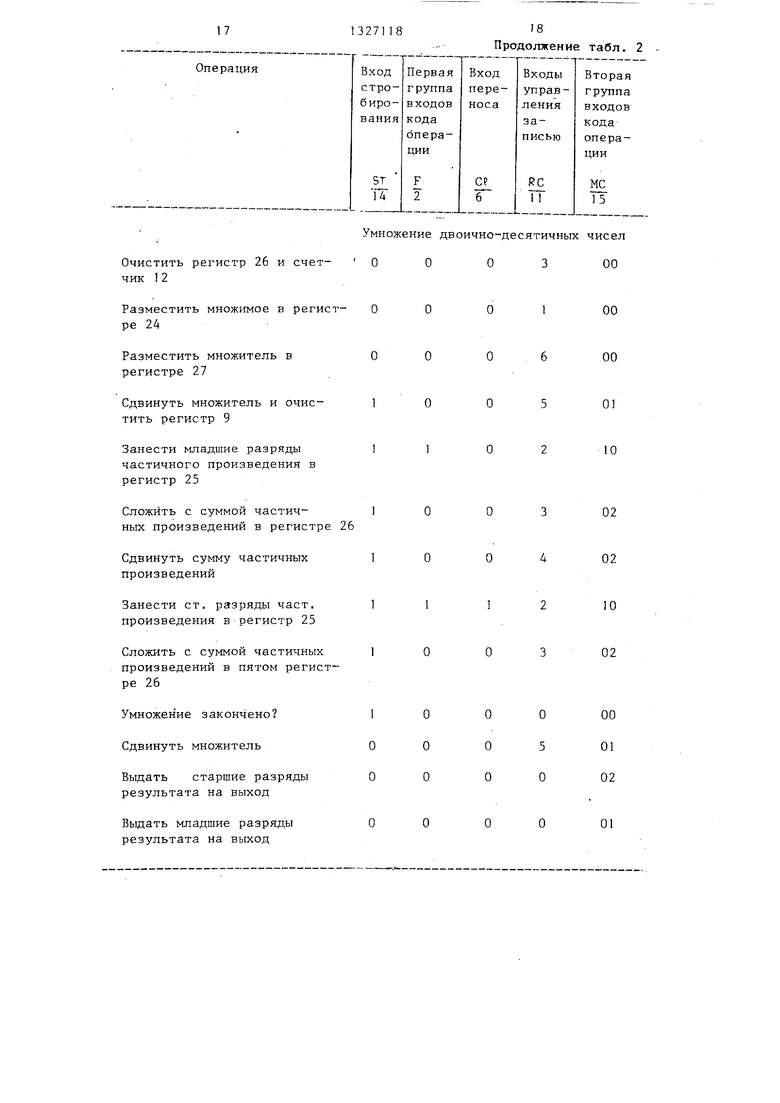

Очистить регистр 26 и счет чик 2

Разместить множимое в регире 24

Разместить множитель в регистре 27

Сдвинуть множитель и очистить регистр 9

Занести младшие разряды частичного произведения в регистр 25

Сложить с суммой частичных произведений в регистр

Сдвинуть сумму частичных произведений

Занести ст. разряды част, произведения в регистр 25

Сложить с суммой частичных произведений в пятом регисре 26

Умножение закончено Сдвинуть множитель

Выдать старшие разряды результата на выход

Бьщать младшие разряды результата на выход

О

00

00

00

01

02

02

10

02

01

.J0ut.l

| название | год | авторы | номер документа |

|---|---|---|---|

| ОПЕРАЦИОННЫЙ БЛОК | 1993 |

|

RU2034330C1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559340A1 |

| Процессор для обработки массивов данных | 1982 |

|

SU1381532A1 |

| Микропроцессор | 1984 |

|

SU1179363A1 |

| Микропроцессорное устройство для цифрового преобразования координат | 1982 |

|

SU1104523A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Микропрограммный процессор | 1987 |

|

SU1553984A1 |

| Устройство для умножения | 1984 |

|

SU1176325A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

Изобретение относится к вычислительной технике и может найти применение при построении быстродействующих универсальных ЭВМ. Цель изобретения - повьппение быстродействия устройства при выполнении двоично-десятичных операций. Вычисли- , тельное устройство содержит п соединенных по цепи переноса операционных блоков 1, первый и второй регистры 8, 9, дешифратор 10, счетчик 12. Операционный блок включает в себя запоминающий узел (для хранения таблиц сложения и умножения), первый и второй мультиплексоры, с первого по четвертый регистры. Цель изобретения достигается благодаря введению первого и второго регистров, счетчика и дешифратора. 4 ил., 2 табл.

СнАЧАЙО

Раместить 2 операнд 6 peeucmpet

(конец 3 «US

С тч/(йо )

| Операционный модуль | 1982 |

|

SU1083198A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Операционное устройство | 1982 |

|

SU1113805A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-30—Публикация

1986-03-18—Подача