Изобретение относится к вычислительной технике и может найти применение в многомашинных и многопроцессорных системах для распределения нагрузки между процессорами.

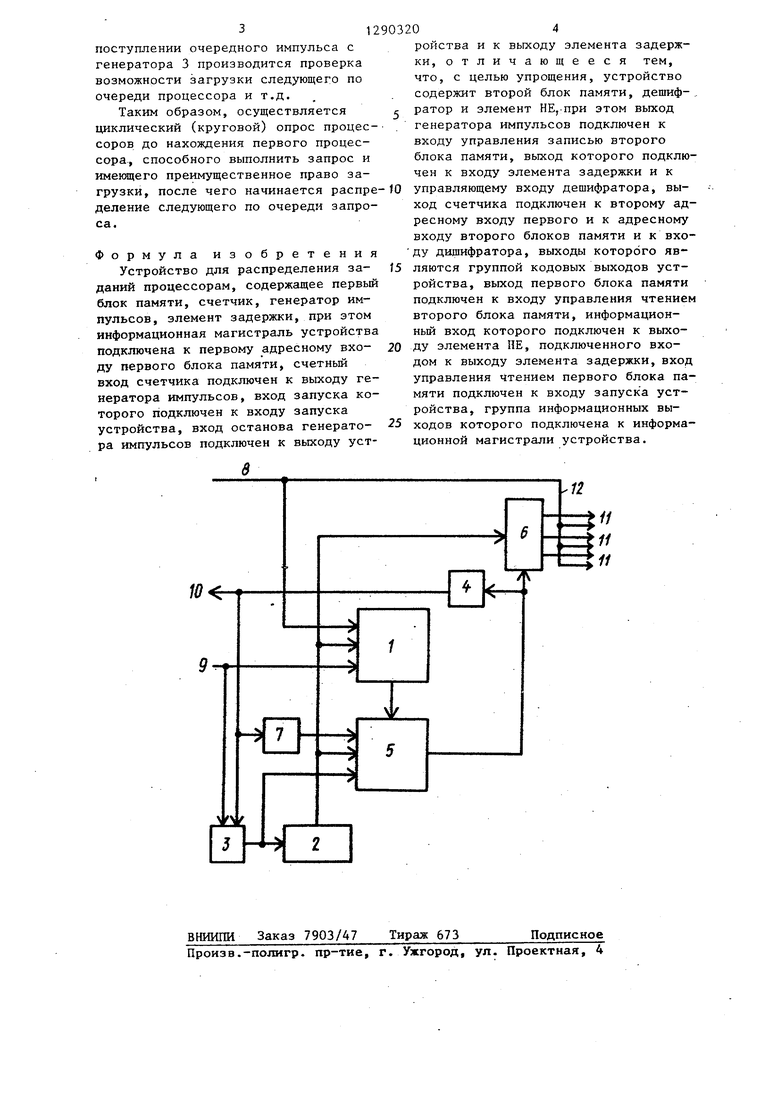

На чертеже пре;цставлена структурная схема устройства.

Устройство содержит блок памяти 1, счетчик 2, генератор импульсов 3 элемент задержки 4, блок памяти 5, дешифратор 6 и элемент НЕ 7, информационную магистраль 8, вход 9 запуска, сигнальный выход 10, группу кодовых выходов 11, информационные выходы 12.

Работа устройства заключается в том, что оно осуществляет динамическое распределение запросов по процессорам (ЭВМ) с учетом их функне был загружен в предьщущем цикле, то сигналом с выхода блока памяти 5 производится выборка дешифратора 6, подключенного к выходу счетчика 2, задаюш;его адрес выбираемого процессора. Унитарным кодом с выхода дешифратора 6 производится выборка загружаемого процессора. При этом сигнал с выхода дешифратора подается на вход прерывания процессора. Код запрашиваемой функции (вектор прерывания) воспринимается процессором ЭВМ с магистрали 8 (выходы 12). После загрузки выбранного процессора с некоторой задержкой на элементе 4 формируется сигнал подтверждения завершения распределения очередного запроса. По этому сигналу на вькоде 10 источник нагрузки подает

циональных возможностей. Функциональ-20л в устройство следующий предназначенные возможности процессоров отображаются в блоке памяти 1. При этом если данный процессор способен выполнить данную функцию, в соответствующую ячейку блока памяти 1 заносится М, если нет, то О.

Для обеспечения равномерности загрузки процессоров преимущество по загрузке дается процессорам, которые при распределении предыдущих запросов не были загружены. Для реализации этого принципа распределения в устройство вводится блок памяти 5, в соответствующей ячейке ко- ,. торого записывается О, если в предьщущих циклах загрузки он не был загружен. В противном случае в ячейке блока памяти 5 записана 1.

Рассмотрим более подробно процесс распределения запросов, поступающих на магистраль 8 и сопровождаемых сигналом на входе 9. По сигналу на входе 9 происходит запуск генератора импульсов 3, связанного с тактовым входом .счетчика 2, содержимое которого определяет выбор процессора, проверяемого на возможность загрузки. Выход счетчика 2 связан с адресными входами блоков памяти 5 и 1. Код запрашиваемой функции по магистрали 8 одновременно является адресом строки блока памяти 1. Если выбранный процессор способен выполнить запрашиваемую функцию, то на выходе блока памяти 1 формируется 1, осуществляющая выборку блока памяти 5. Если в ячейке блока памя- .ти 5 содержится О, т.е. процессор

25

30

35

ный для распределения запрос. Сигналом с выхода элемента задержки 4 производится остановка генератора импульсов 3, по заднему фронту импульса с которого (поступающего на вход записи блока памяти 5) при наличии сигнала на выходе блока памяти 5 в соответствующую ячейку блока памяти заносится 1.

Если выбранный процессор способен выполнить запрашиваемую функцию, но в соответствующей ячейке блока памяти 5 находится 1 (данный процессор был загружен на предьщущем цикле), то при выборке блока памяти 5 на его выходе сигнал не формируется и процессор не загружается. Сигнал подтверждения на выходе 10 в этом случае также не вырабатывается, поэтому по заднему фронту импульса,. с генератора 3 происходит запись О в соответствующую ячейку блока памяти 5, в результате чего при следую- 45 щем цикле выборки данного процессора он будет иметь преимущественное право по загрузке. При следующем импульсе с генератора 3 содержимое счетчика 2 увеличивается и происхо- 50 дит проверка следующего процессора на возможность загрузки в него запрашиваемой функции. Если данный процессор не способен выполнить запрашиваемую функцию, то на выходе 55 блока памяти 1 формируется О и

выборки блока памяти 5 не происходит, сигнал на его выходе не формируется и загрузки процессора не происходит. В этом случае, как и раньше, при

40

не был загружен в предьщущем цикле, то сигналом с выхода блока памяти 5 производится выборка дешифратора 6, подключенного к выходу счетчика 2, задаюш;его адрес выбираемого процессора. Унитарным кодом с выхода дешифратора 6 производится выборка загружаемого процессора. При этом сигнал с выхода дешифратора подается на вход прерывания процессора. Код запрашиваемой функции (вектор прерывания) воспринимается процессором ЭВМ с магистрали 8 (выходы 12). После загрузки выбранного процессора с некоторой задержкой на элементе 4 формируется сигнал подтверждения завершения распределения очередного запроса. По этому сигналу на вькоде 10 источник нагрузки подает

в устройство следующий предназначен5

0

5

ный для распределения запрос. Сигналом с выхода элемента задержки 4 производится остановка генератора импульсов 3, по заднему фронту импульса с которого (поступающего на вход записи блока памяти 5) при наличии сигнала на выходе блока памяти 5 в соответствующую ячейку блока памяти заносится 1.

Если выбранный процессор способен выполнить запрашиваемую функцию, но в соответствующей ячейке блока памяти 5 находится 1 (данный процессор был загружен на предьщущем цикле), то при выборке блока памяти 5 на его выходе сигнал не формируется и процессор не загружается. Сигнал подтверждения на выходе 10 в этом случае также не вырабатывается, поэтому по заднему фронту импульса,. с генератора 3 происходит запись О в соответствующую ячейку блока памяти 5, в результате чего при следую- 5 щем цикле выборки данного процессора он будет иметь преимущественное право по загрузке. При следующем импульсе с генератора 3 содержимое счетчика 2 увеличивается и происхо- 0 дит проверка следующего процессора на возможность загрузки в него запрашиваемой функции. Если данный процессор не способен выполнить запрашиваемую функцию, то на выходе 5 блока памяти 1 формируется О и

выборки блока памяти 5 не происходит, сигнал на его выходе не формируется и загрузки процессора не происходит. В этом случае, как и раньше, при

0

поступлении очередного импульса с генератора 3 производится проверка возможности загрузки следующего по очереди процессора и т.д. ,

Таким образом, осуществляется циклический (круговой) опрос процессоров до нахождения первого процессора, способного выполнить запрос и имекяцего преимущественное право загрузки, после чего начинается распре деление следующего по очереди запроса.

Формула изобретения

Устройство для распределения заданий процессорам, содержащее первьй блок памяти, счетчик, генератор импульсов, элемент задержки, при этом информационная магистраль устройства подключена к первому адресному входу первого блока памяти, счетный вход счетчика подключен к выходу генератора импульсов, вход запуска которого подключен к входу запуска устройства, вход останова генератора импульсов подключен к выходу уст8

. 0

5

0

5

ройства и к выходу элемента задержки, отличающееся тем, что, с целью упрощения, устройство содержит второй блок памяти, дешифратор и элемент НЕ,-при этом выход генератора импульсов подключен к входу управления записью второго блока памяти, выход которого подключен к входу элемента задержки и к управляющему входу дешифратора, выход счетчика подключен к второму адресному входу первого и к адресному входу второго блоков памяти и к вхо- ду дищифратора, выходы которого являются группой кодовых выходов устройства, выход первого блока памяти подключен к входу управления чтением второго блока памяти, информационный вход которого подключен к выходу элемента НЕ, подключенного входом к выходу элемента задержки, вход управления чтением первого блока памяти подключен к входу запуск а устройства, группа информационных выходов которого подключена к информационной магистрали устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распределения заданий процессорам | 1985 |

|

SU1285473A1 |

| Устройство для распределения заданий процессорам | 1985 |

|

SU1285474A1 |

| Устройство для распределения заданий процессорам | 1985 |

|

SU1317438A1 |

| Устройство для распределения заданий процессорам | 1984 |

|

SU1205144A1 |

| Многоканальное устройство для распределения заданий процессорам | 1988 |

|

SU1711171A2 |

| Устройство для распределения заданий процессорам | 1990 |

|

SU1798783A1 |

| Устройство для распределения заданий процессорам | 1985 |

|

SU1278848A1 |

| Адаптивное вычислительное устройство | 1980 |

|

SU957214A1 |

| Многоканальное устройство для распределения заданий процессорам | 1988 |

|

SU1619287A1 |

| Многоканальное устройство для распределения заданий процессорам | 1987 |

|

SU1471191A1 |

Устройство для распределения заданий процессорам относится к вычислительной технике и может быть использовано в многомашинных и мультипроцессорных системах для распределения нагрузки. Изобретение может быть использовано в отказоустойчивых мультипроцессорных системах. Цель изобретения - упрощение устройства. Устройство содержит два блока памяти, счетчик, генератор импульсов, элемент задержки, дешифратор, элемент НЕ. Сущность изобретения заключается в том, что для упрощения в-него введены блок памяти, дешифратор и элемент НЕ. 1 ил

| Авторское свидетельство СССР 913377, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для распределения заданий процессорам | 1984 |

|

SU1205144A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-15—Публикация

1985-04-18—Подача