. (St) АДАПТИВНОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки сейсмической информации | 1984 |

|

SU1168963A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1319029A1 |

| Однородная вычислительная система | 1984 |

|

SU1275458A1 |

| Устройство для обработки нечеткой информации | 1985 |

|

SU1564603A1 |

| Процессор с микропрограммным управлением | 1990 |

|

SU1700564A1 |

| Устройство управления последовательностью операций цифрового вычислителя | 1984 |

|

SU1198521A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство для обработки выражений языков программирования | 1981 |

|

SU1016790A1 |

| Микро-ЭВМ | 1982 |

|

SU1124316A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1386998A1 |

Изобретение относится к вычислительной технике, в частности к адаптивным вычислительным устройствам и может быть использовано при построении многопроцессорных вычислительных систем. Известно адаптивное вычислительное устройство, содержащее вычислительные модули, блок сравнения, кольцевые регистры, логические элементы 1. Однако это устройство характеризуется низкой производительностью вслед ствие последовательного вычислительного процесса, Известно адаптивное вычислительное устройство, содержащее вычислительные модули, блок памяти реконфигурации, блок управляющей памяти, блок оперативной памяти, -четыре распределителя импульсов и входной регистр, причем вход блока оперативной памяти соединен с адресными выходами вычислительных модулей, а выход этого блока подключен -к первым информационным входам вычислительных модулей, вторые информационные входы которых соединены с первым выходом входного регистра, первые и вторые управляющие входы вычислительных модулей подключены соответственно к первому выходу первого распределителя импульсое и выходу блока управляющей памяти, который соединен с входом установки О первого распределителя импульсов и входом разрешения приема входного регистра, информационный вход входного регистра подключен к информационному входу устройства, а счетные входы первого и второго распределителей импульсов - к тактовому входу устройства, второй выход входного регистра и первый выход второго распредел11теля импульсов соединены с входом адреса строки блока уп равляющей памяти, второй выход второго распределителя импульсов подключен к счетному входу третьего распределителя импульсов, второй выход п.ервого распределителя импульсов и первый выход четвертого распределителя импульсов соединены с входом адреса столбца блока управляющей памяти и третьими управляющими входами первой группы вычислительных модулей, первый вход установки О второго распределителя импульсов и входу установки 1 третьего распределителя импульсов подключены к входу установки устройства, третий выход .второго распределителя импульсов соединен с входом адреса столбца блока памяти реконфигурации, выход которого подключен к входам настройки первой группы вычислительных модулей 2. . В известном устройстве число вычислительных модулей, настроенных на выполнение каждой функции, постоянно и не зависит от потока запросов на выполнение различных функций. Вследствие этого производительность устройства не всегда удовлетворяет пред являемым требованиям. Цель изобретения - повышение про изводительности устройства. Поставленная цель достигаеУся тем что устройство содержит счетчики, де шифратор, схему сравнения, триггер управления и мультиплексор, при этом информационные входы мультиплексора соединены с информационными выходами вычислительных модулей, адресный вхо мультиплексора подключен к второму выходу первого распределителя импуль сов, а выход мультиплексора соединен с входом разрешения выборки блока управляющей памяти, выход схемы срав нения подключен к входу блокировки управляющей памяти, управляющему вхо ду блока памяти реконфигурации, входам вычитания счетчиков, второму вхо ду установки О второго распределителя импульсов и счетному входу четвертого распределителя импульсов, второй выход которого соединен с вхо дами установки О счетчиков и три|- гера управления, вход установки Т триггера управления подключен к вход установки устройства, первый выход . триггера управления соединен с управ ляющими входами второго и четвертого распределителя импульсов, .а второй выход - с управляющим входом первого распределителя импульсов и входом ра

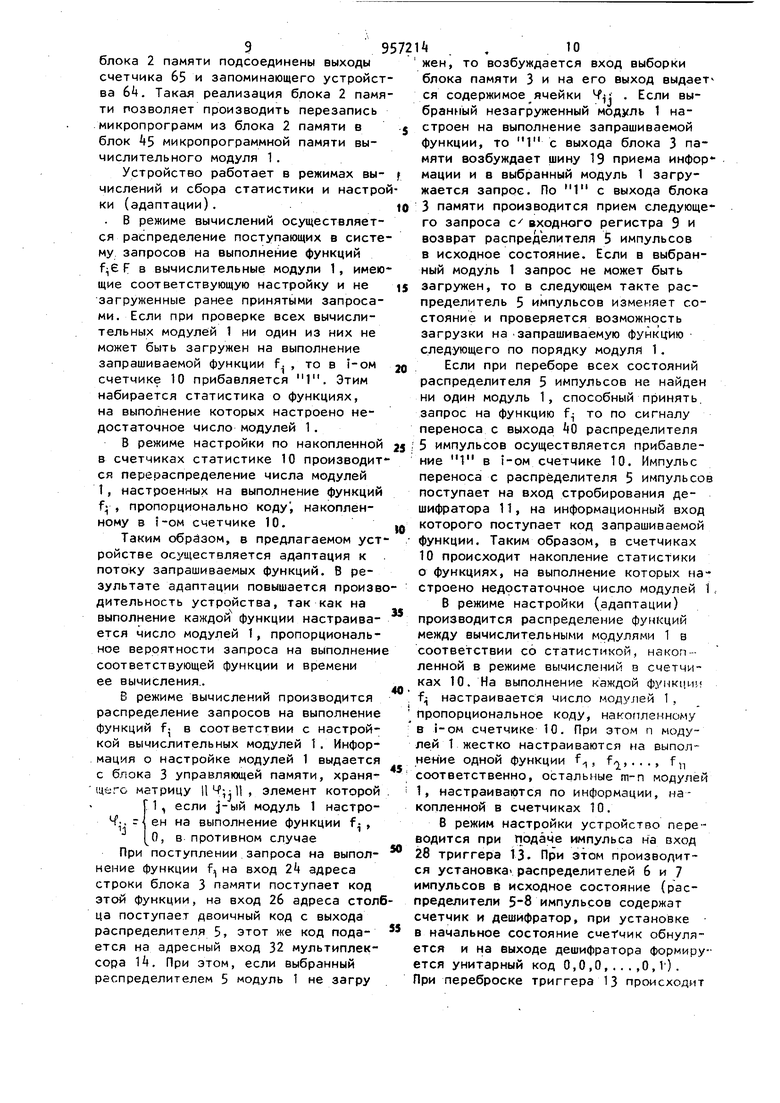

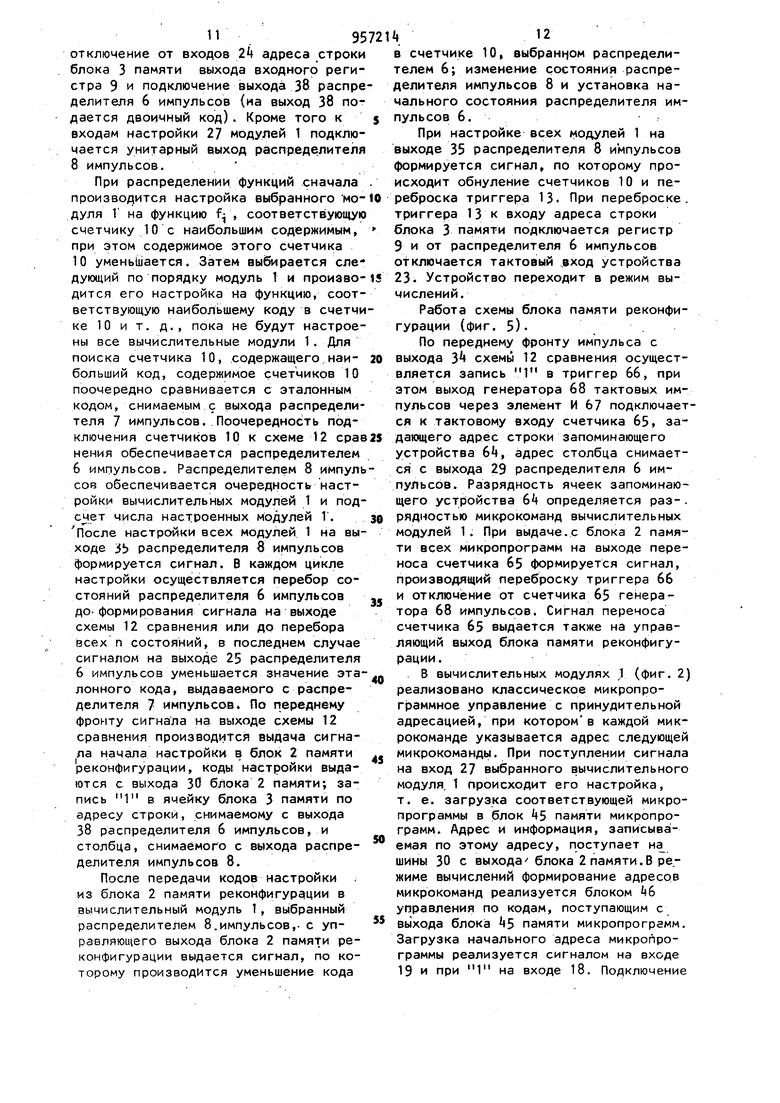

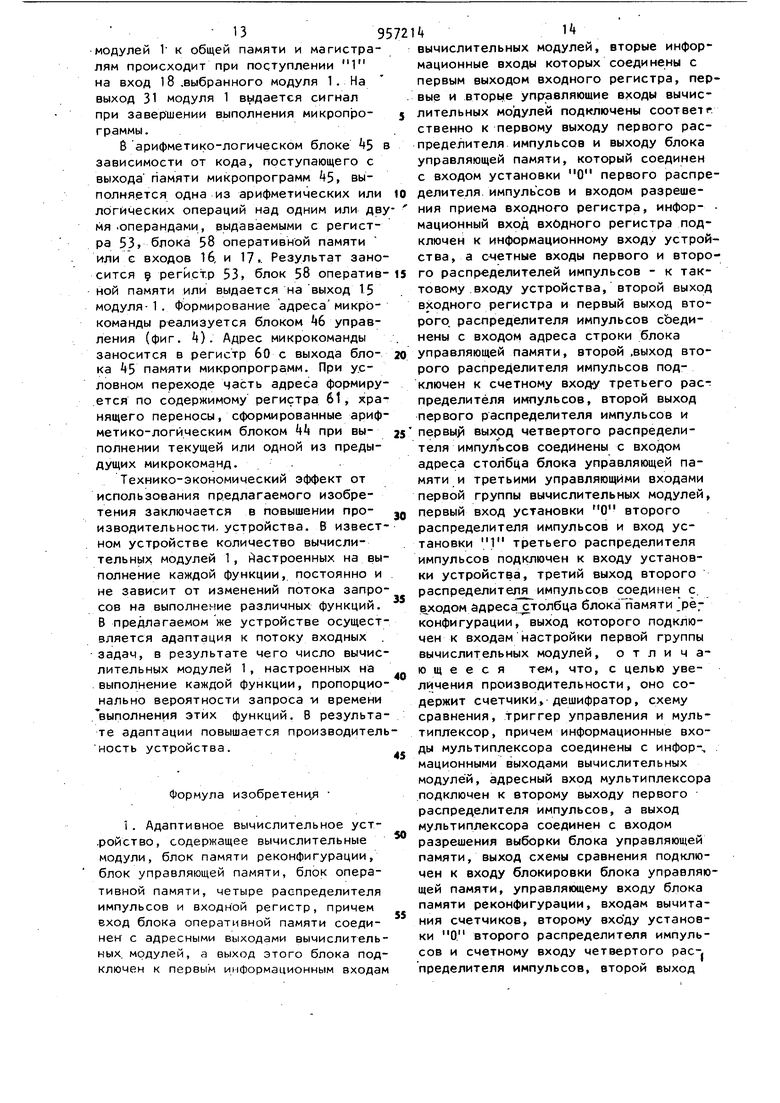

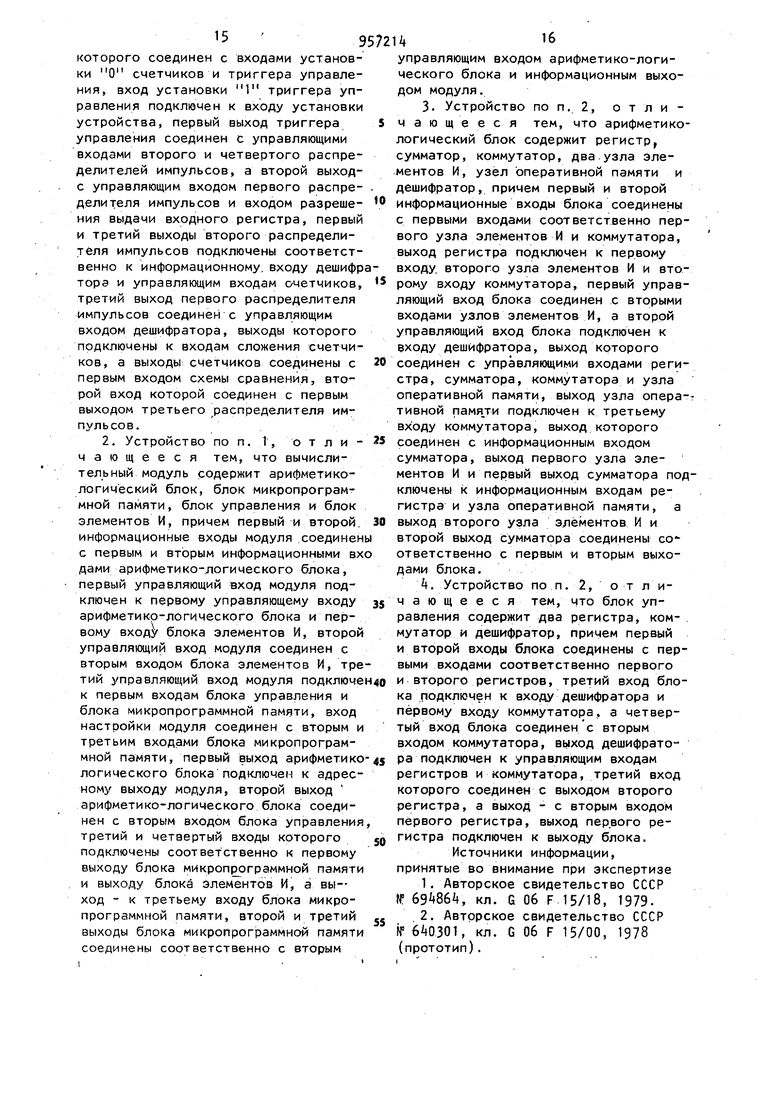

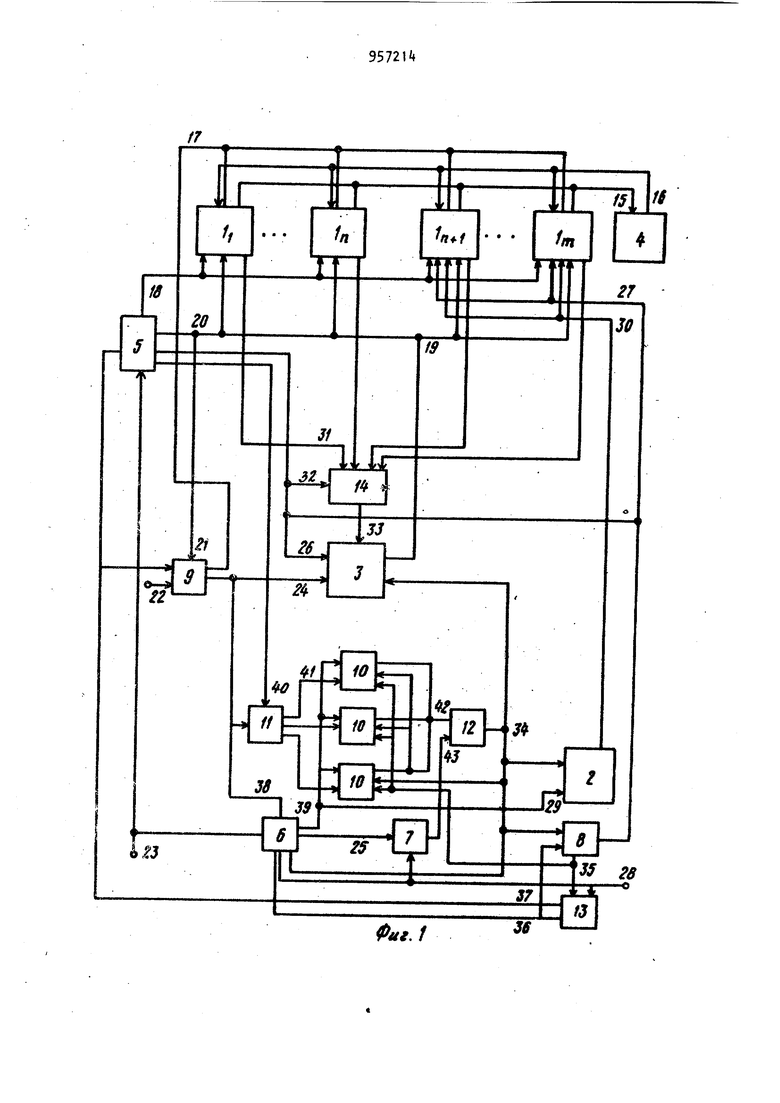

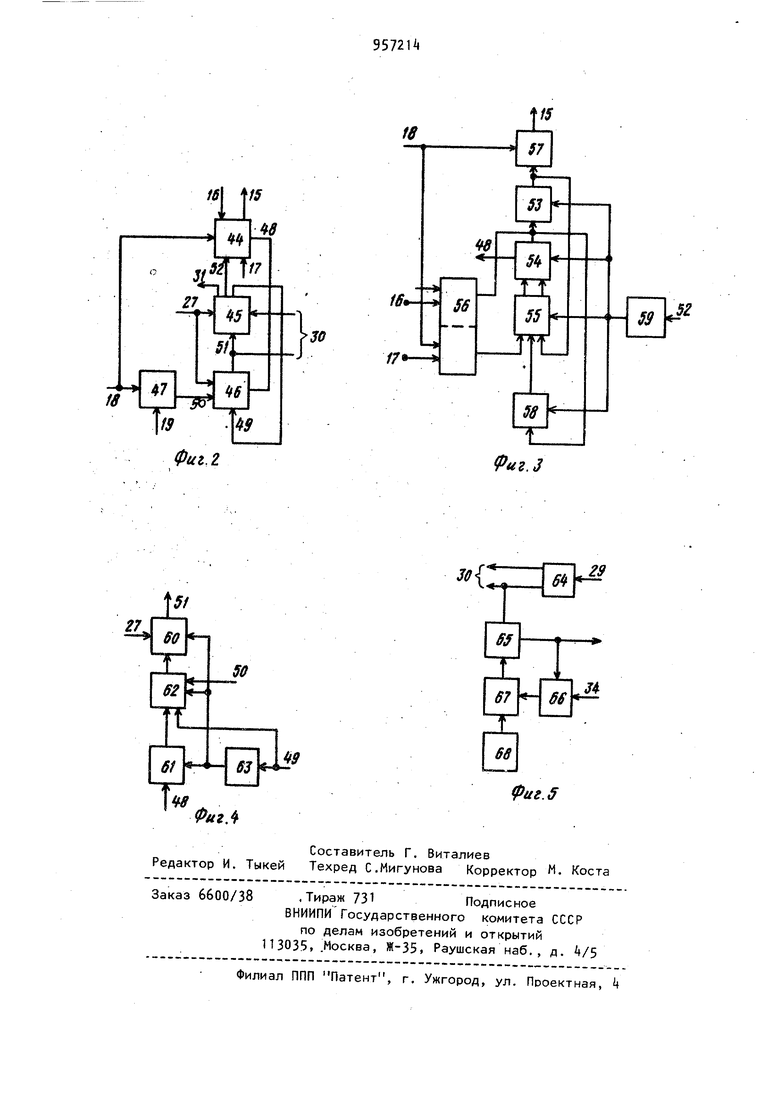

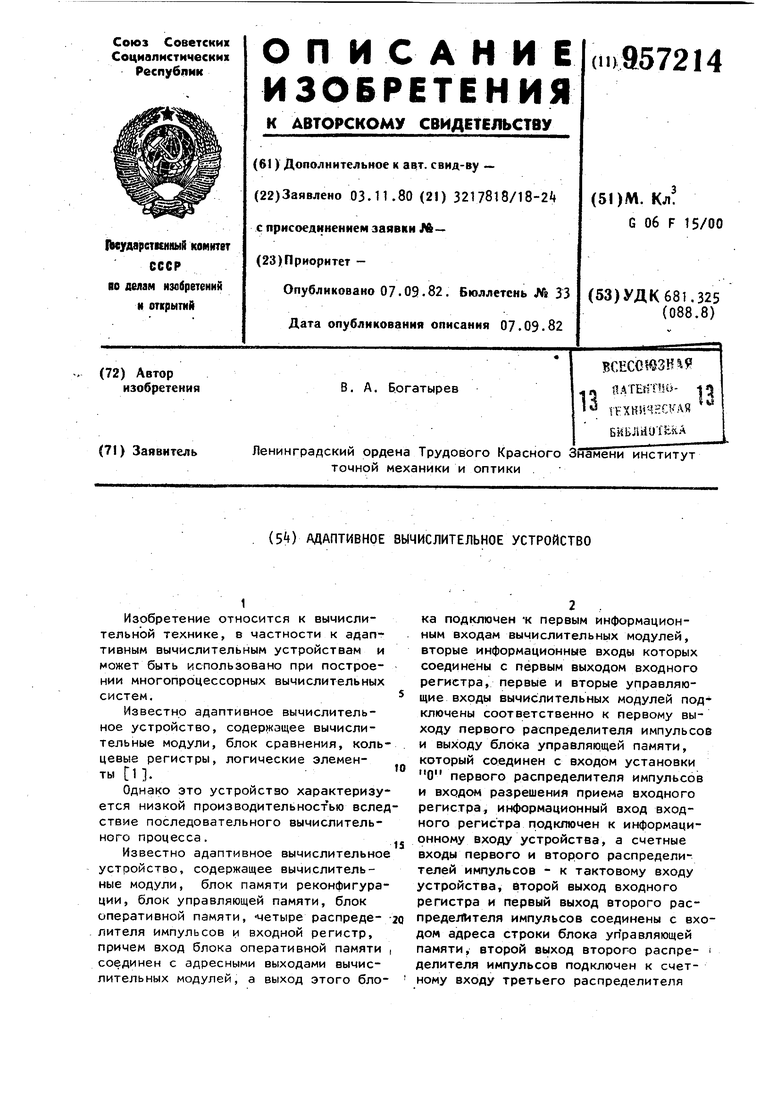

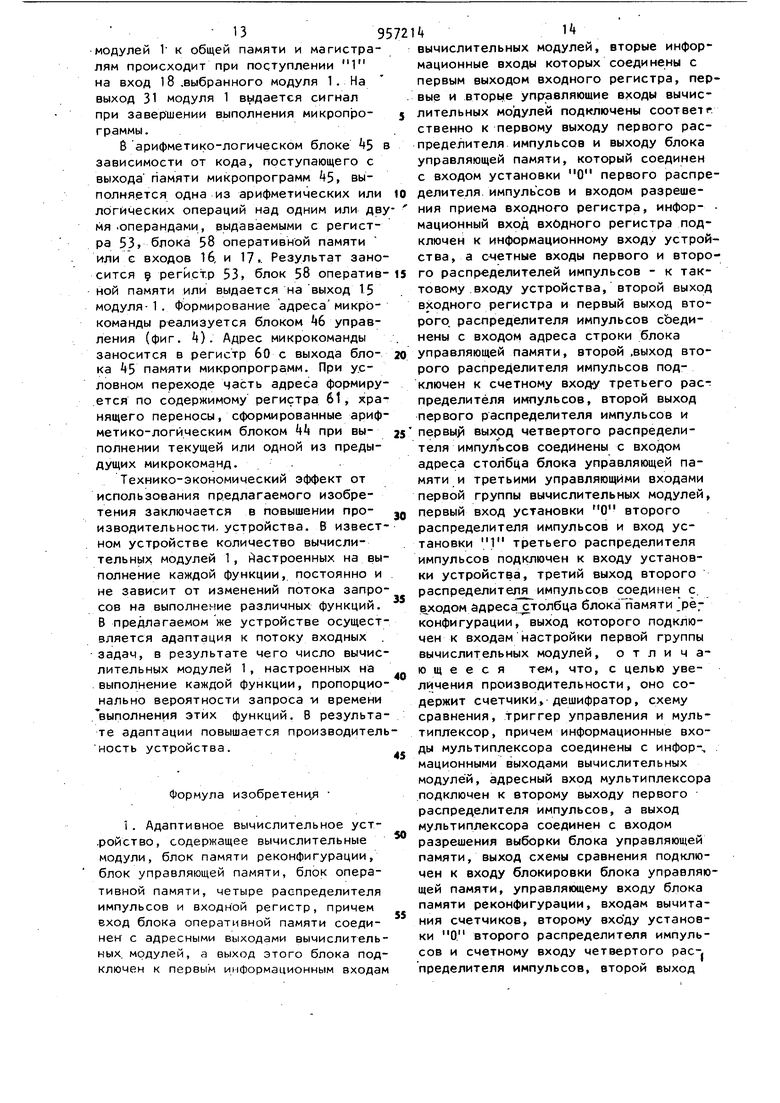

решения выдачи входного регистра, первый и третий выходы второго распределителя импульсов подключены соответкоммутатора, первый управляющий вход блока соединен с вторыми входами узлов элементов И, а второй управственно к информационному входу дешифратора и управляющим входам счетчиков, третий выход первого распределителя импульсов соединен с управляющим входом дешифратора, выходы которого подключены к входам сложения счетчиков, а выходы счетчиков, соединены с первым входом схемы, сравнения, второй вход которой соединен с первым выходом третьего распределителя импульсов. Вычислительный модуль содержит арифметико-логический блок, блок микропрограммной памяти, блок управления и блок элементов И, причем первый и второй информационные входы модуля соединены с первым и вторым информа- . ционными входами арифметико-логического блоКа, первый управляющий вход модуля подключен к первому управляющему входу арифметико-логического блока и первому входу блока элементов И, второй управляющий вход модуля соединен с вторым входом блока элементов И, третий управляющий вход .модуля подключен к первым входам блока управления и блока микропрограммной памяти, вход настройки модуля соединен с вторым и третьим входами блока микропрограммной памяти, первый выход арифметико-логического блока подключен к адресному . выходу модуля, второй выход арифметико-логического блока соединен с вторым входом блока управления, третий и четвертый входы которого подключены соответственно к первому выходу блока микропрограммной памяти и выходу блока элементов И, а выход - к третьему входу блока микропрограммной памяти, второй и третий выходы блока микропрограммной памяти соединены соответственно с вторым управляющим входом арифметико-логического блока и информационным выходом модуля. Арифметико-логический блок содержит регистр, сумматор, коммутатор, два узла элементов И, узел оперативной памяти и дешифратор, при этом первый и второй информационные входы блока соединены с первыми входами соответственно первого узла элементов И и коммутатора, выход регистра подключен к первому входу второго узла элементов И и второму входу ляющий вход блока подключен к дешифратора, выход которого соединен с управляющими входами регистра, сум матора, коммутатора и узла оперативной памяти, выход узла оперативной памяти подключен к третьему входу коммутатора, выход которого соединен с информационным входом сумматора, в ход первого узла элементов И и первы выход сумматора подключены к информа ционным входам регистра и узла опера тивной памяти, а выход второго узла элементов И и второй выход сумматора соединены соответственно с первым и вторым выходами блока. Блок управления содержит два регистра, коммутатор и дешифратор, при чем первый и второй входы блока соединены с первыми входами соответстве но первого и второго регистров, третий вход блока подключен к входу дешифратора и первому входу коммутатор а четвертый вход блока соединен с вторым входом коммутатора, выход дешифратора подключен к управляющим входам регистров и коммутатора, третий вход которого соединен с выходом второго регистра, а выход - с вторым входом первого регистра, выход первого регистра подключен к выходу блока. На фиг, 1 приведена структурная схема предлагаемого устройства; на фиг. 2 - вариант вычислительного модуля; на фиг. 3 - вариант арифметикологического блока; на фиг. k - вариант блока управления; на фиг. 5 структура блока памяти реконфигурации Адаптивное вычислительное устройст во (фиг. 1) содержит вычислительные модули 1, блок 2 памяти реконфигурации, блок 3 управляющей памяти, блок k оперативной памяти, четыре распределителя 5-8 импульсов, входной регистр 9f счетчики 10, дешифратор 11, схему 12 сравнения, триггер 13 управления, мультиплексорv14, Вход 15 блока Ц оперативной памяти соединен с выходами вычислительных модулей 1, а выход 16 этого блока подключен к первым информационным входам вычисли тельных модулей 1, вторые информационные входы 17 которых соединены с первым выходом входного регистра 9Первые 18 и вторые 19 управляющие входы вычислительных модулей 1 подключены соответственно к первому выходу первого распределителя импульсов 5 и выходу блока управляющей 9 входу памяти 3. который соединен с входом 20 установки О первого распределителя импульсов 5 и входом 21 разрешения приема входного регистра 9, информационный вход 22 входного регистра 9 подключен к информационному входу устройства, а счетныб входы первого 5 и второго 6 распределителей импульсов - к тактовому входу 23 устройства, второй выход входного ре- . гис;тра 9 и первый выход второго распределителя импульсов 5 соединены с входом 2k адреса строки блока 3 управ ляющей памяти, второй выход 25 второго распределителя 6 импульсов подключен к счетному входу третьего распределителя 7 импульсов, второй выход первого распределителя импульсов 5 и первый выход четвертого распределителя 8 импульсов соединены с входом 26 адреса столбца блока 3 управляющей памяти и третьими управляющими входами 27 первой г;руппы вычислительных модулей J, первый вход установки О второго распределителя 6 импульсов и вход установки 1 третьего распределителя 7 импульсов подключены к входу 28 установки устройства, третий выход второго распределителя б импульсов с входом 29 адреса столбсоединенца блока 2 памяти реконфигурации, выход которого подключен к входам 30 настройки первой группа вычислительных модулей 1. Информационные входы И мультиплексора 1ч соединены с ииформационныки выходами 31 вычислительных модулей 1. Адресный вход 32 мультиплексора 14 подключен к второму выходу первого распределителя импульсов 5, а выход мультиплексора I соединен с входом 33 разрешения выборки блока 3 управляющей памяти. Выход 3 схемы 12 сравнения подключен к входу блокировки управляющей памяти 3, управляющему входу блока 2 памяти реконфигурации, входам вычитания счетчикс а 10, второму входу установки О второго распределителя 6 импульсов и ; счетному входу четвертого распределителя 8 импульсов, второй выход 35 которого соединен с входами установки О счетчиков 10 и триггера 13 управления. Вход установки 1 триггера 13 управления подключён к входу 28 установки устройства, первый выход 36 триггера 13 управления соединен с управляющими входами второго 6 и четвертого 8 распределителей импульсов, а второй выход 37 .- с управляющим входом первого распределителя 5 импульсов и входом разрешения выдачи входного регистра 9, первый и третий выходы второго распределителя 6 импупьсов подключены соответственно к информационномувходу 38 дешифратора 11 и управляющим входам 39 счетчиков 10, третий выход первого распределителя 5 импульсов соединен с управляю щим входом АО дешифратора 11, выходы которого подключены к входам 1 слож ния, сметчиков 10, выходы счетчиков 10 соединены с первым входом Ц2 схемы 12 сравнения, второй вход которой соединен с первым выходом третьего распределителя 7 импульсов. Вычислительный модуль 1 (фиг, 2) содержит арифметико-логический блок k блок kS микропрограммной памяти, блок 46 управления и блок 7 элементов И, причем первый 16 и второй 17 информационные входы модуля 1 соединены с первым и вторым информационными входами арифметико-логического блока kk, первый управляющий вход 18 модуля 1 подключен к первому управляющему входу арифметико-логического блока kk и первому входу блока kj элементов И, второй управляющий вход 19 модуля 1 соединен с вторым входом блока 7 элементов И, третий управляющий вход 27 модуля 1 подключен к первыг(( входам блока 6 управления и блока AS микропрограммной памяти, вход настройки 30 модуля 1 соединен с вторым и третьим входами блока 45 микропрограммной памяти, первый выход арифметико-логического блока kk подключен к выходу 15 модуля 1 , второй выход арифметико-логического блока k соединен с вторым входом блока 6 управления, третий 9 и четвертый 50 входы которогй подключены соответственно к перво му выходу блока 5 микропрограммной памяти и выходу блока 47 элементов И, а выход 51 .к третьему входу бло ка 5 микропрограммной памяти, второй и третий выходы блока S микропрограммной памяти -соединены соответственно с вторым управляющим входом арифметико-логического блока 52 и информационным выходом 31 модуля Т Арифметико-логический блок k содержит регистр 53, сумматор 5, комм татор 55, два узла элементов.И 56 и 57, узел 58 оперативной памяти и дешифратор 59, при этом первый 16 и второй 17 информационные входы блока соединены с первым и вторым входами первого узла элементов И 56, первый выход которых подключены к первому входу коммутатора 55. Выход регистра 53 подключен к первому входу второго узла элементов И 57 и второму входу коммутатора 55- Первый управляющий вход 18 блока соединен с вторыми входами узлов элементов И 56 и 57, а второй управляющий вход 52 блока под,ключен к входу дешифратора 59, выход которого соединен с управляющими входами регистра 53 сумматора 5, коммутатора 55 и узла 58 оперативной памяти, выход узла оперативной памяти 58 подключен к третьему входу коммутатора 55 выходы которого соединены с информационными входами сумматора 5. Второй выход первого узла элементов И 5б и первый выход сумматора B по/включены к информационным входам регистра 53 и узла 58 оперативной памяти, а выход второго узла элементов И 57 и второй выход сумматора 5 соединены соответственно с первым и вторым выходами блока. Блок управления содержит два регистра 60 и 61, коммутатор 62 и дешифратор 63, причем первый 27 и второй 50 входы блока соединены с первыми входами соответственно первого 60 и второго 61 регистров. Третий вход 49 блока Подключен к входу дешифратора 63 и первому входу коммутатора б2, а четвертый вход 50 блока соединен с вторым входом коммутатора б2, выход дешифратора подключен к управляющим входам регистров 60, 61 и коммутатора 62, третий вход которого соединен с выходом второго регистра 61, а выход - с вторым входом первого регистра 60, выход первого регистра 60 подключен квыходу 51 ёяока. Блок памяти реконфигурации (фиг. 5) содержит запоминающее устройство 64, счетчик б5, элемент И 66, триггер б7 и генератор 68 импульсов. Вход адреса строки запоминающего устройства 64 подключен к информационному выходу счетчика 65, выход переноса которого подключен к первому входу триггера 67, второй вход которого связан с входом 34 блока 2, а выход - с первым входом элемента И 66, второй вход которого подключен к генератору 68 импульсов, а выход - к тактовому входу счетчика 65. Адресный вход столбца запоминающего устройства 64 подсоединен к входу 29 блока 2. К выходу 30 блока 2 памяти подсоединены выходы счетчика 65 и запоминающего устройст ва 64. Такая реализация блока 2 памя ти позволяет производить перезапись микропрограмм из блока 2 памяти в блок 5 микропрограммной памяти вычислительного модуля 1. Устройство работает в режимах вычислений и сбора статистики и настро ки (адаптации). В режиме вычислений осуществляется распределение поступающих в систе му запросов на выполнение функций F в вычислительные модули 1, имею щие соответствующую настройку и не загруженные ранее принятыми запросами. Если при проверке всех вычислительных модулей 1 ни один из них не может быть загружен на выполнение запрашиваемой функции f. , то в i-ом счетчике 10 прибавляется 1. Этим набирается статистика о функциях, на выполнение которых настроено недостаточное число модулей 1. В режиме настройки по накопленной в счетчиках статистике 10 производит ся перераспределение числа модулей 1, настроенных на выполнение функций f , пропорционально коду , накопленному в 1-ом счетчике 10. Таким обрезом, в предлагаемом уст ройстве осуществляется адаптация к потоку запрашиваемых функций. В результате адаптации повышается произв дительность устройства, так как на выполнение каждой функции настраивается число модулей 1, пропорциональное вероятности запроса на выполнени соответствующей функции и времени ее вычисления,. В режиме вычислений производится распределение запросов на выполнение функций f. в соответствии с настройкой вычислительных модулей 1. Информация о настройке модулей 1 выдается с блока 3 управляющей памяти, храня 1цего матрицу 11 11 , элемент которой 1, если j-ый модуль 1 настроен на выполнение функции f, 0, в противном случае При поступлении запроса на выполнение функции f на вход 2k адреса строки блока 3 памяти поступает код этой функции, на вход 26 адреса стол ца поступает двоичный код с выхода распределителя 5, этот же код подается на адресный вход 32 мультиплексора 1. При этом, если выбранный распределителем 5 модуль 1 не загру 9 жен, то возбуждается вход выборки блока памяти 3 и на его выход выдает ся содержимое ячейки . Если выбранный незагруженный модуль 1 настроен на выполнение запрашиваемой функции, то 1 с выхода блока 3 памяти возбуждает шину 19 приема информации и в выбранный модуль 1 загружается запрос. По 1 с выхода блока 3 памяти производится прием следующего запроса с/ входного регистра 9 и возврат распределителя 5 импульсов в исходное состояние. Если в выбранный модуль 1 запрос не может быть загружен, то в следующем такте распределитель 5 импульсов изменяет состояние и проверяется возможность загрузки на запрашиваемую функцгию следующего по порядку модуля 1. Если при переборе всех состояний распределителя 5 импульсов не найден ни один модуль 1, способный принять. запрос на функцию f то по сигналу переноса с выхода 0 распределителя 5 импульсов осуществляется прибавление 1 в i-ом счетчике 10. Импульс переноса с распределителя 5 импульсов поступает на вход стробирования дешифратора 11, на информационный вход которого поступает код запрашиваемой функции. Таким образом, в счетчиках 10 происходит накопление статистики о функциях, на выполнение которых настроено недостаточное число модулей 1. В режиме настройки (адаптации) производится распределение функций между вычислительными модулями 1 в соответствии со статистикой, накопленной в режиме вычислений в счетчиках 10. На выполнение каждой функция f настраивается число модулей 1, пропорциональное коду, накопленному в i-oM счетчике 10. При этом п модулей 1 жестко настраиваются на выполнение одной функции f, f, . . . , f, соответственно, остальные m-n модулей 1, настраиваются по информации, накопленной в счетчиках 10. В режим настройки устройство переводится при подаче импульса на вход 28 триггера 13. При этом производится установка- распределителей 6 и 7 импульсов в исходное состояние (распределители импульсов содержат сметчик и дешифратор, при установке а начальное состояние счегчик обнуляется и на выходе дешифратора формируется унитарный код 0,0,0,...,0,V). При переброске триггера 13 происходит 11 . 95 отключение от входов 24 адреса строки блока 3 памяти выхода входного регистра 9 и подключение выхода 38 распре делителя 6 импульсов (на выход 38 подается двоичный код). Кроме того к входам настройки 27 модулей 1 подключается унитарный выход распределителя 8 импульсов. При распределении функций сначала производится настройка выбранного модуля V на функцию f , соответствующую счетчику 10 с наибольшим содержимым, при этом содержимое этого счетчика 10 уменьшается. Затем выбирается следующий по порядку модуль 1 и производится его настройка На функцию, соответствующую наибол1эшему коду в счетчи ке 10 и т. д., пока не будут настроены все вычислительные модули 1. Для поиска счетчика 10, содержащего,наибольший код, содержимое счетчиков 10 поочередно сравнивается с эталонным кодом, снимаемым с выхода распределителя 7 импульсов. Поочередность подключения счетчиков 10 к схеме 12 cpae нения обеспечивается распределителем 6 импульсов. Распределителем 8 импуль сов обеспечивается очередность настройки вычислительных модулей 1 и подсчет числа настроенных модулей 1. После настройки всех модулей 1 на выходе ЗЬ распределителя 8 импульсов формируется сигнал. В каждом цикле настройки осуществляется перебор состояний распределителя 6 импульсов до-формирования сигнала на выходе схемы 12 сравнения или до перебора всех п состояний, в последнем случае сигналом на выходе 25 распределителя 6 импульсов уменьшается значение эта лонного кода, выдаваемого с распределителя 7 импульсов По переднему фронту сигнала на выходе схемы 12 сравнения производится выдача сигнала начала настройки в блок 2 памяти реконфигурации, коды настройки выдаются с выхода ЗО блока 2 памяти; запись М в ячейку блока 3 памяти по адресу строки, снимаемому с выхода 38 распределителя б импульсов, и столбца, снимаемого с выхода распределителя импульсов 8. После передачи кодов настройки из блока 2 памяти реконфигурации в вычислительный модуль 1, выбранный распределителем 8.импульсов,- с управляющего выхода блока 2 памяти реконфигурации выдается сигнал, по которому производится уменьшение кода 12 в счетчике 10, выбранном распределителем 6; изменение состояния распределителя импульсов 8 и установка начального состояния распределителя импульсов 6. При настройке всех модулей 1 на выходе 35 распределителя 8 импульсов формируется сигнал, по которому происходит обнуление счетчиков 10 и переброска триггера 13. При переброске, триггера 13 к входу адреса строки блока 3 памяти подключается регистр 9 и от распределителя 6 импульсов otключaeтcя тактовый .вход устройства 23. Устройство переходит в режим вычислений. Работа схемы блока памяти реконфигурации {фиг. 5). По переднему фронту импульса с выхода З схемы 12 сравнения осуществляется запись 1 в триггер 66, при этом выход генератора 68 тактовых импульсов через элемент И 67 подключается к тактовому входу счетчика б5, задающего адрес строки запоминающего устройства 6, адрес столбца снимается с выхода 29 распределителя 6 импульсов. Разрядность ячеек запоминающего устройства 64 определяется раз-. рядностью микрокоманд вычислительных модулей 1. При выдаче.с блока 2 памяти всех микропрограмм на выходе переноса счетчика б5 формируется сигнал, производящий переброску триггера 66 и отключение от счетчика 65 генератора 68 импульсов. Сигнал переноса счетчика б5 выдается также на управляющий выход блока памяти реконфигурации. В вычислительных модулях 1 (фиг. 2) реализовано классическое микропрог)эаммное управление с принудительной адресацией, при которомв каждой микрокоманде указывается адрес следующей микрокоманды. При поступлении сигнала на вход 27 выбранного вычислительного модуля. 1 происходит его настройка, т. е. загрузка соответствующей микропрограммы в блок kS памяти микропрограмм. Адрес и информация, записываемая по этому адресу, поступает на шины 30 с выхода/блока 2 памяти.В режиме вычислений формирование адресов микрокоманд реализуется блоком «б управления по кодам, поступающим с выхода блока 5 памяти микропрограмм. Загрузка начального адреса микропрограммы реализуется сигналом на входе 19 и при 1 на входе 18. Подключение -139 модулей V к общей памяти и магистралям происходит при поступлении 1 на вход 18 .выбранного модуля 1. На выход 31 модуля 1 выдается сигнал при завершении выполнения микропрограммы. 6 арифметико-логическом блоке 5 зависимости от кода, поступающего с выхода Намяти микропрограмм 5, выполняется одна из арифметических или логических операций над одним или дв мя .операндами, выдаваемыми с регистра 53, блока 58 оперативной памяти или с входов 16, и 17,. Результат зано сится 9 регист.р 53, блок 58 оператив ной памяти или выдается на выход 1-5 модуля-1. Формирование адреса микрокоманды реализуется блоком б управления (фиг. k}. Адрес микрокоманды заносится в регистр 60 с выхода блока kS памяти микропрограмм. При условном переходе часть адреса формиру ется по содержимому регистра 61, хра нящего переносы, сформированные ариф метико-логическим блоком kk при выполнении текущей или одной из предыдущих микрокоманд. . Технико-экономический эффект от использования предлагаемого изобретения заключается в повышении производительности. устройства. В извест ном устройстве количество вычислительных модулей 1, йастроенных на вы полнение каждой функции, постоянно и не зависит от изменений потока запро сов на выполнение различных функций. В предлагаемом же устройстве осущест вляется адаптация к потоку входных . задач, в результате чего число вычис лительных модулей 1, настроенных на .выполнение каждой функции, пропорцио нально вероятности запроса vi времени выполнения этих функций. В результа те адаптации повышается производител ность устройства. Формула изобретения 1. Адаптивное вычислительное уст.ройство, содержащее вычислительные модули, блок памяти реконфигурации, блок управляющей памяти, блок оперативной памяти, четыре распределителя импульсов и входной регистр, причем вход блока оперативной памяти соединен с адресными выходами вычислительных, модулей, а выход этого блока подключен к первым информационным входам ЦI вычислительных модулей, вторые информационные входы которых соединены с первым выходом входного регистра, первые и BTOpbie управляющие входы вычислительных модулей подключены соответг ственно к первому выходу первого распределителя импульсов и выходу блока управляющей памяти, который соединен с входом установки О первого распределителя импульсов и входом разрешения приема входного регистра, инфор- мационный вход входного регистра подключен к информационному входу устройства, а счетные входы первого и второго распределителей импульсов - к тактовому входу устройства, второй выход входного регистра и первый выход второго, распределителя импульсов сЪединены с входом адреса строки блока управляющей памяти, второй ,выход второго распределителя импульсов подключен к счетному входу третьего рас-; пределитёля импульсов, второй выход первого распределителя импульсов и первый выход четвертого распределителя импульсов соединены с входом адреса столбца блока управляющей памяти и третьими управляющими входами первой группы вычислительных модулей, первый вход установки О второго распределителя импульсов и вход установки 1 третьего распределителя импульсов подключен к входу установки устройства, третий выход второго распределителе импульсов соединен с. входом адреса толбца блока памяти рёконфигурации, выход которого подключен к входам настройки первой группы вычислительных модулей, отличающееся тем, что, с целью увеличения производительности, оно содержит счетчики, дешифратор, схему сравнения, триггер управления и мультиплексор, причем информационные входы мультиплексора соединены с инфор-, . мационными выходами вычислительных модулей, адресный вход мультиплексора подключен к второму выходу первого распределителя импульсов, а выход мультиплексора соединен с входом разрешения выборки блока управляющей памяти, выход схемы сравнения подключен к входу блокировки блока управляющей памяти, управляющему входу блока памяти реконфигурации, входам вычитания счетчиков, второму входу установки О второго распределителя импульсов и счетному входу четвертого рас-, пределитёля импульсов, второй выход которого соединен с входами установки О счетчиков и триггера управления, вход установки 1 триггера управления подключен к входу установки устройства, первый выход триггера управления соединен с управляющими входами второго и четвертого распределителей импульсов, а второй выходс управляющим входом первого распределителя импульсов и входом разрешения выдачи входного регистра, первый и третий выходы второго распределителя импульсов подключены соответственно к информационному, входу дешифр тора и управляющим входам очетчиков, третий выход первого распределителя импульсов соединен с управляющим входом дешифратора, выходы которого подключены к входам сложения счетчиков, а выходы счетчиков соединены с первым входом схемы сравнения, второй вход которой соединен с первым выходом третьего распределителя импульсов. 2. Устройство по п. 1, отличающееся тем, что вычислительный модуль содержит арифметикологический блок, блок микропрограмм мной памяти, блок управления и блок элементов И, причем первый и второй, информационные входы модуля .соединен с первым и вторым информационными вх дами арифметико-логического блока, первый управляющий вход модуля подключен к первому управляющему входу арифметико-логического блока и первому входу блока элементов И, второй управляющий вход модуля соединен с вторым входом блока элементов И, тре тий управляющий вход модуля подключе к первым входам блока управления и блока микропрограммной памяти, вход настройки модуля соединен с вторым и третьим входами блока микропрограммной памяти, первый выход арифметико логического блока подключен к адресному выходу модуля, второй выход арифметико-логического блока соединен с вторым входом блока управления третий и четвертый входы которого подключены соответственно к первому выходу блока микропрограммной памяти и выходу блоки элементов И, а вы-ход - к третьему входу блока микропрограммной памяти, второй и третий выходы блока микропрограммной памяти соединены соответственно с вторым управляющим входом арифметико-логического блока и информационным выходом модуля. 3.Устройство по п. 2, отличающееся тем, что арифметикологический блок содержит регистр, сумматор, коммутатор, два узла элементов И, узел оперативной памяти и дешифратор, причем первый и второй информационные входы блока соединены с первыми входами соответственно первого узла элементов И и коммутатора, выход регистра подключен к первому входу, второго узла элементов И и второму входу коммутатора, первый управляющий вход блока соединен с вторыми входами У.ЗЛОВ элементов И, а второй управляющий вход блока подключен к входу дешифратора, выход которого соединен с управляющими входами регистра, сумматора, коммутатора и узла оперативной памяти, выход узла опера-г тивной подключен к третьему входу коммутатора, выход которого соединен с информационным входом сумматора, выход первого узла элементов И и первый выход сумматора подключены к информационным входам регистра и узла оперативной памяти, а выход второго узла элементов И и второй выход сумматора соединены соответственно с первым и вторым выходами блока. 4.Устройство по п. 2, от л ичающееся тем, что блок управления содержит два регистра, коммутатор и дешифратор, причем первый и второй входы блока соединены с первыми входами соответственно первого и второго регистров, третий вход блока подключен к входу дешифратора и первому входу коммутатора, а четвертый вход блока соединен с вторым входом коммутатора, выход дешифратоРа подключен к управляющим входам регистров и коммутатора, третий вход которого соединен с выходом второго регистра, а выход - с вторым входом первого регистра, выход первого регистра подключен к выходу блока. Источники информации, принятые во внимание при экспертизе 1,Авторское свидетельство СССР № , кл. G Об F 15/18, 1979. 2.Авторское свидетельство СССР № 640301, кл. G Об F 15/00, 1978 (прототип).

Авторы

Даты

1982-09-07—Публикация

1980-11-03—Подача