Изобретение относится к вычислительной технике.

Известно устройство, содержащее регистр адреса, коммутаторы, модификатор адреса, узлы управления модулем памяти, блоки памяти, блок управления, буферные регистры считывания и записи сдвигатели, регистр маски, регистр данных, формирователи мае-. ки записи и маски считывания, блок управления выделением полей памяти, выполненный на элементах И, НЕ и сумматоре, В этом устройстве информационные разряды слова могут записыватьс;я в любые заданные разряды модулей памяти слева или справа oi кодированного значения границы L J«

Однако данное устройство содержит значительное оборудование и его рационально использовать в высокопроизводительных вычислительных машинах (ЭВМ),

Для упрсшления промышленными устанввками и технологическими процессами все больше применяются мини и микро ЭВМ, обеспечивая реализацию достаточно сложных алгоритмов управления. Исполнительные элементы в системах управления часто имеют релейный характер и выполняют операции,

включения, выключения и переключения различных цепей и устройств. Соответствующие сигналы управления выводятся из ЭВМ группами ( слрвами), Выводимое слово представляет собой вектор двоичных переменных, значения составляющих которого определяются в общем случае в произвольном порядке в результате вычислений, выпол10няемых в ЭВМ по определенным программам. Для формирования выводимоговектора требуется операция записи двоичной переменной в любой разряд ячейки памяти. Часто выводимый век15тор формируется по результатам реализации многоместных логических функций.

Наиболее близким к изобретению по технической, сущности является

20 устройство, содержащее блоки памяти, регистр числа, регистр команд, счетчик команд, мультиплексор адреса и блок микропрограммного управления. Для записи двоичной переменной в

25 заданный разряд ячейки памяти в нем используется программный способ с применением команд сдвига, дизъюнк ции, конъюнкции и инверсии ,

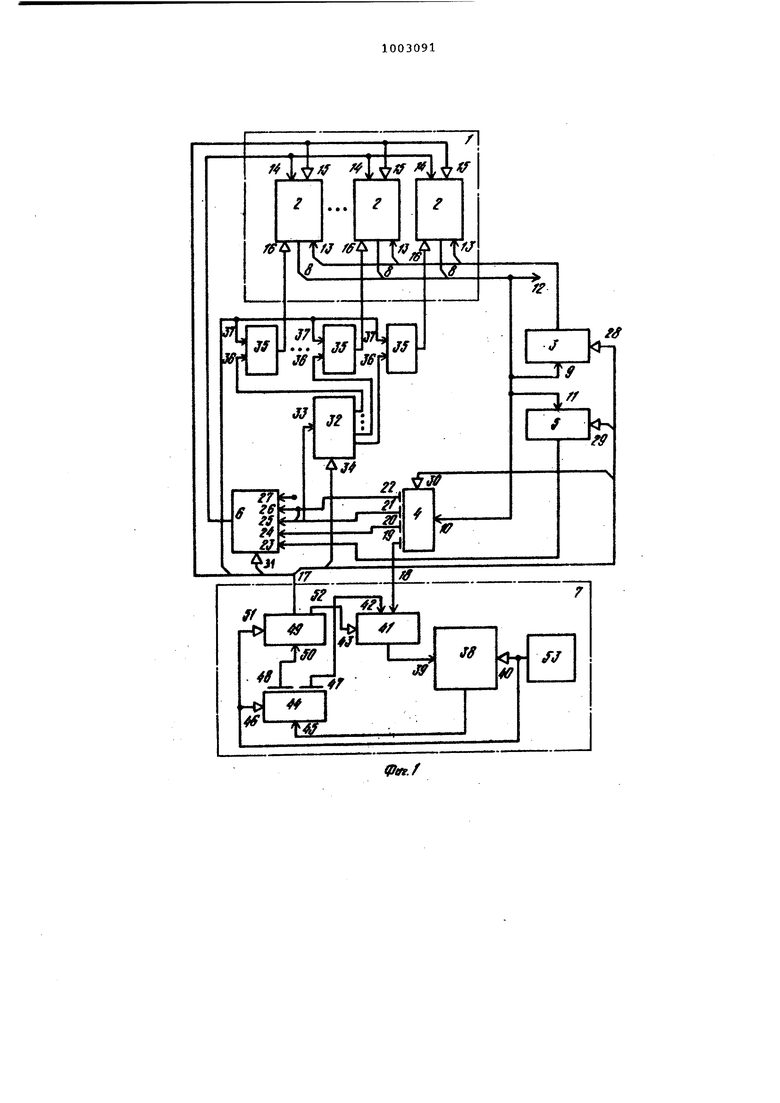

Недостатками устройства, реали30зующего известный способ, являются сравнительно большая сложность программ и низкая производительность вы полнения таких операций. Целью изобретения является повышение производительности. Поставленная цель достигается тем, что в устройство/ содержащее блоки памяти-, регистр числа,™ регистр команд, счетчик команд, мультиплексор адреса и блок микропрограммного управления, причем информационные выходы блоков памяти соединенй соответственно с информа ционными входами регистра числа, регистра команд, счетчика команд и с : выходом устройства, информационные входы блоков памяти соединены с выходом регистра числа, адресные входы соединены с выходоммультиплексора адреса, первые управляющие входы блоков памяти соединены с выходом бл .ка микропрограммного управления, вход которого соединен с первым выходом регистра команд, первый инфорВ4ационный вход мультиплексора адреса соединен с выходом счетчика команд, второй и третий информационные входы соединены соответственно с вторым и с третьим выходами регистра команд управляющие входы мультиплексора адг реса, регистра числа, регистра команд и счетчика команд соединены с выходом блока микропрограммного управления, введены дешифратор и элементы ИЛИ по числу блоков памяти, причем четвертый информационный вход .1ультиш1ексора адреса соединен с четвертым выходом регистра команд пятый информационный вход мультиплексора адреса является входом устройства, информационный вход дешифра тора соединен с третьим выходом ре гистра команд, управляющий вход - с выходом блока микропрограммного управления, выходы дешифратора соединены соответственно с первыми входами элементов ИЛИ, вторые входы которьах соединены с выходом, блока микропрограммного управления, выходы соединены соответственно с вторыми управляющими входами блоков памяти. На фиг. 1 представлена структурная схема устройства; на фиг. 2 временной диаграмма работы. Устройству содержит оперативную память 1, содержащую блоки 2 памя;;; ти, регистр 3 числа, регистр 4 команд, счетчик 5 команд,мультиплексор 6 адреса, блок 7 микропрограммно го управления, информационные выходы 8 блоков памяти, информационные входы регистра числа (9), регистра команд(.10) и счетчика команд (11), выход 12 устройства, информационные 13, адресные 14, первые 15 и вторые 16 управляющие входы блоков памяти, выход 17 и вход 18 блока 7 микропрограммного управления, выходы 19-22 регистра команд, информационные вхо,ды 23-27 мультиплексора адреса, управляющие входы 28-31 регистра числа, счетчика команд, регистра команд и мультиплексора адреса, дешифратор 32 с информационным 33 и управляющим 34 входами, элементы ИЛИ 35 с первым 36 и вторым 37 входами, узел 38памяти микропрограмм с адресным 39и управляющим 40 входами, регистр 41 адреса микрокоманд с первым 18, вторым 42 информационными и управляющим 43 входами, регистр 44 микрокоманд с информационным 45 и управляющим 46 входами, первым 47 и втог рым 48 выходами, группа 49 элементов И с информационным. 50 и управляющим 51 входами, первым 52 и вторым 17 выходами, генератор 53 тактовых импульсов.1 Блок 2 памяти является одноразрядным, он имеет т-разрядный адресный вход 14 и содержит 2 запоминающих элементов, дешифратор адреса и схемы управления. В качестве блока 2 могут использоваться, например, большие интегральные схемы. На первый управляющий вход 15 подается сигнал разрешения обращения к блоку 2 памяти, инициирующий работу внутг. ренних схем управления блока 2. Этот сигнал подается как в режиме Чтение, так и в режиме Запись. На управляющий вход 16 подается сигнал разрешения записи. Этот сигнал подается только в режиме Запись. Для записи ДВОИЧНОЙ переменной только в один .требуемый разряд ячейки блока памяти используется возможность независимого формирования сигг налов разрешения записи в каждом разряде. При выполнении команд, связанных с записью кодов в блок 1 памяти, сигнал разрешения подается одновременно на нее блоки 2 памятИ из блока 7 микропрограммного управления через входы 37 элементов ИЛИ 35. Регистры 3 числа и 4 команд работают в режиме хранения при нулевых сигналах на управляющих входах 28 и 29, а в режиме записи кодов, поступающих на их информационные входы 9 и 10, при единичных значениях. Счетчик 5 команд может работать в трех режимах в зависимости от сигнала на управляющем вхбде 29: хранение, запись кода, подаваемого на вход 11, модификация кода в счетчике прибавлением единицы. Мультиплексор б адреса имеет выход соответственно числу разрядов на адресных входах 14 блоков 2 памяч ти и четыре входных канала. Первому В, второму В и третьему В каналам соответствуют входы 23, 24 и 25, а четвер ому В группа входов 26 и 27. Мультиплексор б адреса в зависимости от кода на управляющем, входе 31 переключает на выход код соответ ствуияцего канала. Дешифратор 32 при наличии сигнал 1 на управляющем входе преобразует двоичный код в соответствующий уни«7 тарный код на выходе. Команда считывается из блока 1 памяти По адресу из счетчика 5 команд, подаваемому на адресный вход 14 блока 1 пэмяти через первый канал t вход 23) мультиплексора 6 адре са, и записывается в регистр 4 команд. Двухоперандные команды имеют сле дукиций формат, которому соответству ют группы выходов регистра 4 команд код операции 19, адрес 1-го операнда 20, адрес 2-го операнда 21 и 22. Адрес 2-го операнда используется и как адрес результата. Команда записи двоичной переменной в любой разряд ячейки блока 1 памяти имеет следующий формат; как операции 19, адрес ячейки ОЗУ 20, код номера разряда 21, код адреса ячейки выделенного сегмента блока 1 памяти, хранящей требуемую константу 22. В двух ячейках выделенного сегме та блока 1 памяти должны быть записаны две констано ; первая с нулевы ми значениями разрядов, вторая - с единичным значения ш. Первая константа используется дл записи нуля в любой разряд ячейки блока 1 памяти, а вторая константа для записи единицы. Работа устройства при выполнении команды записи двоичной переменной в любой разряд ячейки оперативного . запо1 1инающего устройства может быть представлена следующей микропрограммой. Начало; t ,j,oy2.,,; Vt 5 ) Vt Формирование адреса ячейки 1 памяти с требуемой константой с использованием 4-го канала мультиплексора 6 .адреса, считывание константы и запись ее в регистр 3 числ : РЗр1 - г ,-Ч ;НСАКП . ,,;H(A)ti ---HCA)i;il4j q,}e Формирование адреса ячейки в бло ке 1 памяти, в которую необходимо произвести запись двоичной переменной { нуля, либо единицы), запись в разряд, соответствующий коду в регистре 4 команд, кода из регистра 3 числа и содержимое остальных разрядов ячейки блока 1 памяти остается неиз{ енным. Необходимые последовательности управляющих сигналов формирует блок 7микропрограммного управления. Рассмотрим алгоритмы работы входящих 8него узлов. Узел 38 памяти микропрограмм работает в режимах хранения и чтения информации. При 1 на входе АО осуществляется чтение содержимого ячейки по адресу, код которого поступает на вход 39. Регистр 41 адреса микрокомгшд (РАМК } работает в режимах хранения и записи по одному из 2-х входов 18 и 42, При V 43 01 РАМК. X,g При V 43 10 Регистр 44 иикрокоманд работает в режимах хранения и записи. На структурном уровне предстгшления устройства его работа рассматривается в дискретном времени, за дискрет принят цикл обращения к блоку 1 памяти. В зависимости от типов больших интегральных схем, соответствующих блокам 2, этот цикл может быть различным и ему соответствует различная временная диаграмма сигна-. лов ria информационном 13, адресном 14 и управляющих 15 и 16 входах, а также на выходе 8. Для реализации требуемой временной диаграммы цикл делится на такты с помощью тактовых импульсов, вырабатываемых генератором тактовых импульсов 53. Упровляю щие сигналы синхронизируются соответствукяцими тактсмлми и: пульсами в элементах И группы 49. Возможная временная диаграмма работы устройства содержит три цикла: цикл считывания команды и два цикла ее выполнения. В формате микрокоманды имеются два поля для адреса следующей микрокоманды и для кода управляющих сигналов. На.фиг. 1 им соответствуют выходы 47 и 48 регистра 44 микрокоманд. Код управляющих сигналов на выходе 48 имеет несколько полей для различных управляющих сигналов. Блок 7 микропрограммного управления при считывании и выполнении команды, в соответствии с выбранной временной диаграммой, работает следую,щим образом. В 1-ом такте на управляющий вход 40 узла 38 хранения микропрограмм поступает сигнгш 1 и производится считывание микрокоманды по адресу, ;поступающему из регистра 41 адреса

Микрокоманд. В начале 2-го такта считанный код записывается в регистр 44 микрокоманд. На выход 31 при этом поступает сигнал 00, в результате чего мультиплексором 6 формируется адрес, поступающий из счетчика 5 команд. В 3-ем такте формируется сигнал 1, на вхрде 15 обеспечивающий считывание команды из-блока 1 памяти в 4-ом такте считанная команда записывается в регистр 4 команд, содержимое счетчика 5 команд увеличивается на единицу, а в регистр 41 адреса микрокоманд записывается код операции считанной команды, поступающий с выхода 19, В 1-ом такте 2-го цикла считывается первая микрокоманда приведенной выше микропрограммы и в начале 2-го такта записывается в регистр 44 микрокоманд. Формируется сигнал 11 на входе 31. В 3-ем такте осуществляется считывание константы из блока 1 памяти, в четвертом такте она записывается в регистр 3 числа, а врегистр 41 адреса микрокоманд записывается адрес следующей микрокоманды, поданный на вход 42. в 1-ом такте 3-го цикла считывается 2-я микрокоманда из узла 38 памяти микропрограмм и в начале 2-го такта записывается в регистр 44 микрокоманд. Формируется сигнал 01 на входе 31, при этом мультиплексор 6 подключает к выходу 2-ой канал tвход 247.

Ъ 3-ем такте формируется сигнал разрешения обращения к блок.у 1 памяти. В 4-ом такте формируется управляющий сигнал 1 на входе 34 дешифратора 32 и на выходе дешифратора 32 формируется выходной сигнал.

Соответственно на входе 16 одного из блоков памяти формируется сигнал разрешения записи и осуществляется запись в ячейку, адрес которой поступает с выхода 20. Записывается О, если во 2-ом цикле была считана первая константа, или 1, если была вторая константа.

В остальных блоках 2 памяти сигнал на входах 16 равен О и запись не производится. В 4-ом такте осуществляется также запись адреса следующей мико окоманды по входу 42 в регистр 41 адреса микрокоманд. Это должен быть адрес микрокоманды считывания очередной команды из блока 1 памяти. Выполнение такой микрокоманды было рассмотрено в 1-ом цикле работы устройства.

Возможны и Очругие подходы к организации блока 7 микропрограммного

управления, например, в виде автомата с жесткой логической на интегральных схемах либо на программируеи«х логических матрицах.

Формула изобретения

стройство для управления операцией записи, содержащее блоки памяти, регистр числа, регистр команд, счетчик команд, мультиплексор адреса и блок микропрограммного управления, причем информационные выходы блоков памяти, соединены соответственно с информационными входами регистра числа, регистра команд, счетчика команд и с выходом устройства, информационные входы блоков памяти соединены с выходом регистра числа, адресные входы соединены.с выходом мультиплексора адреса, первые управляющи входы блоков памяти соединены с выходом блока микропрограммного управления, вход которого соединен с первым выходом регистра команд, первый информационный вход мультиплексора адреса соединен с выходом счетчика команд, второй и третий информационные входы соединены соответственно с вторым и с третьим выходами регистра команд, управляющие входы мультиплексора адреса, регистра числа, регистра команд и счетчика команд соединены с выходом блока микропрсэграммного управления, отличающееся тем, что, с целью повышения производительности, в него введены дешифратор и элементы ИЛИ по числу блоков памяти, причем четвертый информационный вход мультиплексора адреса соединен с четвертым выходом регистра команд, пятый информационный вход мультиплексора адреса является входом устройства, информационный вход дешифратора соединен с третьим выходом регистра команд, управляющий вход - с выходом блока микропрограммного управления, выходы дешифратора соединены соответственно с первыми входами элементов ИЛИ, вторые входы которых соединены с выходом блока микропрограммного управления, выходы соединены соответственно с вторыми управляющими входами блоков памяти.

Источники информации, принятые во внимание при экспертизе

1.Патент США №3 781812, чл. G06P 7/00, 1973.

2.Таненбаум Э. Многоуровневая организация ЭВМ. Мир, 1979, 7, с. 256-265 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

| Устройство для выполнения команд реализации систем многоместных логических функций | 1981 |

|

SU999051A1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| Микропрограммный процессор | 1987 |

|

SU1517034A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108448A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

Авторы

Даты

1983-03-07—Публикация

1981-10-20—Подача