соседних по строке блоков коммутации, соответствующ,ие входы крайних по строке бло,ков каммутадии Соедияены с выходом блока ввода. Кроме того, блок суммирования содержит одноразрядный сумматор, элементы И, группы элементов И, регистры, элемент ИЛИ, причем первый, второй, третий, четвертый и пятый входы блока суммирования подключены к первому, второму, третьему, четвертому и пятому входам сумматора, выход которого подключен к первым входам первого и второго элементов И, выходы которых соединены с информационными входами первого и второго регистров,,первые выходы кото;рых подключены к первым входам элементов И первой и второй групп, вторые входы которых соединены соответственно с выходами третьего и четвертого элементов И, вторые выходы первого и второго регистров соединены с первыми входами пятого и шестого элементов И, выходы которых подключены к входам элемента ИЛИ, выход которого соединен с,выходом блока суммирования, выходы элементов И первой н второй групп подключены к группе выходов блока суммирования, вторые входы первого, второго, пятого и шестого элементов И соединены с третьей группой управляюихих входов блока суммирования, первый и второй входы третьего элемента И подключены к первой группе управляюш,их входов блока суммирования, первый и второй входы четвертого элемента И соединены с второй группой управляющих входов блока суммирования.

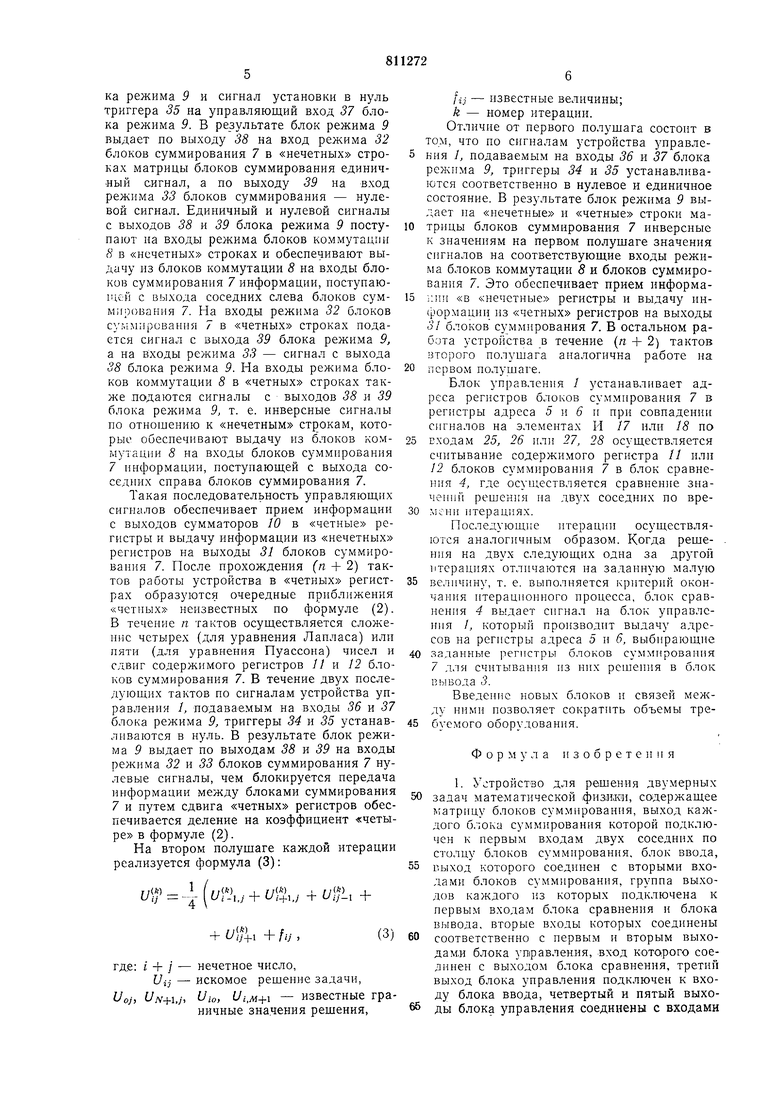

На фиг. 1 дано предлагаемое устройство; на фиг. 2 и 3 - структуры блоков суммирования и задания режима.

Устройство содержит блок управления /, блок ввода 2, блок вывода 3, блок сравнения 4, первый регистр адреса 5, второй регистр адреса 6, матрица блока cyммиpJЭвания 7, блоки коммутации 8, блок режима 9.

Каждый блок суммирования содержит пятивходовой одноразрядный сумматор 10, первый регистр 11, второй регистр 1Z, первый элемент И 13, второй элемент И 14, шестой элемент И 15, четвертый элемент И 16, пятый элемент И 17, шестой элемент И 18, первую группу элементов И 19, вторую группу элементов И 20, элемент ИЛИ 21, первую выходную шину 22, вторую выходную шину 23, входы пятивходового одно(разрядного сумматора 24, управляющие входы блока суммирования 25-30, выход блока суммирования 31, первый вход режима 32, второй вход режима 33.

Блок режима 9 содержит первый триггер 34, второй триггер 35, входы блока режима - 55 и 37, выходы блока режима - 38 и 39.

Устройство предназначено для решения системы уравнений вида

i-.i + t(+l./ + Uij-i + /7+1 -

-4i;,; + /,7 o,

где i 1, 2, ... M / 1, 2, ... M. Устройство работает следующим образом.

Каждый блок суммирования 7 соответствует двум соседним неизвестным по строке (Uij, Uij+i) или по столбцу (Uij, f/i+l- ).

В одном из регистров //, 12 блока суммирования 7 хранится очередное приближение неизвестного с четной суммой индексов («четное неизвестное, «четный регистр), в другом - очередное приближение неизвестнего с нечетной суммой индексов («нечетное .неизвестное, «нечетный регистр).

Если блок суммирования 7 хранит два соседних неизвестных по строке, то его выходы соединяются с входами соседних слева и справа блоков коммутации 5 и входами соседних сверху и снизу по столбцу блоков суммирования 7. Если блок суммирования 7 хранит два соседних неизвестных по столбцу, то выходы соединяются с вхолами соседних сверху и снизу по столбцу блоков коммутации 5 и входами соседних слева и справа по строке блоков суммирования.

Пусть в строках матрицы блоков суммирования 7 с нечетными номерами «нечетные строки) в первых регистрах // блоков суммирования 7 хранятся «четные неизвестные («четные регистры), во вторых регистрах 12 - «нечетные неизвестные («нечетные регистры); в строках -матрицы блоков суммиро.вания 7 с четнымл номерами - наоборот («четные cTipoKH): первые регистры 11 блоков сумМИроваН|Ия 7 являются «нечетными, а вторые регистры 12

блоков суммирования - «четными.

На первом полушаге каждой итерации реализуется формула (2), т. е. вычисляются новые приближения «четный неизвестных:

1

/.() I 7/(й-1) г //(Я-1) ,

/(-)

(Ui-ij -rUi+ij +Uij-i j(2)

(ft-l)

/л

f //;),

и I

7+1

i + j - четное число.

Блок ввода 2 выдает в последовательном коде, начиная с младшего разряда, значения граничных условий для «четных

неизвестных на входы внешних блоков суммирования 7 в крайних и нечетных строках блоков коммутации 8, и значения соответствующих правых частей fa на входы всех блоков суммирования 7, на другие входы

которых поступает последовательный код со своего выхода, выхода сответствующего блока коммутации S и с соседних блоков суммирования 7. Одновременно блок управления / выдает сигнал установки в единицу

триггера 34 на управляющий вход 36 блока режима 9 и сигнал установки в нуль триггера 35 на управляющий вход 37 блока режима 9. В результате блок режима 9 выдает по выходу 38 на вход режима 32 блоков суммирования 7 в «нечетных строках матрицы блоков суммирования единичный Сигнал, а по выходу 39 на вход режима 33 блоков суммирования - нулевой сигнал. Единичный и нулевой сигналы с выходов 38 и 39 блока режима 9 поступают на входы режима блоков коммутации 8 в «нечетных строках и обеспечивают выдачу из блоков коммутации 8 на входы блоков суммирования 7 информации, поступающей с выхода соседних слева блоков суммирования 7. На входы режима 32 блоков суммирования 7 в «четных строках подается сигнал с выхода 39 блока режима 9, а на входы режима 33 - сигнал с выхода 38 блока режима 9. На входы режима блоков коммутации 8 в «четных строках также подаются сигналы с выходов 38 и 39 блока режима 9, т. е. инверсные сигналы по отношению к «нечетным строкам, которые обеспечивают выдачу из блоков коммутации 8 на входы блоков суммирования 7информации, поступающей с выхода соседних справа блоков суммирования 7. Такая последовательность управляющих сигналов обеспечивает прием информации с выходов сумматоров 10 в «четные регистры и выдачу информации из «нечетных регистров на выходы 31 блоков суммирования 7. После прохождения (п + 2) тактов работы устройства в «четных регистрах образуются очередные приближения «четных неизвестных по формуле (2). 8течение п тактов осуществляется сложение четырех (для уравнения Лапласа) или пяти (для уравнения Пуассона) чисел и сдвиг содержимого регистров 11 и 12 блоков суммирования 7. В течение двух последующих тактов по сигналам устройства управления 1, пода.ваемььм на входы 36 и 37 блока режима 9, триггеры 34 и 35 устанавливаются в нуль. В результате блок режима 9 выдает по выходам 58 и 39 на входы режима 32 и 33 блоков суммирования 7 нулевые сигналы, чем блокируется передача информации между блоками суммирования 7 и путем сдвига «четных регистров обеспечивается деление на коэффициент «четыре в формуле (2). На втором полушаге каждой итерации реализуется формула (3): ;lf -1(г;,+ (/;,,;-bi;l,+ -f , + fij , где: / + / - нечетное число, Uij - искомое решение задачи, Voj, UN+I,/, Uio, Ui,M+ - известные граничные значения решения. fij - известные величины; k - номер итерации. Отличие от первого полушага состоит в ом, что по сигналам устройства управлеия /, подаваемым на входы 36 и 37 блока 9, триггеры 34 и 35 устанавливаются соответственно в нулевое и единичное состояние. В результате блок режима 9 выает на «нечетные и «четные строки матрицы блоков суммирования 7 инверсные к значениям на первом полушаге значения сигналов на соответствующие входы режима блоков коммутации 8 и блоков суммирования 7. Это обеспечивает прием информацпи «в «нечетные регистры и выдачу информации из «четных регистров на выходы 31 блоков суммирования 7. В остальном работа устройства в течение (п + 2) тактов второго полушага аналогична работе на первом полушаге. Блок управления 1 устанавливает адреса регистров блоков суммирования 7 в регистры адреса 5 и 5 и при совпадении сигналов на элементах И 17 или /8 по входам 25, 26 или 27, 28 осуществляется считывание содержимого регистра 11 или 12 блоков суммирования 7 в блок сравнения 4, где осуществляется сравнение значений решения иа двух соседних по вреМ8НИ итерациях. Последующие итерации осуществляются аналогичным образом. Когда рещения на двух следующих одна за другой итерациях отличаются на заданную малую величину, т. е. выполияется критерий окончания итерационного процесса, блок сравнения 4 выдает сигнал на блок управления /, который производит выдачу адресов на регистры адреса 5 и 6, выбирающие заданные регистры блоков суммирования 7 для считывания из них решения в блок вывода 3. Введеиие новых блоков и связей иими позволяет сократить объемы требуемого оборудования. Формула изобретения 1. Устройство для решения двумерных задач математической физ1И;ки, содержащее матр1щу блоков суммирования, выход каждого блока суммирования которой подключен к первым входам двух соседних по столцу блоков суммирования, блок ввода, выход которого соединен с вторыми входами блоков суммирования, группа выходов каждого из которых подключена к первым входам блока сравнения и блока вывода, вторые входы которых соединены соответственно с первым и вторым выходами блока увравления, .вход которого соединен с выходом блока сравнения, третий выход блока управления подключен к входу блока ввода, четвертый и пятый выходы блока управления соединены с входами

первого II второго регистров адреса, выходы первого регистра адреса подключены к -первой грулпе управляющих входов каждого блока суммировалия, выходы второго регистра адреса соединены с второй группой управляющих входов каждого блока суммирования, отличающееся тем, что, с целью упрощения устройства оно содержит блок задания режима и блоки коммутации, причем щестой выход блока управления подключен к входу блока задания режима, выход которого соединен с третьей группой управляющих входов каждого блока суммирования и управляющими входами всех коммутаторов, выходы коммутаторов соединены с третьими входами соответствующих блоков суммирования, выход каждого блока суммирования кодключен к четвертому входу этого блока суммирования и к входам соседних по строке блоков коммутации, входы крайних по строке блоков коммутации соединены с выходом блока ввода.

2. Устройство по п. 1, о т л и ч а ю щ е ес я тем, что блок суммирования содержит одноразрядный сумматор, элементы И, группы элементов И, регистры, элемент ИЛИ, причем первый, второй, третий, четвертый и пятый входы блока суммирования подключены к первому, второму, третьему, четвертому и пятому входам одноразрядного сумматора, выход которого подключен к первым входам первого и второго элементов И, выходы которых соединены с информационными входами первого и второго регистров, первые выходы которых подключены к первым входам элементов И первой и второй групп, вторые входы которых соединены соответственно с выходами третьего и четвертого элементов И, вторые выходы первого и второго регистров соединены с первыми входами

пятого и щестого элементов И, выходы которых подключены ко входам элемента ИЛИ, выход которого соединен с выходом блока суммирования, выходы элементов И первой и второй групп подключены к группе выходов блока суммирования, вторые входы первого, второго, пятого и щестого элементов И соединены с третьей группой управляющих входов блока суммирования, первый и второй входы третьего элемента

И подключены к первой группе управляющих входов блока суммирования, первый и второй входы четвертого элемента И соединены с второй группой управляющих входов блока суммирования.

Источники информации, принятые во внимание при экспертизе:

1.Евренков Э. В. Однородные вычислительные системы высокой производительности.-Новосибирск, «Наука, 1966, с. 38-47

2.Авторское свидетельство СССР jYo 603997,- кл. G 06 F 15/32, 25.04.78.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительный блок матричного устройства для решения дифференциальных уравнений в частных производных | 1989 |

|

SU1605253A1 |

| Устройство для решения двумерных задач математической физики | 1975 |

|

SU610116A1 |

| Устройство для решения двумерных задач математической физики | 1991 |

|

SU1833891A1 |

| Устройство для реализации двухмерного быстрого преобразования Фурье | 1982 |

|

SU1164730A1 |

| Вычислительный узел цифровой сеточной модели для решения дифференциальных уравнений в частных производных | 1980 |

|

SU894717A1 |

| Цифровой преобразователь координат | 1974 |

|

SU614439A1 |

| Вычислительный узел цифровойСЕТОчНОй МОдЕли для РЕшЕНия диффЕРЕН-циАльНыХ уРАВНЕНий B чАСТНыХ пРОизВОд-НыХ | 1978 |

|

SU798858A1 |

| Вычислительный узел цифровой сетки для решения дифференциальных уравнений в частных производных | 1980 |

|

SU926667A1 |

| Устройство для вычисления спектра Фурье | 1983 |

|

SU1121678A1 |

| Вычислительный узел цифровой сетки | 1983 |

|

SU1132295A2 |

Авторы

Даты

1981-03-07—Публикация

1978-07-31—Подача