Изобретение относится к вычисли- тельной технике, в частности к устройствам автоматизированного преобразования и обработки однократно и редко повторяющихся процессов малой длительности.

Цель изобретения -повышение точности и упрощение преобразователя.

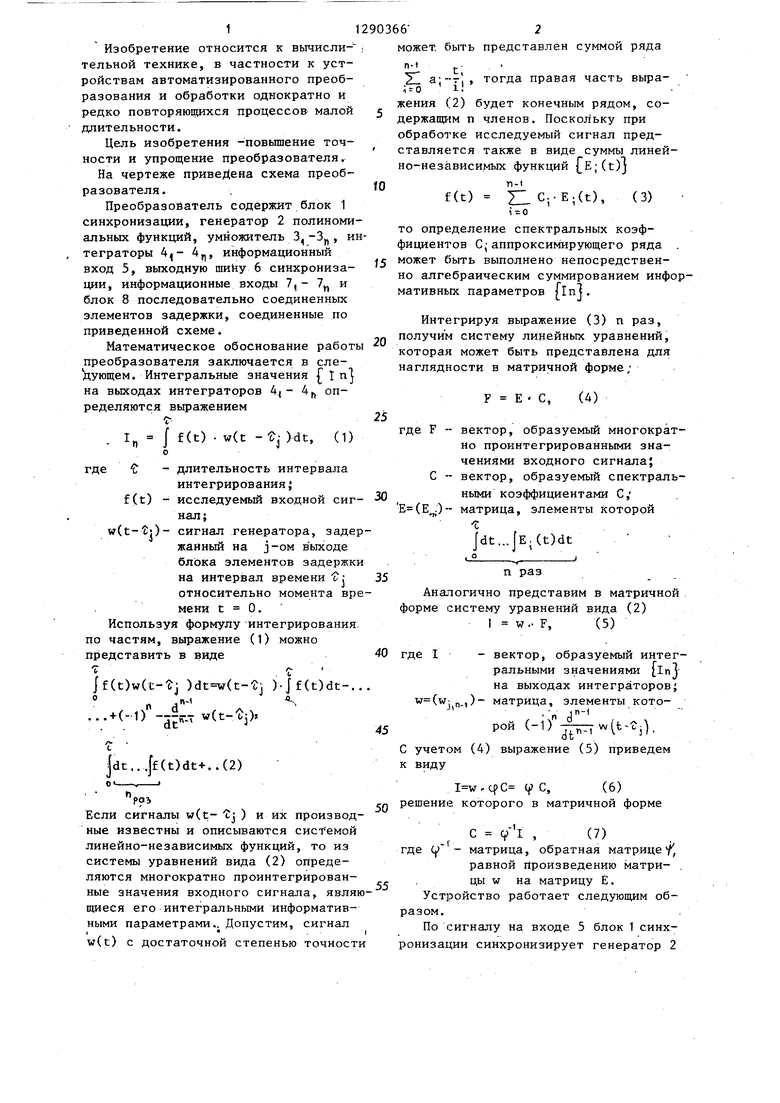

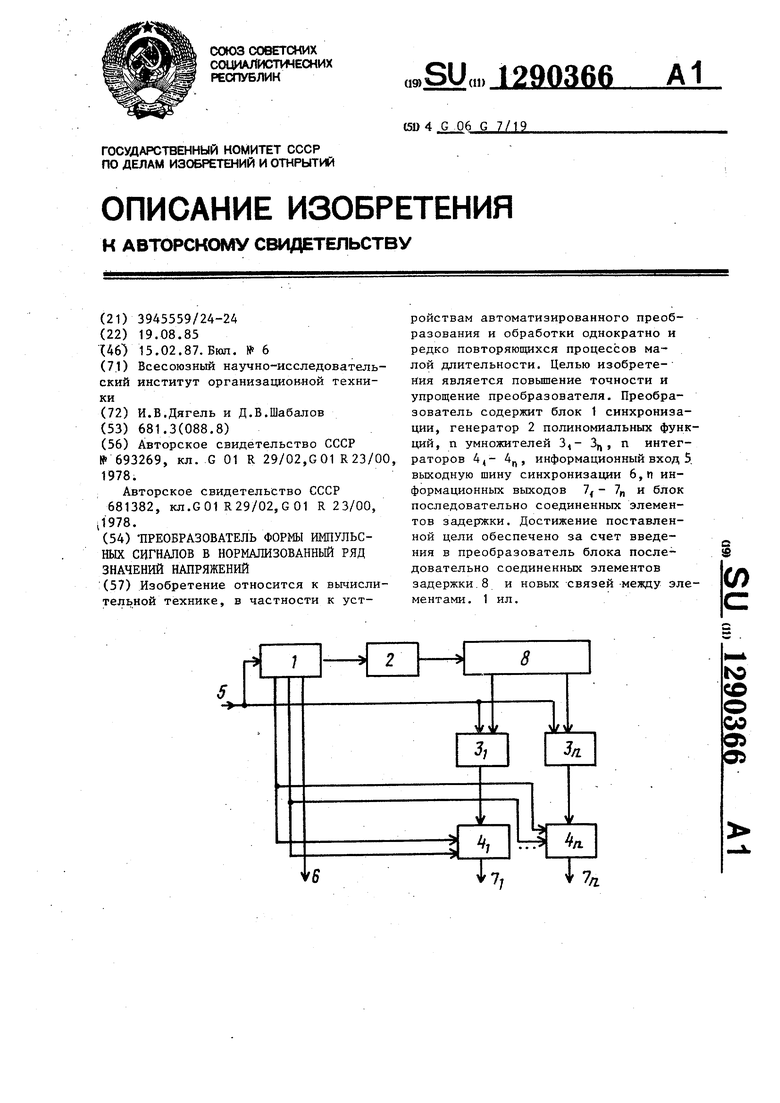

На чертеже приведена схема преобразователя.

Преобразователь содержит блок 1 синхронизации, генератор 2 полиномиальных функций, умножитель 3,, -3,, интеграторы 4„, информационный вход 5, выходную шийу 6 синхронизации, информационные входы 7,- 7 и блок 8 последовательно соединенных элементов задержки, соединенные по приведенной схеме.

Математическое обоснование работы преобразователя заключается в следующем. Интегральные значения {in на выходах интеграторов 4(- 4, определяются вьфажением Т.1 1 f(t) . w(t --fj )dt, (1)

о где - длительность интервала

интегрирования{

f(t) - исследуемый входной сигнал ;

w(t-tj)- сигнал генератора, задержанный на J-OM в ыходе блока элементов задержки на интервал времени относительно момента времени t О,

Используя формулу интегрирования, по частям, выражение (1) можно представить в виде

|f(t)w(t- fj )( )(t)dt-..

, n-i

S

...+(-1) ™n.- W(t-1)j

t

jdt,..ff(t)dt + ..(2)

POi

Если сигналы w(t- tj ) и их производные известны и описываются системой линейно-независимых функций, то из системы уравнений вида (2) определяются многократно проинтегрированные значения входного сигнала, являющиеся его интегральными информативными параметрами.. Допустим, сигнал 1 . I

w(t) с достаточной степенью точности

может быть представлен суммой ряда

П-1 J..

SI а;-т , , тогда правая часть выраi - о -

жения (2) будет конечным рядом, содержащим п членов. Поскольку при обработке исследуемый сигнал представляется также в виде суммы линейно-независимых функций (t)j n-i

f(t)

C.-E;(t), (3)

то определение спектральных коэффициентов С; aппpoкcи шpy oщeгo ряда . может быть выполнено непосредственно алгебраическим суммированием информативных параметров {inj.

Интегрируя вьфажение (3) п раз, получи м систему линейных уравнений, которая может быть представлена для наглядности в матричной форме;

F Е С,

(4)

где F - вектор, образуемый многократно проинтегрированными значениями входного сигнала; С - вектор, образуемый спектральными коэффициентами С; Е(Е.)- матрица, элементы которой Jdt...|E.(t)dt

п раз

Аналогично представим в матричной форме систему уравнений вида (2) 1 W.. F, (5)

где I - вектор, образуемый интегральными значениями flnl на выходах интеграторов; w(w„,)- матрица, элементы кото

рой (-i)w(t-).

с учетом (4) выражение (5) приведем к виду

. (f С, (6) решение которого в матричной форме

, С 9 l , (7) где 9- матрица, обратная матрице / , равной Произведению матри- . цы W на матрицу Е. Устройство работает следующим образом.

По сигналу на входе 5 блок 1 синхронизации синхронизирует генератор 2

сигнал сброса интеграто- ц и подает на них сигнал

полиномиальных функций, одновремен но снимает ров 4

разрешения интегрирования. Сигнал с выхода генератора 2 полиномиальных функций поступает с разными задержкми после блока 8 элементов задержки на аналоговые умножители 3( - 3„, в

которых умножается на входной сигнал. Интегрирование сигналов на выхо- О дах умножителей 3 производится соответствующими интеграторами 4 за время сигнала разрешения интегрирования. По окончании времени блок 1 синхронизации снимает сигнал 5 разрешения интегрирования и устанавливает сигнал на выходной шине 6 синхронизации, по которому разрешается считывание информативных интегр ьчений напряжений, содержащий блок синхронизации, генератор полиномиал ных функций, п умножителей и п интеграторов, выходы которых- являют 5 ся соответствующими информационными выходами преобразователя, а информационные входы подключены к выходам соответствующих умножителей, подсоединенных первыми входами к ин формационному входу преобразователя и к входу запуска блока синхронизации, первый второй и третий выходы которого подключены соответственно к входу синхронизации генератора полиномиальных функций, к входам разрешения интегрирования интеграто ров и к входам их сброса четвертый выход блока синхронизации соединен с выходной шиной синхронизации преных параметров формы входного сигна- 20 образователя, отличающййла с информационных выходов 7{ - „ . По окончании времени считывания блок 1 синхронизации снимает сигнал с выходной шины 6 синхронизации и устанав- сигнал сброса интеграторов 4,- 4,,.

Формула изобретения ; Преобразователь формы импульсных сигналов в нормализованный ряд знаор Э.Слиган 7905/49

Составитель А.Маслов Техред Й.Ходанич

Коррек Подпис

Тираж 673

ВНРШПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва,. Ж-35, Раушская наб., д. 4/5

.Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

О 5903664

чений напряжений, содержащий блок синхронизации, генератор полиномиальных функций, п умножителей и п интеграторов, выходы которых- являют- 5 ся соответствующими информационными выходами преобразователя, а информационные входы подключены к выходам соответствующих умножителей, подсоединенных первыми входами к информационному входу преобразователя и к входу запуска блока синхронизации, первый второй и третий выходы которого подключены соответственно к входу синхронизации генератора полиномиальных функций, к входам разрешения интегрирования интеграторов и к входам их сброса четвертый выход блока синхронизации соединен с выходной шиной синхронизации пре5

с я тем, что, с целью повьшения точности и упрощения преобразователя, он содержит блок последовательно соединенных элементов задержки, вход которого подключен к выходу генератора полиномиальных функций, а п промежуточных выходов соединены с вторыми входами соответствующих умножителей.

Корректор С.Черни Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Последовательно-параллельный многоканальный интегрирующий преобразователь | 1988 |

|

SU1566376A1 |

| Преобразователь формы импульсных сигналов в нормализованный ряд значений напряжений | 1986 |

|

SU1332339A1 |

| Сравнивающее устройство | 1986 |

|

SU1370756A1 |

| Цифровой интегратор | 1988 |

|

SU1580359A1 |

| Анализатор формы импульсных сигналов | 1980 |

|

SU900208A1 |

| Устройство для анализа формы моноимпульсных сигналов | 1983 |

|

SU1091185A1 |

| Аналоговый интегратор | 1987 |

|

SU1425724A1 |

| Устройство для приема сигналов, закодированных с избыточностью | 1988 |

|

SU1605275A2 |

| Интегрирующий аналого-цифровой преобразователь | 1987 |

|

SU1483639A1 |

| Способ пространственного приема телеграфных сигналов | 1987 |

|

SU1585903A1 |

Изобретение относится к вычислительной технике, в частности к устройствам автоматизированного преобразования и обработки однократно и редко повторяюпщхся процессов малой длительности. Целью изобретения является повышение точности и упрощение преобразователя. Преобразователь содержит блок 1 синхронизации, генератор 2 полиномиальных функций, п умножителей 3,- 3, п интеграторов 4, информационный вход 5, выходную шину синхронизации 6,п информационных выходов 7 - 7п и блок последовательно соединенных элементов задергжки. Достижение поставленной цели обеспечено за счет введения в преобразователь блока последовательно соединенных элементов задержки.8 и новых связей -между элементами. 1 ил. (Л с to ;о о со о а:

| Устройство для измерения параметров одиночных и редко повторяющихся импульсов малой длительности | 1977 |

|

SU693269A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для измерения параметров одиночных и редко повторяющихся импульсов малой длительности | 1977 |

|

SU681382A1 |

Авторы

Даты

1987-02-15—Публикация

1985-08-19—Подача