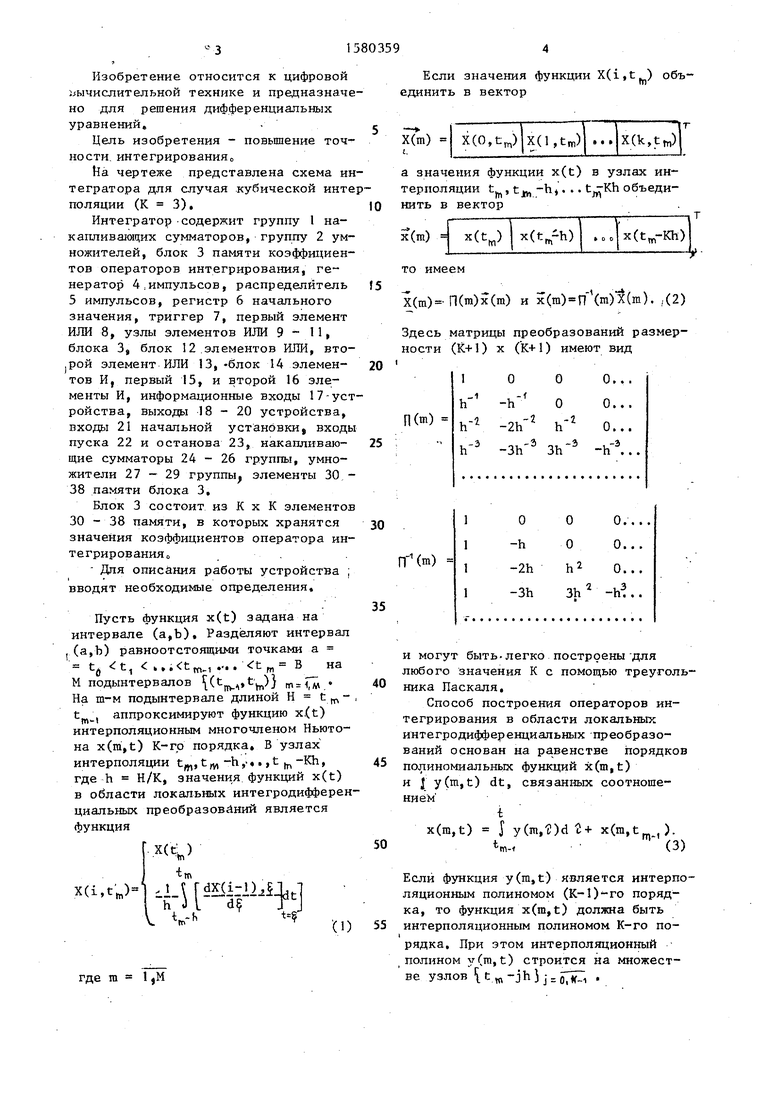

Пусть функция x(t) задана на интервале (а,Ь), Разделяют интервал ,(а,Ъ) равноотстоящими точками а tu t, k.tm, .... tm В на М подынтервалов (t.t)} тв . На m-м подынтервале длиной Н t

аппроксимируют функцию x(t)

интерполяционным многочленом Ньютона x(m,t) К-гр порядка. В узлах интерполяции tm, t m -h,- ., t m -Kh, где h H/K, значения функций x(t) в области локальных интегродифферен циальных преобразований является функция

,

tm

50

-1 «ЩгАЫД,,. ц Г

-ь

(1) 55

где m 1 ,М

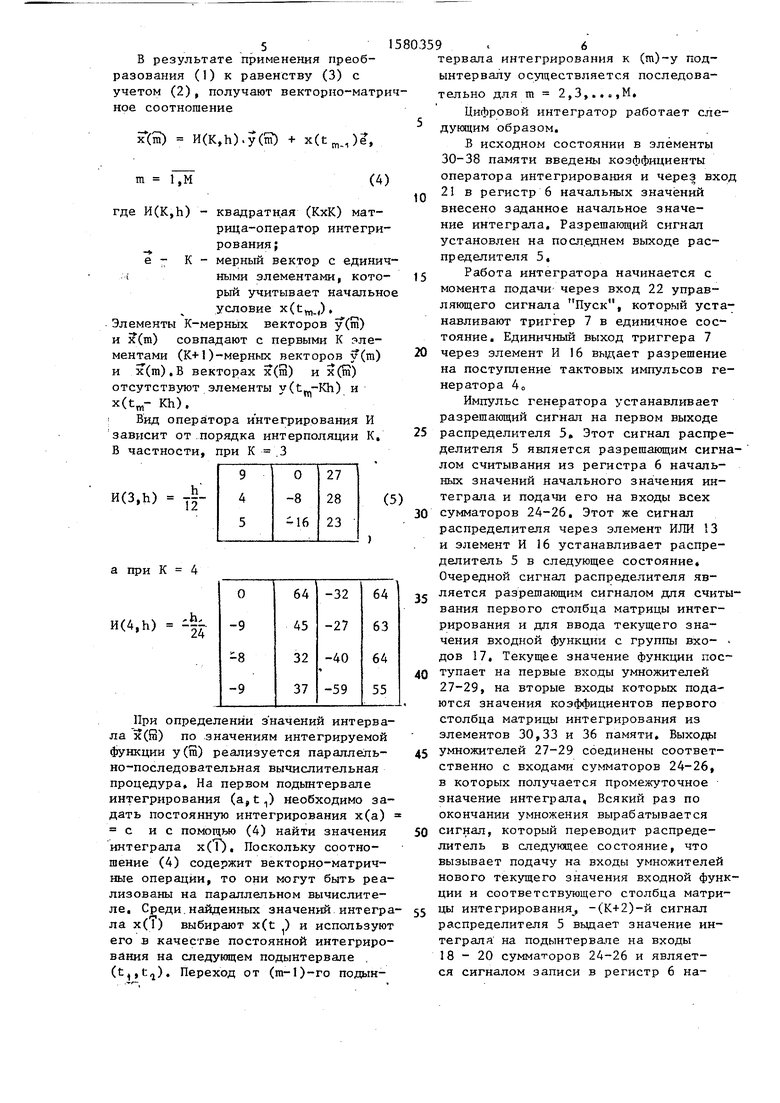

и могут быть-легко построены для любого значения К с помощью треугольника Паскаля.

Способ построения операторов интегрирования в области локальных интегродифференциальных преобразований основан на равенстве порядков полиномиальных функций x(m,t) и I у(m,t) dt, связанных соотношением

i

x(m,t) 1 y(m,1)d2+ x(m,t ). m-,Щ (З)

Если функция y(m,t) является интерполяционным полиномом (K-l)-ro порядка, то функция x(m,t) должна быть интерполяционным полиномом К-го порядка. При этом интерполяционный , полином y(m,t) строится на множестве узлов tw-jhjj .

51580.359

В результате применения преобразования (1) к равенству (3) с учетом (2), получают векторно-матрич- ное соотношение

где И(К,Ь) - квадратная (КхК) матрица-оператор интегрирования ;

е - К - мерный вектор с единич i ными элементами, который учитывает начально условие x(tw.().

Элементы К-мерных векторов у(т) и х(т) совпадают с первыми К элементами (К+1)-мерных векторов у(т) и х(т),В векторах х(й) и х(т) отсутствуют элементы y() и x(tm- Kh).

Вид оператора интегрирования И зависит от порядка интерполяции К. В частности, при К 3

И(3,Ь) у2а при К 4

И(4,Ь) -|Ј

При определении значений интервала x(ffl) по значениям интегрируемой функции у(га) реализуется параллельно-последовательная вычислительная процедура. На первом подынтервале интегрирования (a,t.,) необходимо задать постоянную интегрирования х(а) с и с помощью (4) найти значения интеграла х(Т). Поскольку соотношение (4) содержит векторно-матрич- ные операции, то они могут быть реаИмпульс генератора устанавливает разрешающий сигнал на первом выходе распределителя 5 Этот сигнал распре делителя 5 является разрешающим сигн лом считывания из регистра 6 начальных значений начального значения интеграла и подачи его на входы всех сумматоров 24-26. Этот же сигнал распределителя через элемент ИЛИ 13 и элемент И 16 устанавливает распределитель 5 в следующее состояние. Очередной сигнал распределителя является разрешающим сигналом для счит вания первого столбца матрицы интегрирования и для ввода текущего значения входной функции с группы вхо- дов 17, Текущее значение функции пос тупает на первые входы умножителей 27-29, на вторые входы которых подаются значения коэффициентов первого столбца матрицы интегрирования из элементов 30,33 и 36 памяти. Выходы умножителей 27-29 соединены соответственно с входами сумматоров 24-26, в которых получается промежуточное значение интеграла, Всякий раз по окончании умножения вырабатывается сигнал, который переводит распределитель в следующее состояние, что вызывает подачу на входы умножителей нового текущего значения входной фун ции и соответствующего столбца матри

лизованы на параллельном вычислителе. Среди найденных значений интегра-55 цы интегрирования, -(К+2)-й сигнал ла х(1) выбирают x(t ) и используютраспределителя 5 выдает значение ин- его э качестве постоянной интегриро-теграла на подынтервале на входы вания на следующем подынтервале18-20 сумматоров 24-26 и являет- (). Переход от (m-l)-ro подын- ся сигналом записи в регистр 6 нач-

-е

5)

10

15

20

25

30

35

40

45

50

тервала интегрирования к (т)-у подынтервалу осуществляется последовательно для m 2,3,...,М.

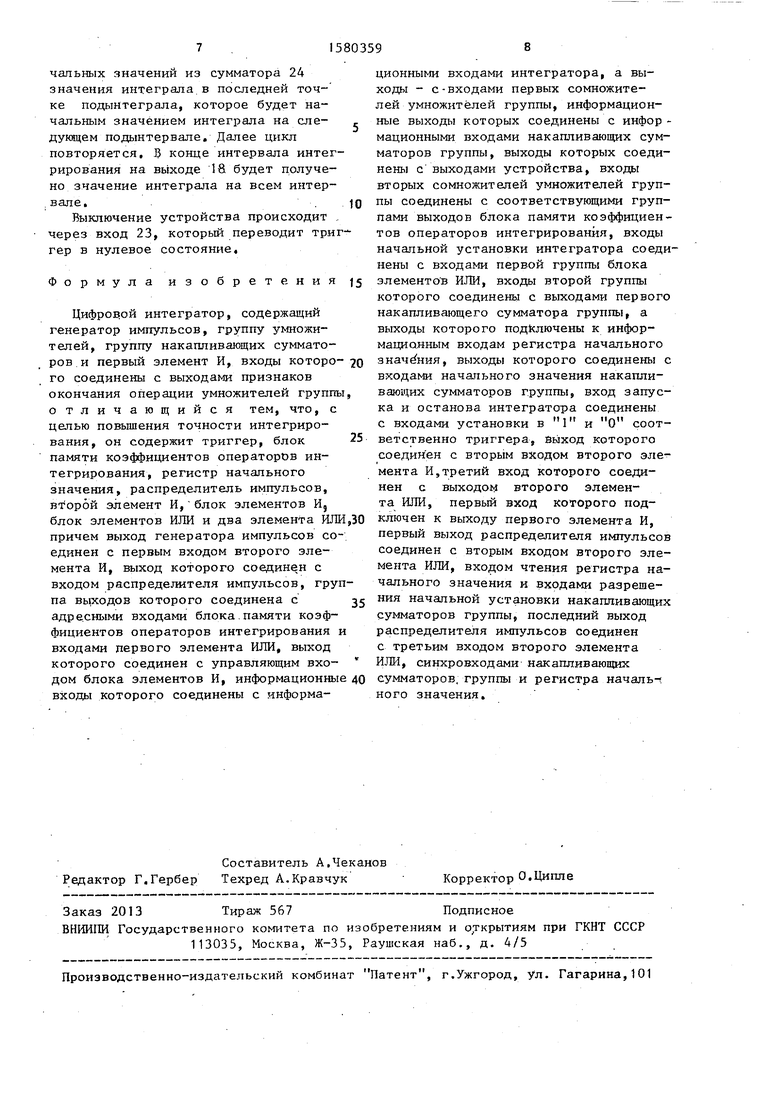

Цифровой интегратор работает следующим образом.

В исходном состоянии в элементы 30-38 памяти введены коэффициенты оператора интегрирования и через вход 21 в регистр 6 начальных значений внесено заданное начальное значение интеграла. Разрешающий сигнал установлен на последнем выходе распределителя 5,

Работа интегратора начинается с момента подачи через вход 22 управляющего сигнала Пуск, который устанавливают триггер 7 в единичное состояние. Единичный выход триггера 7 через элемент И 16 выдает разрешение на поступление тактовых импульсов генератора 4 о

Импульс генератора устанавливает разрешающий сигнал на первом выходе распределителя 5 Этот сигнал распределителя 5 является разрешающим сигналом считывания из регистра 6 начальных значений начального значения интеграла и подачи его на входы всех сумматоров 24-26. Этот же сигнал распределителя через элемент ИЛИ 13 и элемент И 16 устанавливает распределитель 5 в следующее состояние. Очередной сигнал распределителя является разрешающим сигналом для считывания первого столбца матрицы интегрирования и для ввода текущего значения входной функции с группы вхо- дов 17, Текущее значение функции поступает на первые входы умножителей 27-29, на вторые входы которых подаются значения коэффициентов первого столбца матрицы интегрирования из элементов 30,33 и 36 памяти. Выходы умножителей 27-29 соединены соответственно с входами сумматоров 24-26, в которых получается промежуточное значение интеграла, Всякий раз по окончании умножения вырабатывается сигнал, который переводит распределитель в следующее состояние, что вызывает подачу на входы умножителей нового текущего значения входной функции и соответствующего столбца матриа-55 цы интегрирования, -(К+2)-й сигнал траспределителя 5 выдает значение ин- -теграла на подынтервале на входы 18-20 сумматоров 24-26 и являет- ся сигналом записи в регистр 6 начапьных значений из сумматора 24 значения интеграла в последней точке подынтеграла, которое будет начальным значением интеграла на еле- дующем подынтервале. Далее цикл повторяется. В конце интервала интегрирования на выходе 18 будет получено значение интеграла на всем интервале,ю

Выключение устройства происходит через вход 23, который переводит триг-1- гер в нулевое состояние.

Формула изобретения 15

Цифровой интегратор, содержащий генератор импульсов, группу умножителей, группу накапливающих сумматоров и первый элемент И, входы которо- 20 го соединены с выходами признаков окончания операции умножителей группы, отличающийся тем, что, с целью повышения точности интегрирования, он содержит триггер, блок 25 памяти коэффициентов операторов интегрирования, регистр начального значения, распределитель импульсов, второй элемент И, блок элементов И} блок элементов ИЛИ и два элемента ИЛИ ,30 причем выход генератора импульсов соединен с первым входом второго элемента И, выход которого соединен с входом распределителя импульсов, группа выходов которого соединена с 35 адресными входами блока памяти коэффициентов операторов интегрирования и входами первого элемента ИЛИ, выход которого соединен с управляющим вхо- дом блока элементов И, информационные 40 входы которого соединены с информационными входами интегратора, а выходы - с-входами первых сомножителей умножителей группы, информационные выходы которых соединены с инфор - мационными входами накапливающих сумматоров группы, выходы которых соединены с выходами устройства, входы вторых сомножителей умножителей группы соединены с соответствующими группами выходов блока памяти коэффициентов операторов интегрирования, входы начальной установки интегратора соеди нены с входами первой группы блока элементов ИЛИ, входы второй группы которого соединены с выходами первого накапливающего сумматора группы, а выходы которого подключены к информационным входам регистра начального значения, выходы которого соединены с входами начального значения накапливающих сумматоров группы, вход запуска и останова интегратора соединены с входами установки в 1 и О соответственно триггера, выход которого соединен с вторым входом второго элемента И,третий вход которого соединен с выходом второго элемента ИЛИ, первый вход которого подключен к выходу первого элемента И, первый выход распределителя импульсов соединен с вторым входом второго элемента ИЛИ, входом чтения регистра начального значения и входами разрешения начальной установки накапливающих сумматоров группы, последний выход распределителя импульсов соединен с третьим входом второго элемента ИЛИ, синхровходами накапливающих сумматоров, группы и регистра началь-f ного значения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой интегратор | 1980 |

|

SU928351A1 |

| Устройство для решения линейных дифференциальных уравнений | 1987 |

|

SU1476486A1 |

| ЦИФРОВОЙ ИНТЕГРАТОР | 1973 |

|

SU409248A1 |

| Устройство для интегрирования | 1979 |

|

SU822194A1 |

| Модуль интегрирующей вычислительной структуры | 1984 |

|

SU1257641A1 |

| Цифровой интегратор | 1982 |

|

SU1042015A1 |

| Сейсмостанция | 1987 |

|

SU1430924A1 |

| ЦИФРОВОЙ ИНТЕГРАТОР | 2019 |

|

RU2710990C1 |

| Цифровой интегратор | 1984 |

|

SU1171789A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

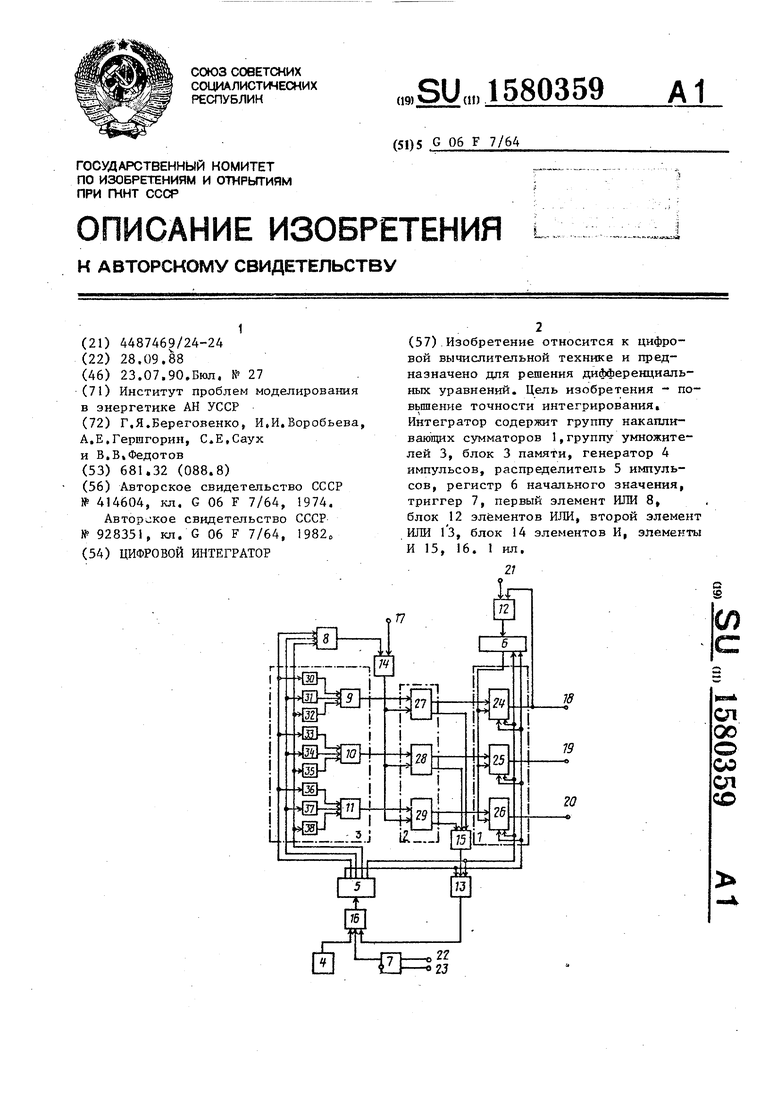

Изобретение относится к цифровой вычислительной технике и предназначено для решения дифференциальных уравнений. Цель изобретения - повышение точности интегрирования. Интегратор содержит группу накпливающих сумматоров 1, группу умножителей 3, блок 3 памяти, генератор 4 импульсов, распределитель 5 импульсов, регистр 6 начального значения, триггер 7, первый элемент ИЛИ 8, блок 12 элементоов ИЛИ, второй элемент ИЛИ 13, блок 14 элементов И, элементы И 15, 16. 1 ил.

| 1972 |

|

SU414604A1 | |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-07-23—Публикация

1988-09-28—Подача