мультиплексора 11, операционного усилителя 14, повторителя 8 напряжения. Устройство также позволяет производить регулировку параметров транзисторов в соответствии с цифровыми кодами, записанными в блок 2 памяти. Это осуществляется с помощью первого 5 и второго 12 аналоговых множительно-суммирующих блоков, первого 10 и второго 17 цифровых

1

Изобретение относится к электрическому моделированию и вычислительной технике и предназначено для электрического моделирования электронных цепей с помощью гибридных вы- числительных устройств.

Цель изобретения - повышение точности.

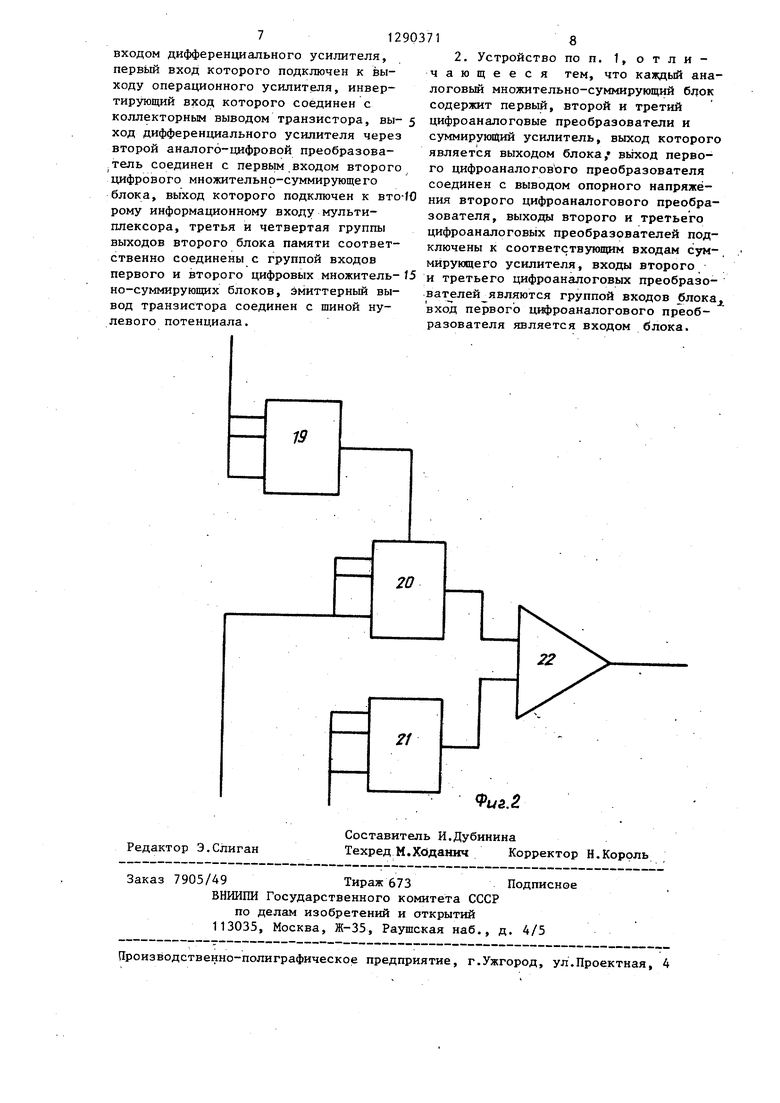

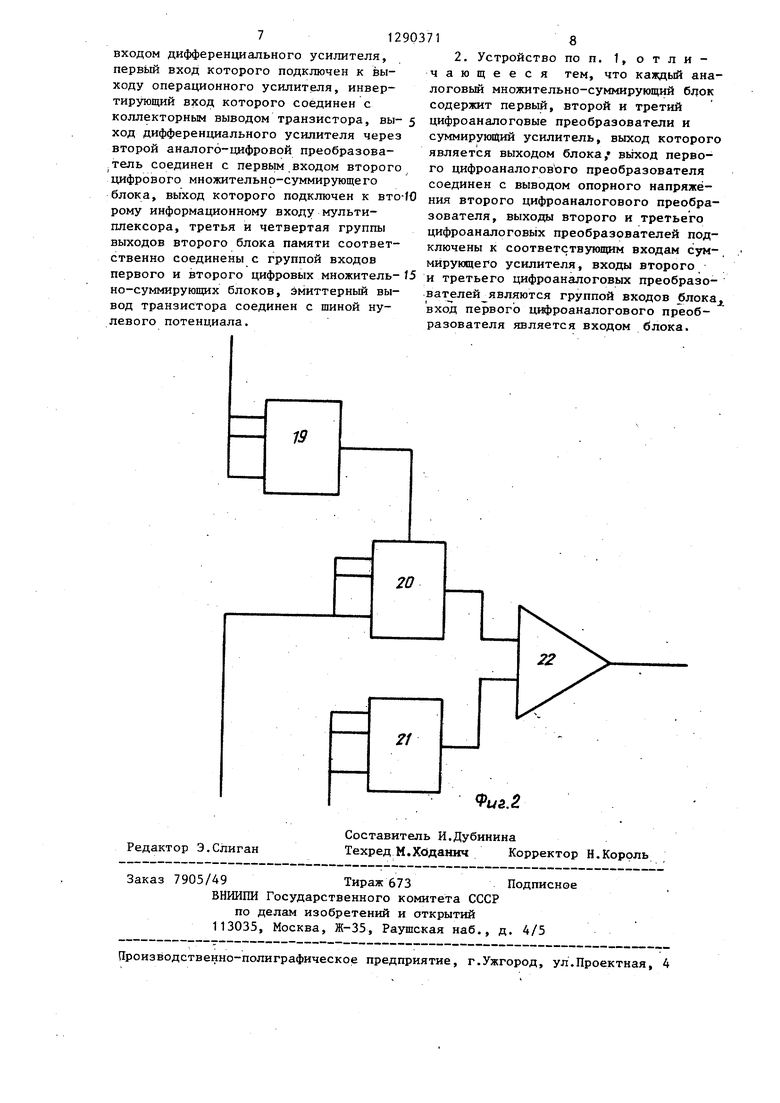

На фиг. 1 представлена структур- ная схема устройстваj на фиг. 2 - структура аналогового множительно- суммирующего блока.

Устройство для моделирования характеристик транзисторов включает блоки 1 и 2 памяти, шину 3 ввода ис- ходной информации устройства,.адресную шину 4 устройства, первый аналоговый множительно-суммирующий блок 5 управляемый источник 6 тока, иссле- дуемый транзистор 7, повторитель 8 напряжения, первый аналого-цифровой преобразователь 9, первый цифровой множительно-суммирующий блок 10,мультиплексор 11 , второй аналоговый мно- жительно-суммирующий блок 12, диффе- ренциальньй усилитель 13, операционный усилитель 14, токосъемный резистор 15, второй аналого-цифровой преобразователь 16, второй цифровой мно жительно-суммирующий блок 17, выходную шину 18 устройства. Каждый аналоговый множительно-суммирующий блок содержит с первого по третий цифро- аналоговые преобразователи 19-21, суммируюшдй усилитель 22.

Моделирование нелинейных характеристик транзисторов основано на принципе самоаналогии, когда один транзистор использует ся для моделирова- ния нелинейных характеристик нескольмножительно-суммирующих блоков, производящих операции умножения и сложения. Блок 1 памяти служит для запоминания входной информации на время преобразований. Обмен информацией с внеишими устройствами осуществляется с помощью шины 3 ввода Jисходной информации . Адресная шина 4 управляет обменом информацией , 2 ил.

ких однотипных транзисторов, имеющих- одинаковые параметры. Нелинейные свойства любого биполярного транзистора описьшаются семейством статических вольт-амперных характеристик, например, для схемы с общим эмиттером:

(1)

Us, (Ц, и„)-, Лк 4(is Vi где Ur.-. напряжение между базой и

эмиттером транзистора, - ток базы транзистора J и - напряжение между коллектором и эмиттером транзистора i,; - ток коллектора транзистора,- f и ср - некоторые нелинейные функции.

Так как все величины, входящие в формулу (1), представлены в аналоговом виде, то непосредственное использование транзистора в гибридных вычислительных устройствах, где входные и выходные переменные представлены в цифровом виде, невозможно. Кроме того, вид функции f и с|1 в формуле (1) зависит от технологии, топологии и условий эксплуатации транзистора. Для этого, чтобы учесть технологический, топологический и эксплуатационный разброс характеристик моделируемых транзисторов, необходимо ввести ряд изменяемых цифровым способом параметров.

В данном устройстве на входы аналоговых множительно-суммирующих блоков с выхода блока 1 поступают цифровые коды, соответствующие току базы ij. и напряжению коллектора U, моде

31

ли, a также с выхода блока 2 цифровы коды,.соответствующие параметрам трзистора N2, N3, N4, N5.

На выходе первого аналогового множительно-суммирующего блока появляется напряжение, которое поступает на управляемый источник тока, с выхода которого на базу транзистора задается ток, определяемый выражением

ij N2.1 + N3. (2)

С выхода второго аналогового множительно-суммирующего блока на коллекторный вывод транзистора подается напряжение, равное:

и,, N4 и, , + N5 . (3)

Такие блоки, как токосъемный резистор, операционный усилитель (с гальванически развязанным питанием) и дифференциальный усилитель служат для получения на выходе дифференциального усилителя напряжения, пропорционального току коллектора, определяемого следую1 Ц1м выражением:

i, Cp(i5, и,,) tp(N2.i + N3,

N4.U, + N5) (4)

где q) - нелинейная функция, описывающая характеристики моделирующего транзистора. На выходе повторителя напряжения при этом появляется следующее напряжение:

N4-u;,

UsV f(is, и«) f( N3, -- + N5) .(5) где f - нелинейная функция,описывающая характеристикитранзистора.

Оба напряжения поступают на входы 40 N1-N8, причем выходы блока 2 соотпервого и второго аналого-цифрового преобразователя, с выхода которых цифровые коды, соответствующие этим напряжениям, а также коды, соответствующие параметрам транзисторов N1, 5 N6, N7, N8, с выходов блока 2 памяти подаются на входы цифровых множительно-суммирующих блоков, которые выполняют операции умножения и суммирования. Тогда на выходе первого циф- 50 затем поступают на входы первого 5 рового множительно-суммирукнцего бло- и второго 12 блоков. В каждом анало- ка формируется цифровой код, в соот- говом множительно-суммирующем блоке

цифровой код, поступивший с выхода блока 1 памяти подаётся на вход пер- вого цифроаналогового преобразоватеветствующие параметрам транзисторов N2-N5, соединены соответственно с входами первого и второго аналоговых множительно-суммирующих блоков 5 и . 12. В блок 1 памяти по шине 3 ввода с помощью адресной шины 4 записываются цифровые коды, соответствующие току базы ig и напряжению коллектора и, модели транзистора, которые

(6)

ветствии с выражением:

V Nl-Ug + N6,

где Ug - напряжение между базой и эмиттером модели транзистора.

На выходе второго цифрового множительно-суммирующего блока формиля 19, на выходе которого формируется пропорциональное коду напряжение, которое поступает на вывод опорного напряжения второго цифроаналогового

руется цифровой код, определяемый по формуле

O

где

. м

Ч

М ил -т

IK N7.1

+ N8

(7)

- ток коллектора модели

транзистора.

Подставляя выражения (4) и (5) в формулы (6) и (7), получим уравнения, описывающие семейства статических вольт-амперных характеристик модели транзистора:

0

N1.f(N2-i + N3, N4-0,;+ N5) +

Uc, N1. f(N2-i

м

5

5

0

5

Бэ + N6,

i ; N7 Cf (N2 ig + N3, N4 UK, + + N5) + N8.(8)

Из уравнений (8) видно, что регулировка параметров транзистора осуществляется путем сжатия, растяжения и сдвига смсЗделированных характеристик транзистора относительно координатных осей. Это соответствует результатам исследований статических вольт-амперных характеристик биполярных транзисторов, вид которых является одинаковым для широкого класса транзисторов, и их можно получить один из других путем указанных операций.

В данном устройстве мультиплексор служит для подключения выходов цифровых множительно-суммирующих блоков к шине вывода устройства. Адресная шина осуществляет операции управления ввода и вывода данных.

Устройство работает следующим образом.

В блок 2 с помощью адресной шины 4 записываются цифровые коды, соответствующие параметрам транзисторов

затем поступают на входы первого 5 и второго 12 блоков. В каждом анало- говом множительно-суммирующем блоке

ветствующие параметрам транзисторов N2-N5, соединены соответственно с входами первого и второго аналоговых множительно-суммирующих блоков 5 и . 12. В блок 1 памяти по шине 3 ввода с помощью адресной шины 4 записываются цифровые коды, соответствующие току базы ig и напряжению коллектора и, модели транзистора, которые

цифровой код, поступивший с выхода блока 1 памяти подаётся на вход пер- вого цифроаналогового преобразователя 19, на выходе которого формируется пропорциональное коду напряжение, которое поступает на вывод опорного напряжения второго цифроаналогового

п реобразователя 20, на вход которого поступает цифровой код с одного выхода блока 2, таким образом на выходе второго цифроаналогового преобразователя образуется напряжение, пропорциональное произведению цифровых кодов, поступивших с выхода блока 1 памяти и одного выхода блока 2 памяти. Это напряжение подается на первы .вход суммирующего усилителя 22, на второй вход которого поступает напряжение с выхода третьего цифроаналогового преобразователя 21, пропорциональное цифровому коду, поступившему с другого выхода блока 2 памяти. На выходе первого и второго аналоговых множйтельно-суммирующих блоков 5 и 1 )Ормируются напряжения j соответствен ; ро определяемым формулам (2) и (3).

Напряжение с выхода первого бло- ка 5 поступает на вход управляемого источника 6 тока, который формирует ток базы транзистора 7. Повторитель 8 напряжения служит для подачи нап- ряжения Uj, определяемого выражением (5), на вход первого аналого- цифрового преобразователя 9, с выхода которого цифровой код, соответствующий напряжению U. а также цифро- вые коды с третьего выхода блоков 2 памяти, соответствующие параметрам транзисторов N1 и N6, поступают на входы первого цифрового множительно- суммирующего блока 10, на выходе которого формируется цифровой код, соответствующий вьфажению (6), и поступает на первый вход мультиплексора 111 Напряжение U. с выхода блока 12 поступает на-второй вход дифференциального усилителя 13 и далее без и зменения на коллектор транзистора 7, при этом дифференциальным напряжением операционного усили

1. Устройство для моделирования характеристик транзисторов, содержащее токосъемный резистор, один вывод которого соединен с Первым входом дифференциального усилителя, а {другой вывод соединен с коллекторным выводом транзистора, о т л и ч а - ю щ е е с я тем, что, с целью повы- ше ния точности, в него введены два .блока памяти, два цифровых множйтел но-суммирующих блока, мультиплексор управляемьй источник тока операцио ньй усилитель, повторитель напряжения, два аналого-цифровых преобразо вателя, два аналоговых множительно- суммирукщих блока, выход первого и которых через управляемьй источник 35 тока подключен к базовому выводу тр зистора, а через цепочку последовательно соединенных повторителя aпp жения и первого аналого-цифрового преобразователя соединен с первым входом первого цифрового множительн суммирующего блока, выход которого подключен к первому информационному входу {мультиплексора, выход которог является выходной шиной устройства.

теля 14 можно пренебречь. Ток коллек-.j щина ввода исходной информации усттора транзистора 7, определяемьй выражением (4), протекает также через токосъемный резистор 15 и вызывает появление на выходе операционного усилителя 14 напряжения, пропорционального току коллектора транзистора 7. Дифференциальный усилитель 13 служит для выделения разности напряжений меяоду выходом операционного усилителя 14 и его общим выводом. Напряжение с выхода дифференциального усилителя 13, пропорциональное току коллектора транзистора 7, поступает на вход второго

ройства соединена с информационными входами первого и второго блоков па мяти, входы разрешения записи и считывания, а также управляющий вход

50 мультиш :ексора соединены с адрес ной шиной устройства, первые и вторые группы выходов первого и вт рого блоков памяти подключены соответственно к входам первого и второ55 го аналоговых множйтельно-суммирующих блоков, выход второго аналогово го множительно-суммирующего блока соединен с неинвертирующим входом операционного усилителя и с вторым

аналого-цифрового преобразователя 16, с вьгхода которого цифровой код, соответствующий току i, а также цифровые коды с выхода блока 2 памяти, соответствующие параметрам транзисторов N7 и N8, поступает на входы второго цифрового множи- тельно-суммирующего блока 17, на выходе которого формируется цифровой

код, соответствующий выражению (7), и поступает на второй вход мультиплексора 11, с выхода которого численная информация поступает на шину 18 вывода в соответствии с состоянием адресной шины 4.

Формула изобретения

5 Q

1. Устройство для моделирования характеристик транзисторов, содержащее токосъемный резистор, один вывод которого соединен с Первым входом дифференциального усилителя, а {другой вывод соединен с коллекторным выводом транзистора, о т л и ч а - ю щ е е с я тем, что, с целью повы- ше ния точности, в него введены два .блока памяти, два цифровых множйтельно-суммирующих блока, мультиплексор, управляемьй источник тока операцион- ньй усилитель, повторитель напряжения, два аналого-цифровых преобразователя, два аналоговых множительно- суммирукщих блока, выход первого из которых через управляемьй источник 5 тока подключен к базовому выводу транзистора, а через цепочку последовательно соединенных повторителя aпpя- жения и первого аналого-цифрового преобразователя соединен с первым входом первого цифрового множительно- суммирующего блока, выход которого подключен к первому информационному входу {мультиплексора, выход которого является выходной шиной устройства.

0

.j щина ввода исходной информации устройства соединена с информационными входами первого и второго блоков памяти, входы разрешения записи и считывания, а также управляющий вход

мультиш :ексора соединены с адресной шиной устройства, первые и вторые группы выходов первого и второго блоков памяти подключены соответственно к входам первого и второго аналоговых множйтельно-суммирующих блоков, выход второго аналогового множительно-суммирующего блока соединен с неинвертирующим входом операционного усилителя и с вторым

712

входом дифференциального усилителя, первьй вход которого подключен к выходу операционного усилителя, инвертирующий вход которого соединен с коллекторным выводом транзистора, вы- ход дифференциального усилителя через второй аналого-цифровой преобразова- .тель соединен с первым .входом второго цифрового множительно-суммирующего

блока, выход которого подключен к вто-/0 ния второго цифроаналогового преобрарому информационному входу мультиплексора, третья и четвертая группы выходов второго блока памяти соответственно соединены с группой входов

зователя, выходы второго и третьего цифроаналоговых преобразователей подключены к соответствующим входам суммирующего усилителя, входы второго

первого и второго цифровых множитель- 15и третьего цифроаналоговых преобразо-

но-суммирующих блоков, эмиттерный вы-вателей являются группой входов блoкaJ,

вод транзистора соединен с шиной ну-вхоТ первого цифроаналогового преоблевого потенциала.разователя является входом блока.

8

2. Устройство по п. 1, отличающееся тем, что каждый аналоговый множительно-суммирующий 6jjoK содержит первый, второй и третий цифроаналоговые преобразователи и суммирующий усилитель, выход которого является выходом блока, выход первого цифроаналогового преобразователя соединен с выводом опорного напряжёзователя, выходы второго и третьего цифроаналоговых преобразователей подключены к соответствующим входам суммирующего усилителя, входы второго

и третьего цифроаналоговых преобразо-

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифроаналоговая вычислительная система | 1987 |

|

SU1483468A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ИЗМЕНЕНИЯ СОПРОТИВЛЕНИЯ РЕЗИСТИВНЫХ ДАТЧИКОВ В ЭЛЕКТРИЧЕСКИЙ СИГНАЛ | 2010 |

|

RU2499237C2 |

| Вычислительное устройство | 1982 |

|

SU1040493A1 |

| Функциональный преобразователь | 1979 |

|

SU830430A1 |

| Программируемое многофункциональное аналого-цифровое устройство сопряжения | 1988 |

|

SU1559355A1 |

| АНАЛОГО-ЦИФРОВАЯ МНОГОПРОЦЕССОРНАЯ СИСТЕМА | 2006 |

|

RU2333533C1 |

| СТАБИЛОГРАФ | 1994 |

|

RU2095025C1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| Устройство для считывания графической информации | 1987 |

|

SU1434461A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СРЕДНЕКВАДРАТИЧЕСКОГО ЗНАЧЕНИЯ НАПРЯЖЕНИЯ | 2000 |

|

RU2198410C2 |

Устройство предназначено для электрического моделирования элект- .ронных цепей, содержапщх биполярные транзисторы, с помощью гибридных вычислительных устройств; Цель изобретения - повьшение точности. Это достигается введением Первого 9 и второго 16 аналого-цифровых преобразователей, первого 5 и второго 12 аналоговых множительно-суммирующих блоков, производящих преобразование информации соответственно из арало- говой формы в цифровую и обратно. :

Редактор Э.Слиган

Заказ 7905/49Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

1/3.2

Составитель И.Дубинина

Техред М.ХОданич Корректор Н.Король

| Патент США № 3471786, кл | |||

| Телефонный аппарат, отзывающийся только на входящие токи | 1921 |

|

SU324A1 |

| Запальная свеча для двигателей | 1924 |

|

SU1967A1 |

| Устройство для моделирования транзистора | 1979 |

|

SU868787A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-15—Публикация

1985-08-21—Подача