1

12904

Изобретение относится к вычислительной технике, а именно к полупроводниковым запоминающим устройствам, и может быть использовано при изготов последних в интегральном испол- нении.

Целью изобретения является повьше- ние надежности работы запоминающего устройства.

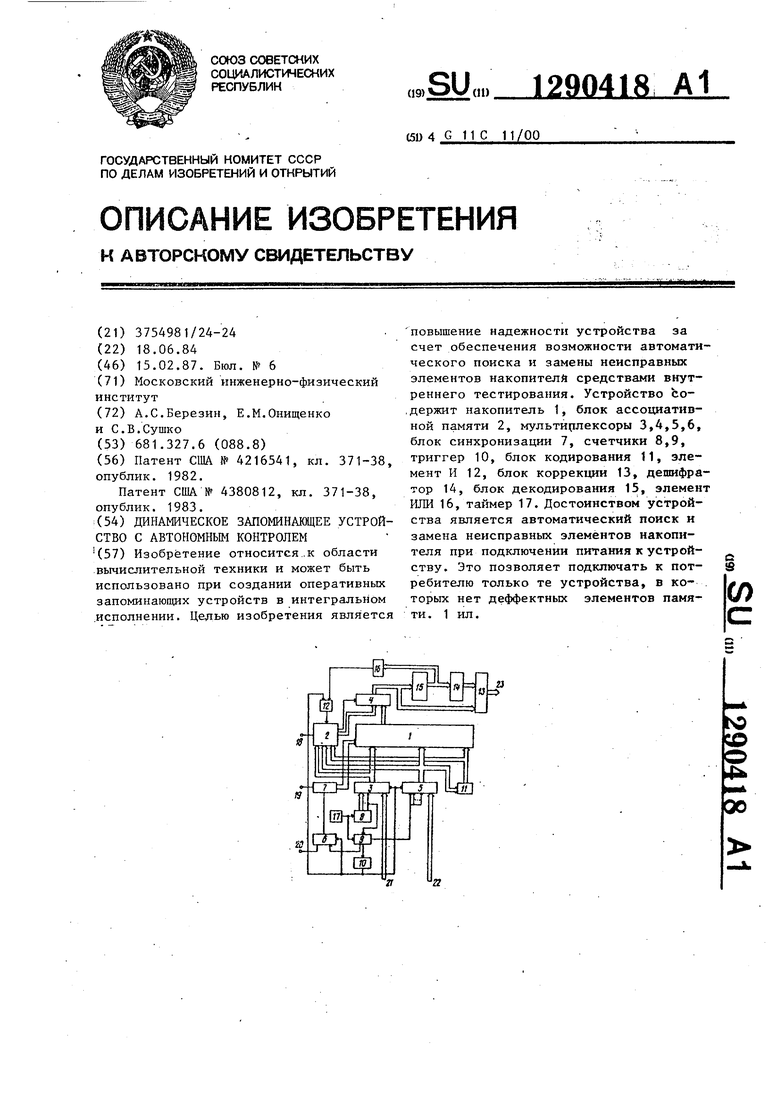

На чертеже показана блок-схема устройства.

Устройство содержит накопитель 1, блок 2 ассоциативной памяти, первый 3, второй 4, третий 5 и четвертый 6 Мультиплексоры, блок 7 синхронизации, основной счетчик 8, дополнительный счетчик 9, триггер-защелку 10, блок 11 кодирования, элемент И 12, блок 13 коррекции, дещифратор 14, блок 15 декодирования, элемент ИЛИ 16, таймер 17, управляющий выход 18, вход 19 выборки кристалла, вход 20 режима, адресные входы 21, информационные входы 22 и информационные выходы 23.

Устройство работает следующим образом.

При подключении питания к устройству основной и дополнительный счетчики 8 и 9 устанавливаются в нулевые состояния, а триггер-защелка 10 - в состояние 1 (цепи начальной установки не показаны). Нахождение триггера-защелки 10 в состоянии 1 укат зьшает на работу запоминающего устройства с коррекцией ошибок в режиме самотестирования, при котором дроис- ходит проверка работоспособности элементов памяти накопителя 1 тестом Последовательные запись/считьшание О и 1.

С второго выхода дополнительного счетчика -9 через третий мультиплексор 5 на входы информационных разрядов накопителя 1 поступают тестовые комбинации сигналов 00...О или 11...1. Если для блока 11 кодирования выбрать матрицу формирования контрольных раз- рядов такую, что каждый контрольный разряд будет равен сумме по модулю 2 например, нечетного числа информаци- онных разрядов, то при указанных тестовых комбинациях информационных разрядов для контрольных разрядов также будет иметь место перебор значений О и 1.

В режиме :Самотестирования основной счетчик 8 обеспечивает последовательный перебор слов накопителя 1, а до

5

О

5 0

0 5

0

182

полнительньй счетчик 9 - смену режимов записи и считывания и задание тестовой комбинации. Если в ходе самотестирования обнаружена ошибка (предполагается, что она вызвана дефектным элементом памяти накопителя 1), т.е. на выходах блока 15 декодирования присутствует ненулевая комбинация сигналов, текущий адрес слова запоминается в признаковой части блока 2 ассоциа.тивной памяти. Занесение адресов дефектных элементов памяти в блок 2 ассоциативной памяти разрешается сигналом с элемента И 12 только в режиме самотестирования. В режиме внещних обращений совпадение внещне- го адреса 21 и адреса, хранимого в признаковой части блока 2 ассоциативной памяти, инициирует запись (в режиме внешней записи) или считывание (в режиме внешнего считывания) из числовой части блока 2 ассоцид- тивной памяти соответствующих информационных и контрольных разрядов. Управляющий выход блока 2 ассоциативной памяти используется дня реги- страции переполнения признаковой части; в этом случае запоминающее устройство признается негодным.

Цикл самотестирования завершается после проверки всех элементов памяти накопителя 1. При этом сигнал с выхода дополнительного счетчика 9 перебрасывает триггер-защелку 10 в состояние О ., которое переключает мультиплексоры 3, 5 и 6 на пропуск сигналов С внешних вх одов устройства.

Формула изобретения

Динамическое запоминающее устройство с автономным контролем, содержащее накопитель, адресные и управляющие входы которого подключены соответственно к выходам первого мультиплексора и блока синхронизации, а входы контрольных разрядов соединены с выходаш блока кодирования, таймер, выход которого подключен к входу основного счетчика, выходы которого соединены с входами первой группы первого мультиплексора, входы второй группы которого являются адресными входами устройства, дешифратор, входы которого подключены к выходам блока декодирования, а вьгходы соединены с входами- первой группы блока коррек- щга, выходы которого являются инфор312

мационными выходами, а первый вход блока синхронизации - входом выборки кристалла устройства, отличающееся тем, что, с целью повышения надежности устройства, в него введены блок ассоциативной памяти, второй, третий и четвертый мультиплексоры, дополнительный счетчик, триггер, элемент ИЛИ и элемент И, причем входы элемента ИЛИ подключены к выхо- дам блока декодирования., а выход соединен с первым входом.элемента И, второй вход которого подключен к управляющим входам первого, третьего и четвертого мультиплексоров и к вы- ходу триггера, вход которого соединен с третьим выходом дополнительного счетчика, первый и второй выходы ко- торого подключены соответственно к первому информационному входу четвертого мультиплексора и к входам первой .группы третьего мультиплексора, а входы соединены соответственно с выходом таймера и одним из выходов основного счетчика, второй информационный вход четвертого мультиплексора

Редактор К.Волощук

Составитель С.Сушко

Техред Л.Олейник Корректор А.Обручар

Заказ 7910/52Ти раж б11 - Подписное

ВНИИЛИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

, Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

184

является входом режима устройства, а выход подключен к второму входу блока синхронизации, выходы третьего мультиплексора соединены с входами информационных разрядов накопителя и с входами блока кодирования, а входы второй группы являются информацонными входами устройства, информационные входы первой, второй и третьей групп блока ассоциативной памяти подключены соответственно к выходам первого и третьего мультиплексоров,и блока кодирования, управляющий вход соединен с выходом элемента И, первый управляю- щий выход является управляющим выходом устройства, а второй управляющий выход и информационные выходы блока . ассоциативной памяти подключены соответственно к управляющему и к информационным входам первой группы второго ьгультиплексора, информацион1ще входы второй группы которого соединены с выходами накопителя, а выходы йод- ключены к входам блока кодирований и к входам второй г руппы блока коррекции.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с автономным контролем | 1980 |

|

SU903990A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU374657A1 |

| Логическое запоминающее устройство | 1981 |

|

SU972589A1 |

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

| Ассоциативное запоминающее устройство | 1982 |

|

SU1056269A1 |

| Сигнатурный анализатор | 1986 |

|

SU1386995A1 |

| Запоминающее устройство с автономным контролем | 1991 |

|

SU1837363A1 |

| Ассоциативное оперативное запоминающее устройство | 1981 |

|

SU978197A1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

| Ассоциативное запоминающее устройство | 1988 |

|

SU1520595A1 |

Изобретение относится ..к области вычислительной техники и может быть использовано при создании оперативных запоминающих устройств в интегральном исполнении. Целью изобретения является повышение надежности устройства за счет обеспечения возможности автоматического поиска и замены неисправных элементов накопители средствами внутреннего тестирования. Устройство со,держит накопитель 1, блок ассоциативной памяти 2, мультиплексоры 3,4,5,6, блок синхронизации 7, счетчики 8,9, триггер 10, блок кодирования 11, элемент И 12, блок коррекции 13, дешифратор 14, блок декодирования 15, элемент ИЛИ 16, таймер 17. Достоинством устройства является автоматический поиск и замена неисправных элементов накопителя при подключении питания к устройству. Это позволяет подключать к потребителю только те устройства, в которых нет деффектных элементов памяти. 1 ил. i (У) X л г

| Патент США № 4216541, кл | |||

| Гидравлическая передача, могущая служить насосом | 1921 |

|

SU371A1 |

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

| Патент США № 4380812, кп | |||

| Гидравлическая передача, могущая служить насосом | 1921 |

|

SU371A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1987-02-15—Публикация

1984-06-18—Подача