(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С АВТОНОМНЫМ

КОНТРОЛЕМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство с автономным контролем | 1983 |

|

SU1113855A2 |

| Оперативное запоминающее устройство с автономным контролем | 1978 |

|

SU744738A1 |

| Запоминающее устройство с автономным контролем | 1981 |

|

SU1010659A2 |

| Запоминающее устройство с автономным контролем | 1981 |

|

SU970479A1 |

| Оперативное запоминающее устройство с автономным контролем | 1979 |

|

SU947912A2 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU368647A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1805503A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU936033A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU374657A1 |

| Запоминающее устройство | 1985 |

|

SU1295456A1 |

1

Изобретение относится к запоминающим устройствам и может быть использовано при разработке накопителей на базе интегральных матриц с дефектами.

Известно запоминающее устройство, содержащее накопитель, входь которого подключены к выходам элементов ИЛИ и дещифратора, соединенного с регистром адреса, а выход - к регистру слова, подключенному к блоку кодирования-декодирования, выход которого соединен с одними входами элементов ИЛИ, другие входы элементов ИЛИ подключены к выходу блока обнаружения и анализа неисправностей накопителя, соединенного с блоком формирования управляющего кода, входы блока обнаружения и анализа неисправноотей накопителя и блока формирования управляющего кода соединены с выходом регистра слова.

В известном устройстве в ячейку накопителя вместе с информационным словом записывается дополнительная комбинация инвертирования, составленная в ре-

зультате проведенного анализа характера отказа неисправных разрядов ячеек (генератор О или генератор ) и сравнениями их со значениями соответствующих разрядов штформагоюнного слова СИ .

Недостатками известного устройства являются невысокое быстродействие и низкая информационная емкость. Запись информации в устройство осуществляется в течение трех периодов обращения к на10копителю, а в режиме чтения в работе участвует блок кодирования-декодирования. Кроме того, в каждой ячейке необходимо выделять разряды для хранения дополнительной кодовой комбинации.

15

Наиболее близким по технической сущности к предлагаемому является запоминающее устройство с автономным контролем, содержащее адресный блок памяти, соединенный с первым ассоциативным

20 блоком памяти, второй ассоциативный блок памяти, один из входов которого соединен с первым входом адресного бло ка памяти, блок управления, выходы ко39039904

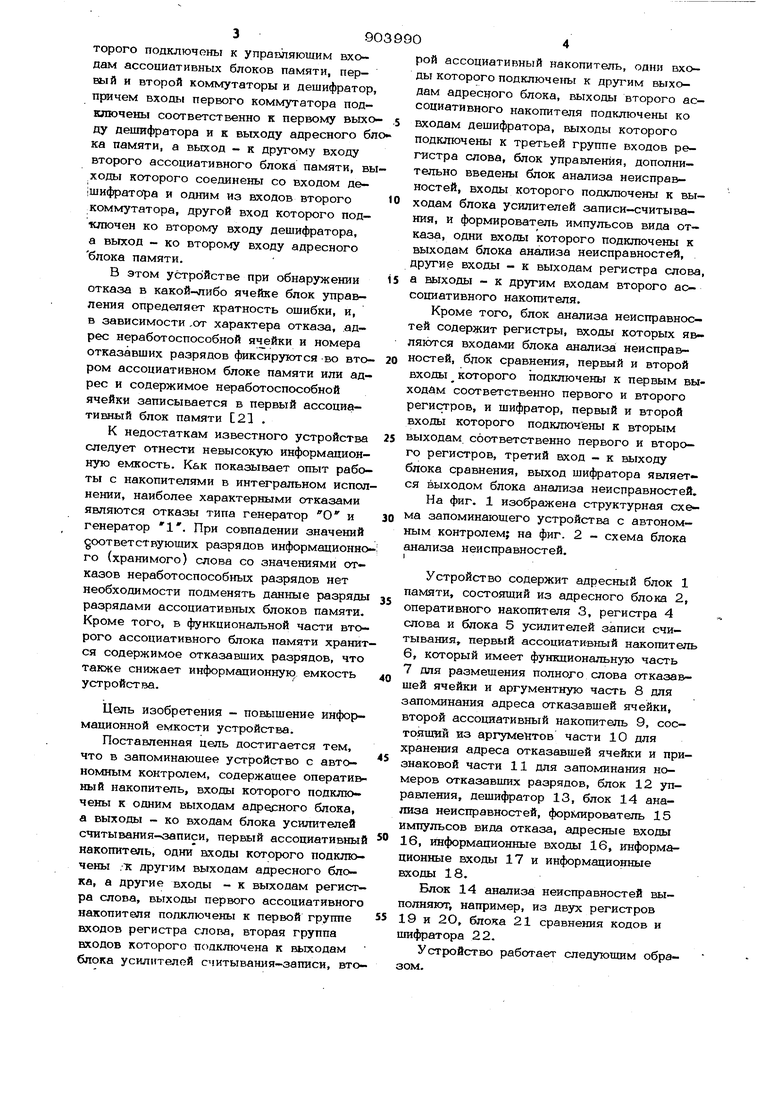

торого подключены к управляющим вхо-рой ассоциативный накопитель, одни входам ассоциативных блоков памяти, пер-ды которого подключены к другим выховый и второй коммутаторы и дешифратор, причем входы первого коммутатора подключены соответственно к первому выхо- .5входам дешифратора, выходы которого ду дешифратора и к выходу адресного бло-подключены к третьей группе входов река памяти, а выход - к другому входу второго ассоциативного блока памяти, выходы которого соединены со входом де- (Шифратора и одним из входов второго коммутатора, другой вход которого подключен ко второму входу дешифратора, а выход - ко второму входу адресного блока памяти. В этом устройстве при обнаружении отказа в какой-либо ячейке блок управления определяет кратность ошибки, и, в зависимости ,от характера отказа, .адрес неработоспособной ячейки и номера отказавших разрядов фиксируются во втором ассоциативном блоке памяти или адрес и содержимое неработоспособной ячейки записывается в первый ассоциативный блок памяти 21 . К недостаткам известного устройства следует отнести невысокую информационную емкость. Как показывает опыт работы с накопителями в интегральном исполнении, наиболее характерными отказами являются отказы типа генератор О и генератор 1. При совпадении значений соответствующих разрядов информационного (хранимого) слова со значениями отказов неработоспособных разрядов нет необходимости подменять данные разряды разрядами ассоциативных блоков памяти. Кроме того, в функциональной части второго ассоциативного блока памяти хранит ся содержимое отказавших разрядов, что также снижает информационнук) емкость устройства. Цель изобретения - повышение информационной емкости устройства. Поставленная цель достигается тем, что в запоминающее устройство с автономным контролем, содержащее оперативный накопитель, входы которого подключены к одним выходам адресного блока, а выходы - ко входам блока усилителей считывания-записи, первый ассоциативны накопитель, одни входы которого подклк чены другим выходам адресного блока, а другие входы - к выходам регнст ра слова, выходы первого ассоциативного накопителя подключены к первой группе входов регистра слова, вторая группа Елодов которого подключена к выходам блока усилителей считывания-записи, вто

дам адресного блока, выходы второго ассоциативного накопителя подключены ко гистра слова, блок управления, дополнительно введены блок анализа неисправностей, входы которого подключены к выходам блока усилителей записи-считывания, и формирователь импульсов вида отказа, одни входы которого подключены к выходам блока анализа неисправностей, другие входы - к выходам регистра слова, а выходы - к другим входам второго ассоциативного накопителя. Кроме того, блок анализа неисправностей содержит регистры, входы которых являются входами блока анализа неисправ- ностей, блок сравнения, первый и второй входы которого подключены к первым выходам соответственно первого и второго регистров, и шифратор, первый и второй входы которого подключены к вторым выходам соответственно первого и второго регистров, третий вход - к выходу блока сравнения, выход шифратора является выходом блока анализа неисправностей. На фиг. 1 изображена структурная схе- а запоминающего устройства с автономным контролем; на фиг. 2 - схема блока анализа неисправностей. Устройство содержит адресный блок 1 ™ состоящий из адресного блока 2, оперативного накопителя 3, регистра 4 ° « ° усилителей записи считывания, первый ассоциативный накопитель 6, который имеет функциональную часть 7 для размещения полного слова отказавшей ячейки и аргументную часть 8 для запоминания адреса отказавшей ячейки, второй ассоциативный накопитель 9, состоящий из аргументов части 10 для хранения адреса отказавшей ячейки и признаковой части 11 для запоминания номеров отказавших разрядов, блок 12 управления, дешифратор 13, блок 14 анализа неисправностей, формирователь 15 импульсов вида отказа, адресные входы 16, информационные входы 16, информационные входы 17 и информационные входы 18. Блок 14 анализа неисправностей выполняют, например, из двух регистров 19 и 2О, блока 21 сравнения кодов и шифратора 22. Устройство работает следующим образом. На адресные входь 16 поступает адрес ячейки, к которой необходимо обратиться, а на информапионные входы 18 информационное слово, которое необходи мо записать для хранения в оперативны накопитель 3, Производится обращение к запрашиваемой ячейке оперативного на копителя 3, т.е. осуществляется запись обратного кода слова с регистра 4 слова в оперативный накопитель 3 и считы вание обратного кода, который поступае на блок 14. Затем осуществляется запи прямого кода содержимого регистра 4 слова в ту же ячейку оперативного нако пителя 3 и вновь считывание на блок 1 В блоке 14 происходит определение, в каких разрядах запрашиваемой ячейки накопителя имеет место отказ, определяется вид отказа ( в каких разрядах отказ типа генератор О, а в каких - генератор ). Полученная информация передается на вход формирователя 15 импульсов вида отказа, на второй вход которого поступает с регистра 4 слова информационное слово, прямой код которого записан в ячейку оперативного накопителя 3. В формирователе 15 импульсов вида отказа анализируется, в каких разрядах вид отказа совпадает с двоичными зна- чениями битов записываемого информационного слова, а в каких разрядах вид отказа не совпадает с двоичным значени ем битов. В зависимости от результатов анализа устройство работает следующим образом. Если значения соответствующих битов записываемого информационного слова совпадают с видами отказов разрядов ячейки, то осуществляется запись следую щего информационного слова по очередному адресу (т.е. в адресный блок 2 поступает новый адрес, а в регистр 4 слова - новое информационное слово). Аналогично устройство работает и в случае, если в ячейке, к которой происходит обращение, нет отказавших разрядов. Если количество отказавших разрядов, в которых вид отказа не совпадает со значениями соответствующих битов информационного слова ( ), меньше или равно п , где определяется из выражения m {og, и fe и ( 1 - количество разрядов слова, записываемого в блок 1), то в этом случае в аргументную часть 10 второго ассоциативного накопителя 9 записывается адрес ячейки с .адресного блока 2, а в признаковую часть 11 записываются номера отказавших разрядов, в которых вид отказа не совпал со значениями соответствующих битов записываемого слова. Причем запись производится в ту ячейку ассоциативного накопителя 9, в которой количество признаковых частей 11 соответствует числу ип. Если, количество отказавших разрядов, в которых вид отказа не совпадает со значениями соответствующих битов инфор 1ационного слова, больше ип, то адрес ячейки, к которой происходит обращение, записывается а;фесным блоком 2 в часть 7 первого ассоциативного накопителя 6, а информационное слово - с.регистра 4 слова в функциональную часть 8. При выполнении операции чтения происходит выборка содержимого ячейки оперативного накопителя 3 на регистр 4 слова, одновременно, осуществляется ассоциативный поиск адреса в первом 6 и втором 9 ассоциативных накопителях. Если в накопителях 6 и 9 такого адреса нет, то содержимое регистра 4 слова без изменений выдается на выход 17. Если адрес обнаружен в первом ассоциативном накопителе 6, то содержимое ячейки, связанной с этим адресом, выдается на регистр 4 слова и далее на выход 17. При обнаружении адреса обращения во втором ассоциативном накопителе 9 содержимое признаковой части 11 данной ячейки поступает на дешифратор 13, который указывает, какие разряды регистра 4 слова необходимо при выдаче проинвертировать. Правильное значение слова выдается на вышд 17. Таким образом, предлагаемое устройство позволяет подменять только те неработоспособные ячейки, в которых вид отказа не совпадает со значением соответствующих бит информационного слова, что повышает информационную емкость устройства. Формула изобретения 1. Запоминающее устройство с автономньм контролем, содержащее оперативый накопитель, входы которого подклюены к одним выходам адресного блока, выходы - ко входам блока усилителей читывания-записи, первый ассоциативный акопитель, одни входы которого подклю-; ены к другим выходам адресного блока, другие входы - к вькодам регистра лова, выходы первого ассоциативного 79 накопителя подключены к первой группе ВХОДОВ регистра слова, вторая группа входов которого подключена к выходам блока усилителей считывания-записи, второй ассоциативный накопитель, одни входы которого подключены к другим выходам адресного блока, выходы второго ассоциативного накопителя подключены ко входам дешифратора, выходы которого . подключены к третьей группе входов регистра слова, блок управления, о т л и чающееся тем, что, с целью повышения информационной емкости устройства, оно содержит блок анализа неиоправностей, входы которого подключены к йыходам блока усилителей считываниязаписи, и формирователь импульсов вида отказа, одни входы которого подключены к выходам блока анализа неисправностей, другие входы - к выходам регистра слова, а вькодь - к другим входам второго ассоциативногб накопителя.

Фиг. f 908 2. Устройство по п. 1, отличающее с я тем, что блок анализ неисправностей содержит регистры, входы которых являются входами блока анализа неисправностей, блок сравнения, первый и второй входы которого подключены к первьп выходам соответственно первого и второго регистров, и шифратор, первый и второй входы которого подключены к вторым входам соответственно первого и второго регистров, третий вход - к выходу блока сравнения, выход щифратора является выходом блока анализа неисправностей. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 600618, кл. Gil С 29/00, 1976. 2., Авторское свидетельство СССР по заявке № 2600719/18-24, кл. &11 С 29/00, 1978 (прототип).

Авторы

Даты

1982-02-07—Публикация

1980-05-05—Подача