1

Изобретение относится к области запоминающих устройств.

Известно запоминающее устройство (ЗУ), соде|ржащее ааресный накооитель, адре.оные цепи .которого ладключены к регистру адреса, а .разрядные - к блокаы 1Коди1р.01ва1Ния и декодироваяия, ассоциативный накопитель, подключенный к регистру ад/реса и регистру слова.

Однако .в нем емкость ассоциативного накапителя агранич.Ивает количество иеиоправньпх ячеек, при .которам допускается работа ЗУ.

Предлагаемое устройстао отличается от известного тем, что оно содержит дополнительный ассоциативный накопитель и регистр мощности коррвкти рую.щвго кода, один выход .которого -под кЛЮчвн ко входам блоков коди/рованИя и декодирования, а вход и другой выход под ключены к долол«ительнаму ассоц.иати1В:наму нак опителю, инфор)ма1Ц.ио.нный вход которого, пойсоединен к основному ассоциатиданаму накопителю, а признаковый вход - к выходу в(ведвЕНОЙ в устройство схемы «ИЛИ, один вход .которой подключен к выходу регистра адреса, а другой - к признаиовому вььходу о.сновного ассоциатннного накопителя. Это позволяет устройству работать и при числе отка13ов, лревыщающем емкость ассоциативного накоп-ителя.

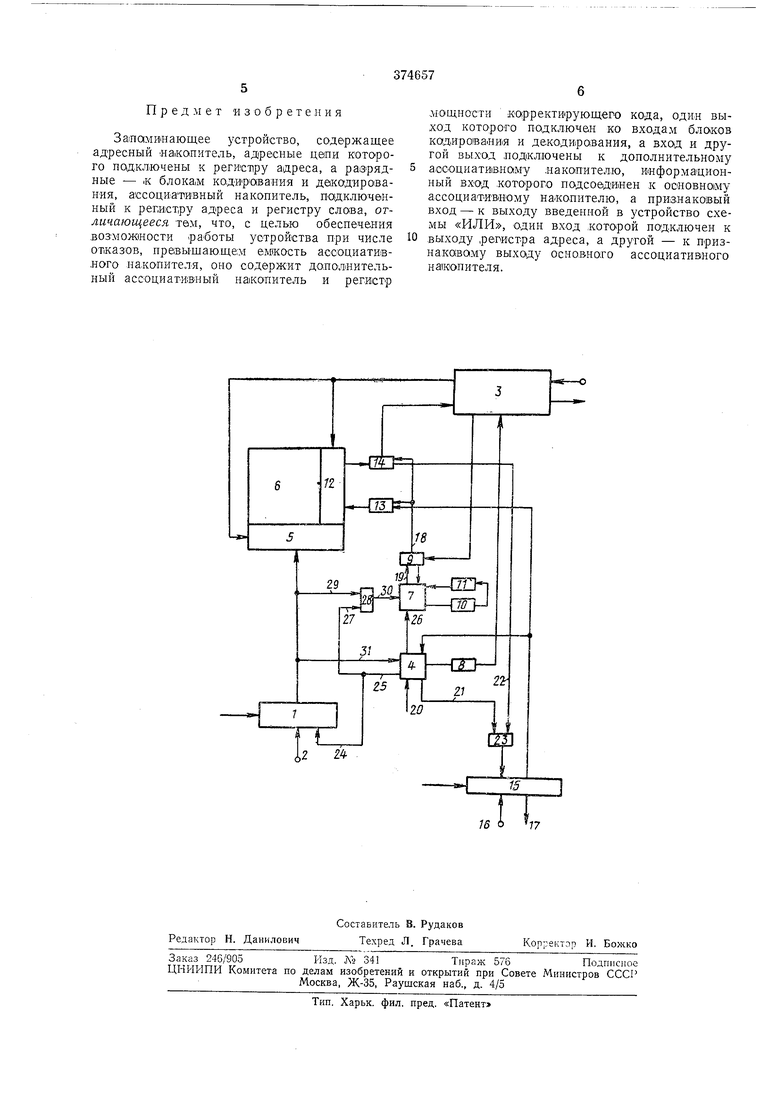

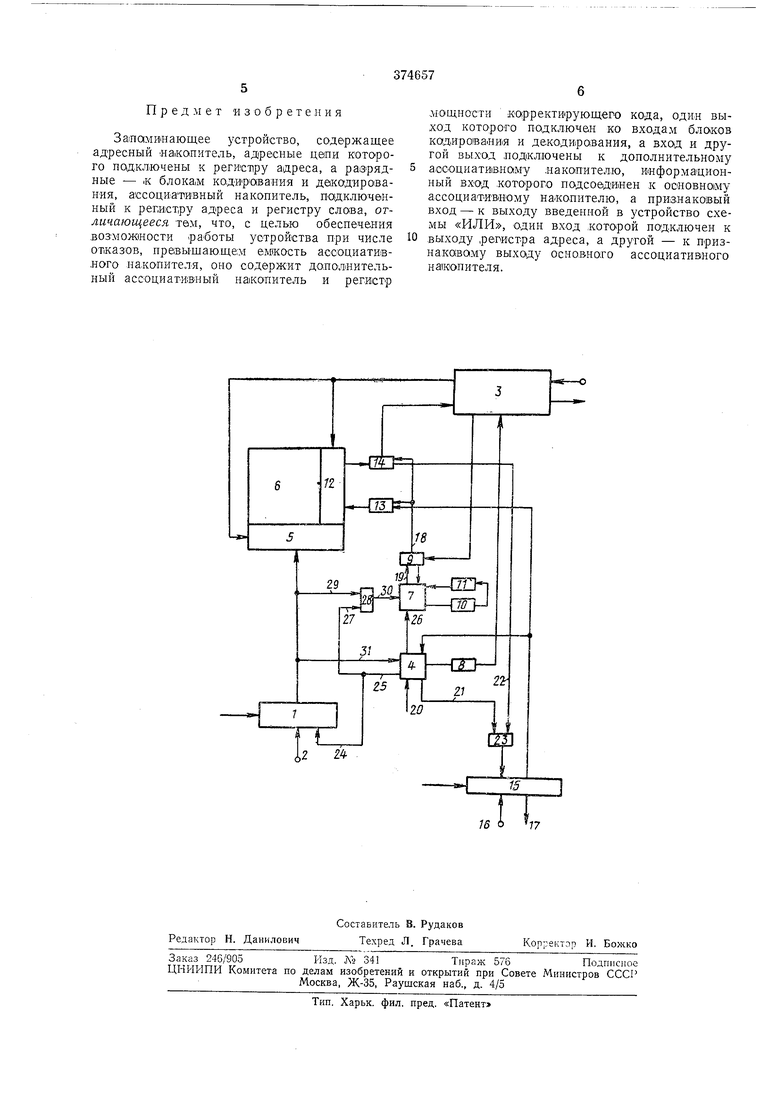

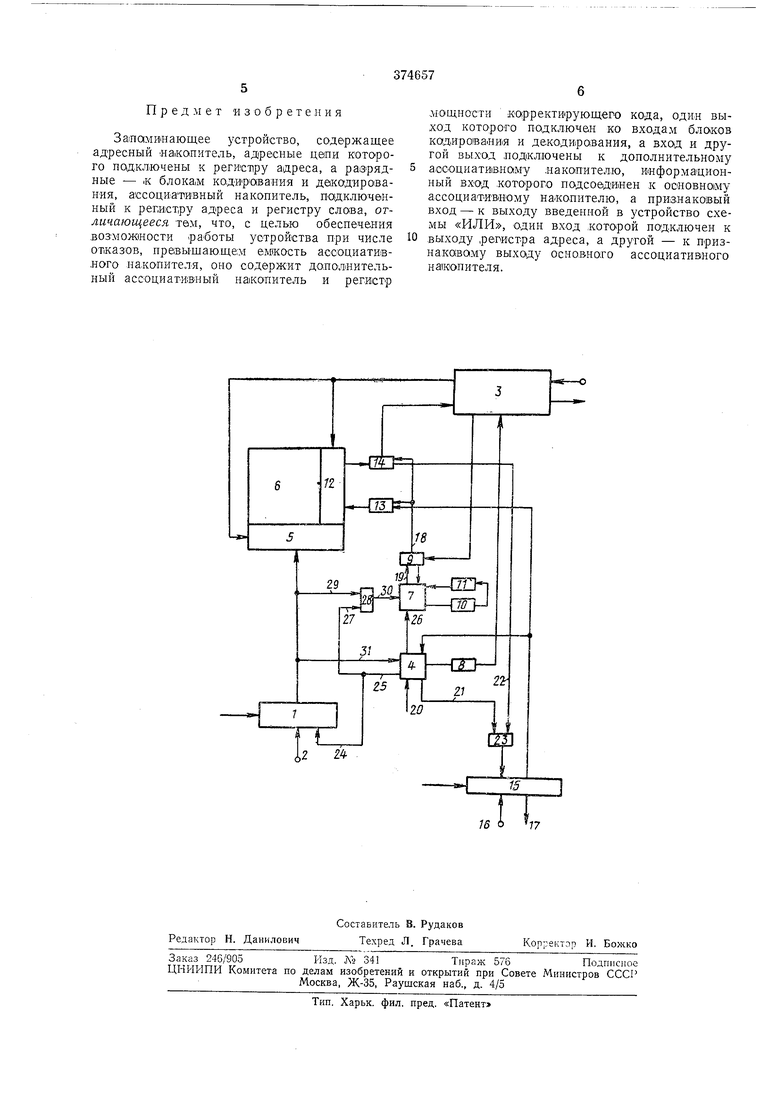

На че ртвже «зобралсена блок-схема предлагаемого устройст1ва.

Устройство содержит регистр / а.дреса с информационным входом 2. Утрасляющие входы регистра 1 соединены с блоком местного управления 3. Выходы регистра / соединены с входами опрОса ассоциатигвного накопителя (АНУ 4. Выход (регистра / адреса подключен к адресным цепя1М 5 адресного накопителя 5 и ко входу АН 4. АН 4 соед.инев с дополнительным АН 7 и узлом 8 занятости и переполнения, связанным с блоком 3, к которому подключен регистр мощности корректирующего хода (РМКК) 9.

Выход дополнительного узла 10 занятости и переполнения и бдока 3 подключены к регистру маски 11, выход которого связан с АН 7. Разрядные цепи 12 адресного накопителя 6 соединены с блока;мИ кодирования 13 и декодирования 4. Управляющий выход последнего под|ключе.н к блоку 3. Регистр слова 15 содержит вход 16 и выкод 17.

Управляющий выход 18 РМКК 9 соединен с блоками 13 и 14 а вход - с блоком 3.

Информационный вход 19 РМКК 9 соединен с АН 7. АН 4 содерж.ит вход записи 20. Выходы АН 4 и блока декодирования 14 посредством ШИН 21 я 22 к через вс;помогательяу,ю схему «ИЛИ 23 соединены с регистром слова 15. Вход 24 регистра адреса ) подгключен к признаковому выходу 25 АН 4, который подсоединен к инфорчмационному входу 26 АН 7.

П|риз:накавы1Й .вы.ход 25 АН 4 подключен к первому входу 27 схемы «ИЛИ 28, второй вход 29 которой подсоединен к региCTipa адреса 1, а выход - ж призлаковому вхаду 30 дополнительного АН 7.

Предлагаемое устройспво работает следующим образом. Одним из слособов (например с ПОМОЩЬЮ контролирующих п-рОПрамм, затгаси - считььвапия прямых « обратных кодов с последующим сравнением) определяют адреса отказавщих ячеек и кратность отказав в .них. Эти адреса и кратности отказов заносятся по входу записи 20 в признаковые части ячеек АН 4, информационные части коTOipbix используются нри этом для замены неисправных ячеек адресного накопителя 6. РМКК 9 устанавливается на миннмальную мощность. Нри этом возможны два режима работы.

При первом режиме РМКК настраивается на код, обнаруживающий одну ощибку. Адреса отказавщих ячеек и кратность ошибок в ячейке по входу 20 записываются в сво1бодные ячейки АН 4, которые определяются по нулевому состоянию триггеров занятости соответствующей ячейки в узле 8. При записи очередного адреса опказавщей ячейки 3 АН 4 соответствующий триггер занятости в узле 5 переходит в состояние «1.

После записи в АН 4 адресов всех отказавщих ячеек накопителя 5 и их кратности отказов и цри отсутствии сигнала переполнения на выходе узла 8 устройство готово к работе.

На вход 2 регистра 1 поступает адрес ячейки, ж которой необходимо обратиться, а на 1входы блока 3 поступают сигналы кода операции и начала опе|рации. Адрес с регистра 1 поступает на входы 5/ и 30 АН 4 и АН 7 соответсивенно и на адресные пепи 5 накопителя 6. При этом обращение возможно либо iK АН 4, либо к накопителю 6 и к. АН 7. При обращении к АН 6, который служит для подмены от1казавщих ячеек основного накопителя 6, чтение осуществляется через схему «ИЛИ 23, а запись с регистра 15. При обращении к АН 7, который служит для фийса.ции кратности отказав, происходит выборка на РМКК 9 содержимого ячей.ки с признаком, равным запрашиваемому адресу. РМКК 9 настраивает работу блоков 13 и 14 при записи или чтении информации из накопителя 6 в соответствии с кратностью ошиб1КИ в его ячейке.

Предположи.м, что в одной из ячеек адресного накопителя 6, адрес которой не зафиксирован в АН 4, произощел отказ. Декодирующий блок 14 выдает сигнал «ошибка, который поступает в блок 3. По этому сигналу происходит восстановление искаженной информации (например путем чтения ее из в1нешней памяти) и запись ее в АН 4. При

ЭТОМ в признаковую часть соответствующей ячейки АН 4 записывается адрес от1казавшей ячейки и кратность отказа. В дальнейшем обращение по данному адресу приводит к чтению информации -из АН 4. TaiK устройство работает до тех пор, пока не происходит переполнения АН 4. В этом случае выдается сигнал переполнения, который поступает на блок 3. По этому сигналу происходит просмотр содержимого АН 4, и адреса тех ячеек, которые Иамеют Минималыную кратность отказов, перезаписываютоя через регистр 1 в признаковую часть АН 7, а кратность отказов записывается в инфор1мационную часть АН 7. С целью повышения быстродействия устройства перезапись адресов ячеек, имеющих минимальную кратность отказов, можно производить через схему «ИЛИ 28. После просмотра АН 4 в узле 5 фиксируются освободившиеся ячейки АН 4, таким образо м, АН 4 частично освобождается и можно записывать в него адреса неисправных ячеек по мере их об|наружвния корректирующим кодом. Для повышения вероятности обнаружения ошибки возможна периодическая, проверка адресного накопителя 6 с помощью указанных ранее способов на предмет обнаружения адресов неи10пра1В|Ных ячеек, не обнаруженных корректирующим кодом. При переполнении АН 7, информация в ячейках которого представляет собой величину мощности корректирующего хода (МКК) для отказавшей ячейки накопителя 6, узел 10 занятости и переполнения выдает сигнал в регистр 11 маски, маскирующий младший из разрядов в признаковой части АН 5. Теперь там будут не адреса отказавших ячеек адресного накопителя 6, а адреса групп ячеек (в данном случае группа состоит из двух ячеек).

При маскировании ячейка, в которой была записана .максимальная МКК среди всех ячеек АН 7 данной группы, сох|раняется, а для остальных ячеек из данной группы триггера занятости узла 10 устанавливаются в «О. Так АН 7 работает до следующего переполнения.

При новом переполнении АН 7 регистр 11 (маоки маскирует снова младший из немаскируемых разрядов (грушна теперь будет состоять из четырех ячеек), и описанный выше процесс повторяется.

Началом каждого нового цикла АН 7 служит сигнал переполнения с узла 8, а для АН 7 - сигнал с узла 10.

Второй режим работы устройства отличается тем, что в начале работы корректирующий код минимальной мощаюсти должен обнаруживать две ошибки и исправлять одну, а при дальнейшей работе мощность кода на единицу больше в соответствующем ци1)ле по сравнению с пер1вым режимам. В этом режиме не требуется восстановления информации, если в ячейке в дальнейшем произойдет еще один отказ в течение текущего цикла.

П р е д .Л1 е т изобретения

Запоминающее устройство, содержащее адресный .иа1капитель, адресные цепи которого подключены к perHicnpy адреса, а разрядные - .к блока кодирования и декодирования, ассоциативный накопитель, цадключенный к регистру адреса и регистру слова, отличающееся тем, что, с целью обеспечения возможности работы устройства при числе отказов, пре;вышаю,ще;м емкость ассоциативного накопителя, оно содержит дополнительный ассоциативный накопитель и регистр

МОЩНОСТИ Карректирующего кода, один выход которого подключен ко входам блоков кодирования и декоди1рО;вания, а вход и другой выход лодключены к дополнительному ассоциативному накопителю, информационный вход .которого подсоединен к основно1му ассоциативному нажонителю, а признаковый вход - к выходу введенной в устройство схемы «ИЛИ, один вход кото-рой подключен к выходу ,репистра адреса, а другой - к признаковому выходу основного ассоциативного нацдапителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU368647A1 |

| Оперативное запоминающее устройство с автономным контролем | 1978 |

|

SU744738A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU903990A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1805503A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU936033A1 |

| Оперативное запоминающее устройство с автономным контролем | 1983 |

|

SU1113855A2 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО„. -..,-•. ."р л С^аог^'-.---'^--:: '•^k^Vfi''-'- | 1973 |

|

SU375675A1 |

| Запоминающее устройство | 1972 |

|

SU448480A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1157575A1 |

| Запоминающее устройство | 1972 |

|

SU437127A1 |

Авторы

Даты

1973-01-01—Публикация