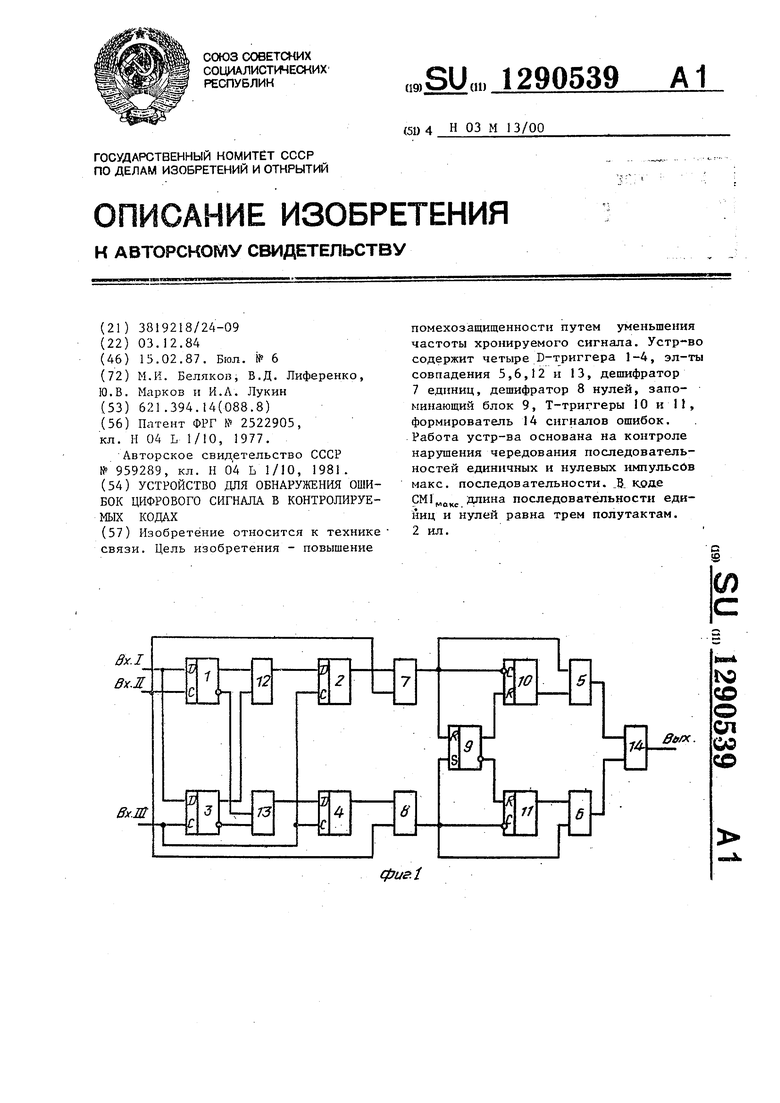

Изобретение относится к технике связи и может быть использовано для обнаружения ошибок цифрового сигнала в контролируемых кодах.

Цель,изобретения - повьшение помехозащищенности путем уменьшения частоты используемого хронируемого сигнала.

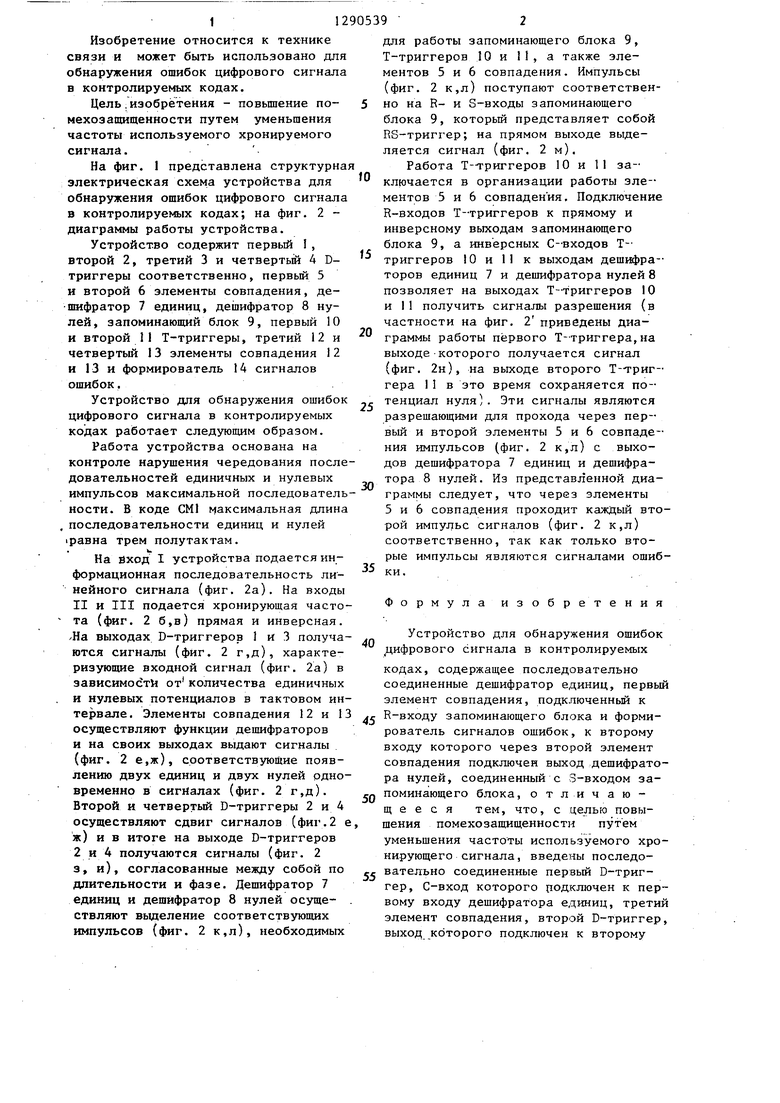

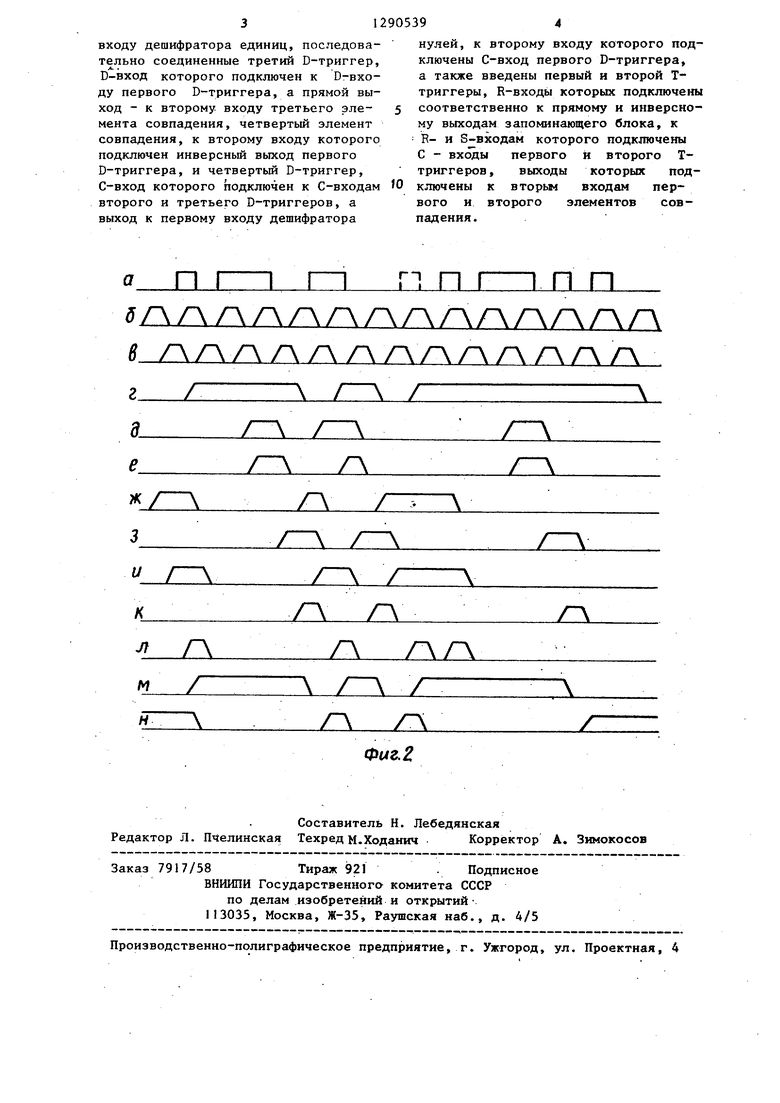

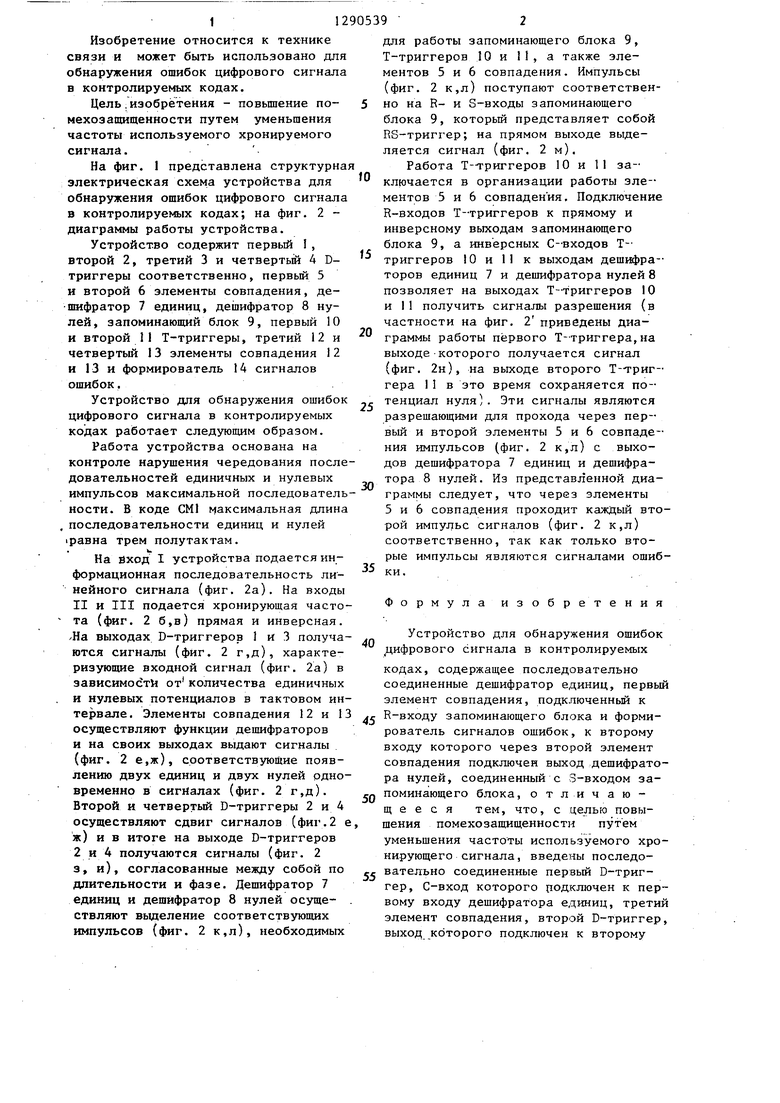

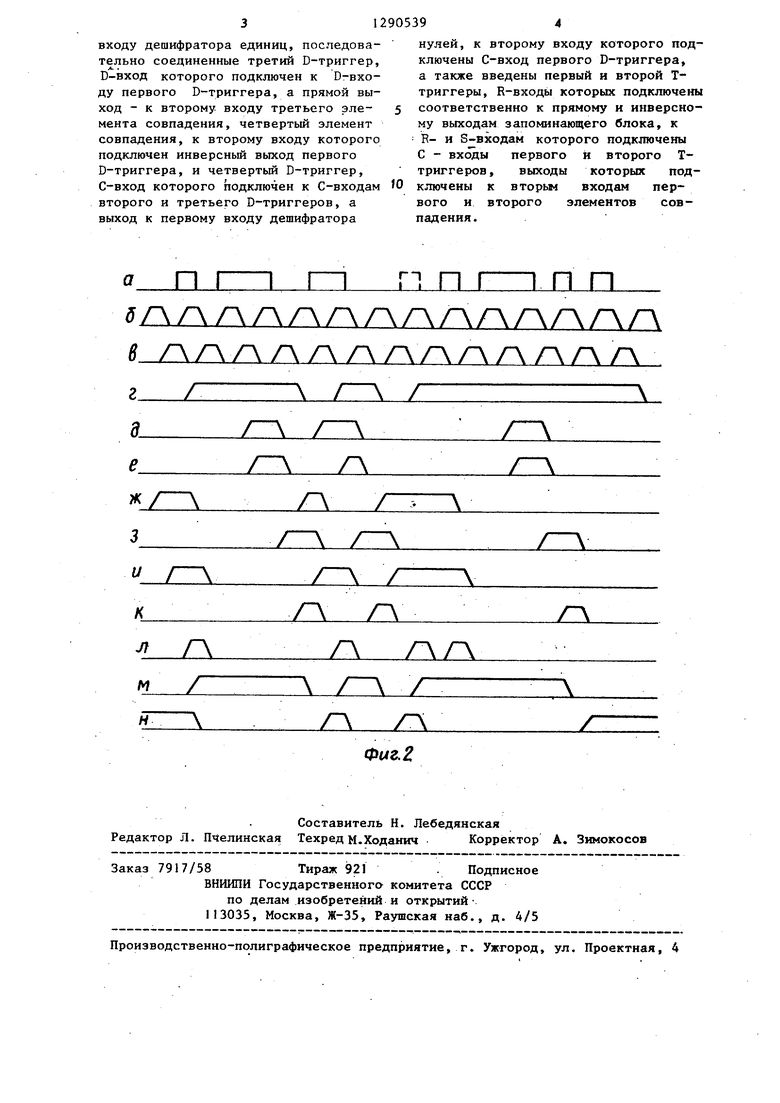

На фиг. 1 представлена структурная электрическая схема устройства для обнаружения ошибок цифрового сигнала в контролируемых кодах; на фиг. 2 - диаграммы работы устройства.

Устройство содержит первый I, второй 2, третий 3 и четвертьй 4 D- триггеры соответственно, первый 5 и второй 6 элементы совпадения, де- шифратор 7 единиц, дешифратор 8 нулей, запоминающий блок 9, первый 10 и второй П Т-триггеры, третий 12 и четвертый 13 элементы совпадения 12 и 13 и формирователь 14 сигналов ошибок.

Устройство для обнаружения ошибок цифрового сигнала в контролируемых кодах работает следующим образом. Работа устройства основана на контроле нарушения чередования последовательностей единичных и нулевых импульсов максимальной последовательности. В коде СМ1 максимальная длина последовательности единиц и нулей фавна трем полутактам.

На вход I устройства подается информационная последовательность линейного сигнала (фиг. 2а). На входы II и III подается хронирующая часто- та (фиг. 2 б,в) прямая и инверсная. /На выходах D-триггеров 1 и 3 получаются сигналы (фиг. 2 г,д), характеризующие входной сигнал (фиг. 2а) в зависимости от количества единичных и нулевых потенциалов в тактовом интервале. Элементы совпадения 12 и 13 осуществляют функции дешифраторов и на своих выходах выдают сигналы (фиг. 2 е,ж), соответствующие появлению двух единиц и двух нулей одновременно в сигналах (фиг. 2 г,д). Второй и четвертый D-триггеры 2 и 4 осуществляют сдвиг сигналов (фиг.2 е, ж) и в итоге на выходе D-триггеров 2 и Л получаются сигналы (фиг. 2 3, и), согласованные между собой по длительности и фазе. Дешифратор 7 единиц и дешифратор 8 нулей осуще- . ствляют вьщеление соответствующих импульсов (фиг. 2 к,л), необходимых

5

0

5

0

5

для работы запоминающего блока 9, Т-триггеров 10 и 11, а также элементов 5 и 6 совпадения. Импульсы (фиг. 2 к,л) поступают соответственно на R- и S-входы запоминающего блока 9, который представляет собой RS-триггер; на прямом выходе выделяется сигнал (фиг. 2м).

Работа Т-триггеров 10 и 11 заключается в организации работы элементов 5 и 6 совпадения. Подключение R-входов Т-триггеров к прямому и инверсному выходам запоминающего блока 9, а инверсных С--входов Т-триггеров 10 и 11 к выходам дешифра-- торов единиц 7 и дешифратора нулей 8 позволяет на выходах Т--триггеров 10 и 11 получить сигналы разрешения (в частности на фиг. 2 приведены диаграммы работы первого Т- Триггера, на выходе-которого получается сигнал (фиг. 2н), на выходе второго Т-триг- гера 1I в это время сохраняется потенциал нуля). Эти сигналы являются разрешающими для прохода через первый и второй элементы 5 и 6 совпадения импульсов (фиг. 2 к,л) с выходов дешифратора 7 единиц и дешифратора 8 нулей. Из представленной диаграммы следует, что через элементы 5 и 6 совпадения проходит каждый второй импульс сигналов (фиг. 2 к,л) соответственно, так как только вторые импульсы являются сигналами ошибки.

Формула изобретения

Устройство для обнаружения ошибок 11ИФРОВОГО сигнала в контролируемых

кодах, содержащее последовательно соединенные дешифратор единиц, первый элемент совпадения, подключенньй к

Н-входу запоминающего блока и формирователь сигналов ошибок, к второму входу которого через второй элемент совпадения подключен выход дешифратора нулей, соединенный с З-входом запоминающего блока, отличающееся тем, что, с целью повышения помехозащищенности путем уменьшения частоты используемого хронирующего сигнала, введены последовательно соединенные первый D-триг- гер, С-вход которого подключен к первому входу дешифратора единиц, третий элемент совпадения, второй D-триггер, выход которого подключен к второму

входу дешифратора единиц, последовательно соединенные третий D-триггер, D-вход которого подключен к D-BXO- ду первого D-триггера, а прямой выход - к второму входу третьего элемента совпадения, четвертый элемент совпадения, к второму входу которого подключен инверсный выход первого D-триггера, и четвертьй D-триггер, С-вход которого подключен к С-входам второго и третьего D-триггеров, а выход к первому входу дешифратора

а

гы

/Л/Л/ЛЛЛА /ЛАЛЛ /Л/Л/Л/Л/Л/Л

нулей, к второму входу которого подключены С-вход первого D-триггера, а также введены первый и второй Т- триггеры, R-входы которых подключены соответственно к прямому и инверсному выходам запоминающего блока, к : R и S-входам которого подключены С - входы первого и второго Т- триггеров, выходы которых подключены к вторым входам первого и вторюго элементов совпадения.

Г1 П г

тп п

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения достоверности информации | 1983 |

|

SU1092742A1 |

| Устройство для ввода информации | 1980 |

|

SU898410A1 |

| Устройство коррекции двойных ошибок с использованием кода Рида-Соломона | 1988 |

|

SU1662010A1 |

| Устройство для исправления ошибок | 1985 |

|

SU1327297A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1995 |

|

RU2101785C1 |

| Устройство для контроля псевдослучайной последовательности двоичных сигналов | 1988 |

|

SU1622950A1 |

| Устройство для измерения параметров дыхания | 1990 |

|

SU1803037A1 |

| СЕЛЕКТОР ПСЕВДОСЛУЧАЙНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ ИМПУЛЬСОВ | 1993 |

|

RU2072627C1 |

| Преобразователь кода | 1981 |

|

SU1054916A2 |

| СИСТЕМА ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1985 |

|

SU1256670A1 |

Изобретение относится к технике связи. Цель изобретения - повышение помехозащищенности путем уменьшения частоты хронируемого сигнала, Устр-во содержит четыре D-триггера 1-4, эл-ты совпадения 5,6,12 и 13, дешифратор 7 единиц, дешифратор 8 нулей, запоминающий блок 9, Т-триггеры 10 и 1I, формирователь 14 сигналов ошибок, Работа устр-ва основана на контроле нарушения чередования последовательностей единичных и нулевых импульсйв макс, последовательности. В. КОДе Р макс длина последовательности единиц и нулей равна трем полутактам, 2 ил. ffif/X. ГчЭ О сл со QD

/-

г /л

JI/л

/л /ЛАЛ

м

jL

н

Л

г /

Составитель Н. Лебедянская Редактор Л. Пчелинская Техред м.Ходаиич Корректор А. Зимокосов

Заказ 7917/58 Тираж 921 . Подписное ВНИИПИ Государственного комитета СССР

по делам .изобретений и открытий- I13035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

г

/

Фиг.2

| СПОСОБ ИЗВЛЕЧЕНИЯ РЕДКОЗЕМЕЛЬНЫХ ЭЛЕМЕНТОВ ИЗ ЖИДКИХ СПЛАВОВ С ЦИНКОМ | 2012 |

|

RU2522905C1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для обнаружения ошибок цифрового сигнала в контролируемых кодах | 1981 |

|

SU959289A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-02-15—Публикация

1984-12-03—Подача