to

4 О ГО

(puff

1

Изобретение относится к устройствам вычислительной техники и может быть использовано для автоматизации научных и прикладных исследований.

Цель изобретения - повышение быстродействия вь числительной системы аугем уменьшения времени на подключение каналов к вычислительным блокам.

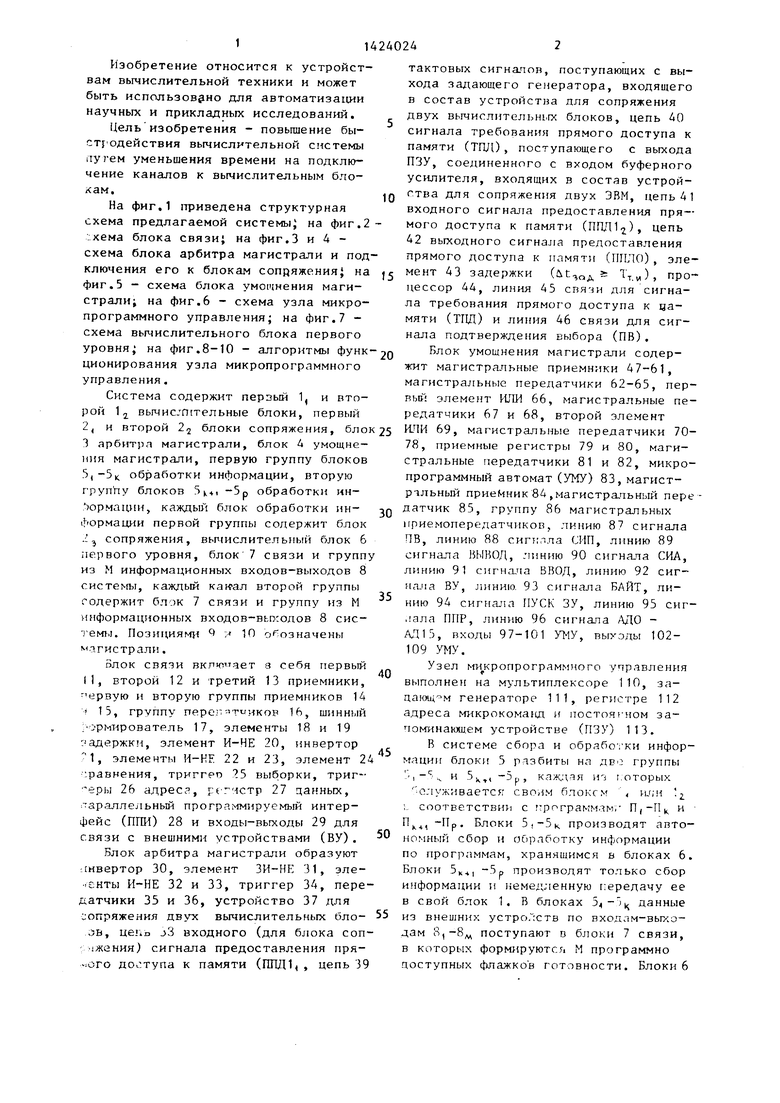

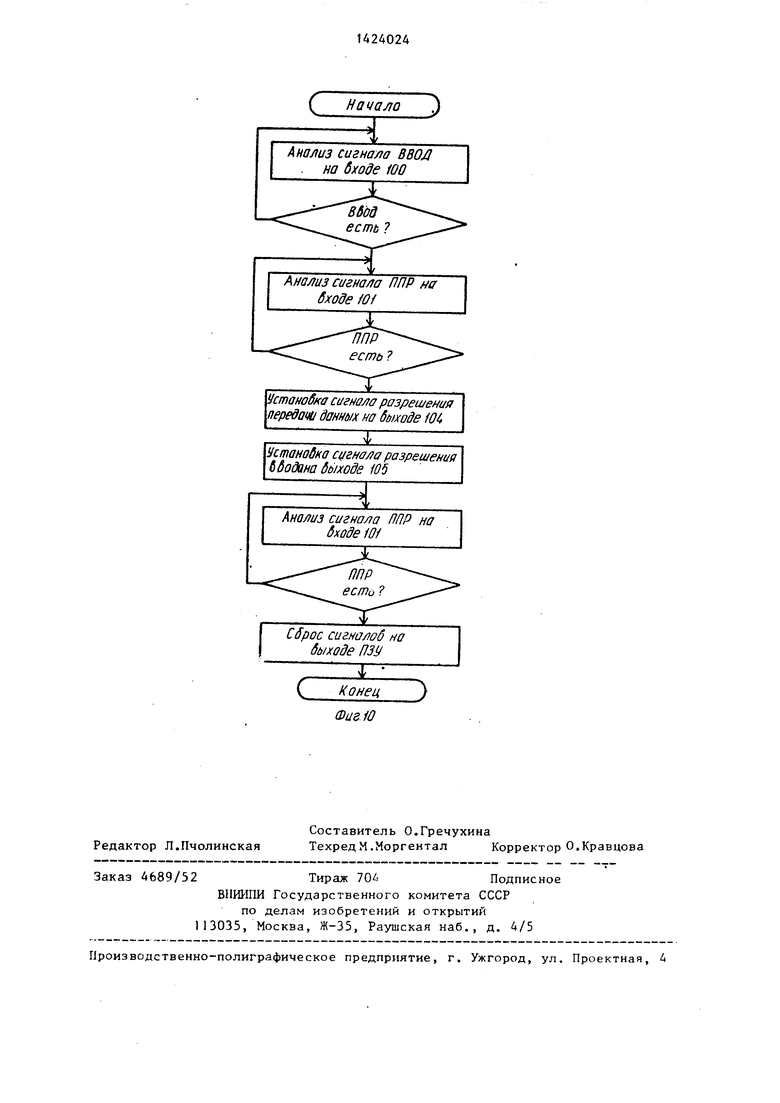

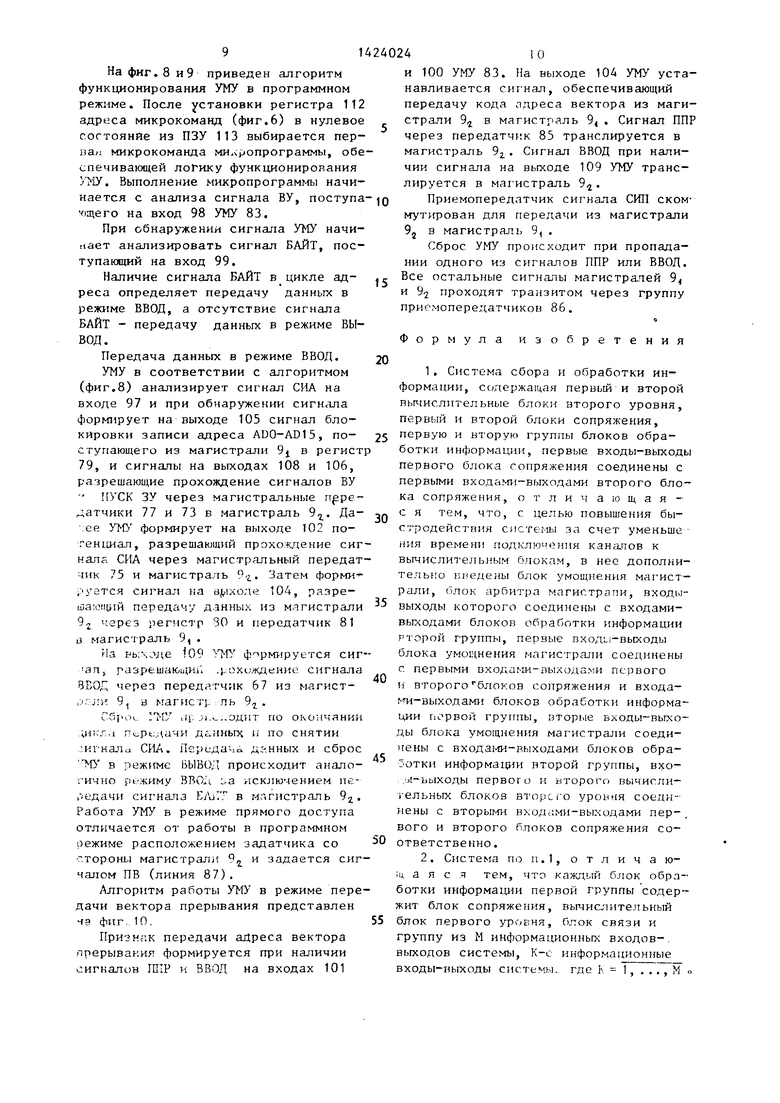

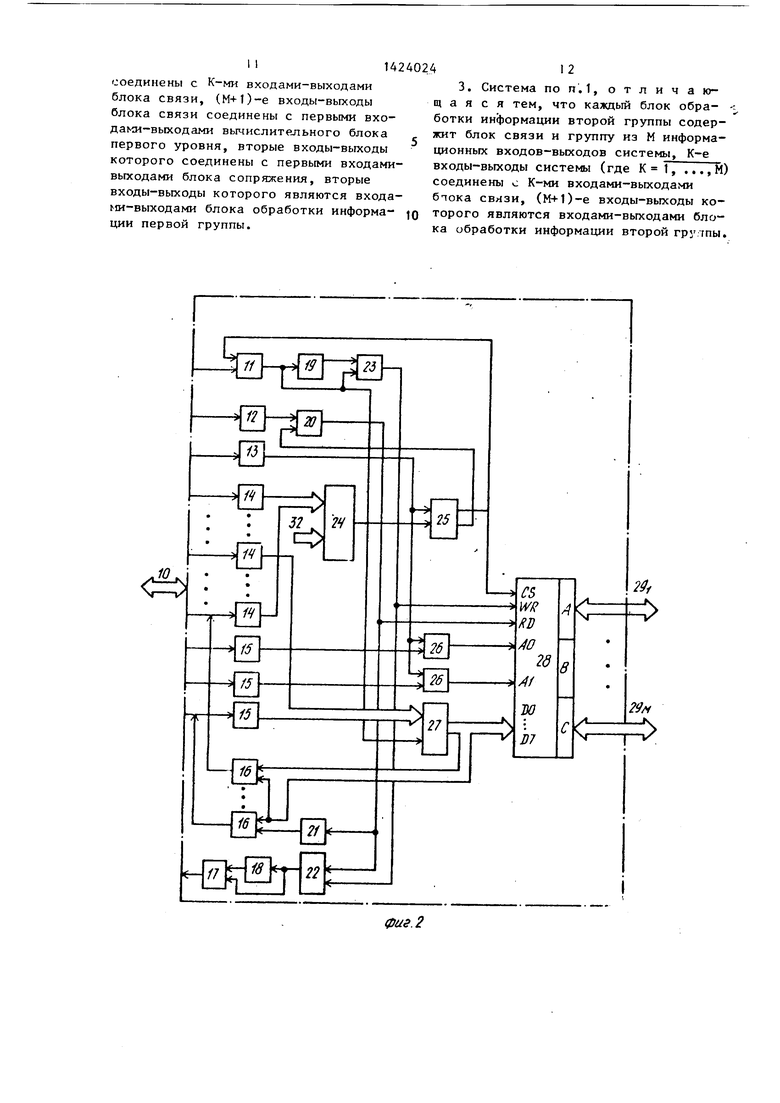

На фиг,1 приведена структурная схема предлагаемой системы; на фиг.хема блока связи; на фиг.З и 4 - схема блока арбитра магистрали и поключения его к блокам сопряжения} н фиг.З - схема блока умопшения магистрали; на фиг.6 - схема узла микропрограммного управления; на фиг.7 - схема вычислительного блока первого уровня; на фиг.8-10 - алгоритмы фун ционирования узла микропрограммного управления.

Система содержит перзый 1, и вто

рой 12, вычис- Штельные блоки, первый

0

мент 0

тактовых сигналов, поступающих с выхода задающего генератора, входящего в состав устройства для сопряжения двух вычислительнь.гх блоков, цепь 40 сигнала требования прямого доступа к памяти (ТГиО , поступающего с выхода ПЗУ, соединенного с входом буферного усилителя, входящих в состав устройства для сопряжения двух ЭВМ, цепь 41 входного сигнала предоставления прямого доступа к памяти (ПГЦЦ), цепь 42 выходного сигнала предоставления прямого доступа к памяти (ППЛО), эле- 43 задержки ( s 1.}, процессор 44, линия 45 спячи для сигнала требования прямого доступа к ца- мяти (ТГЩ) и линия 46 связи для сигнала подтверждения выбора (ПВ),

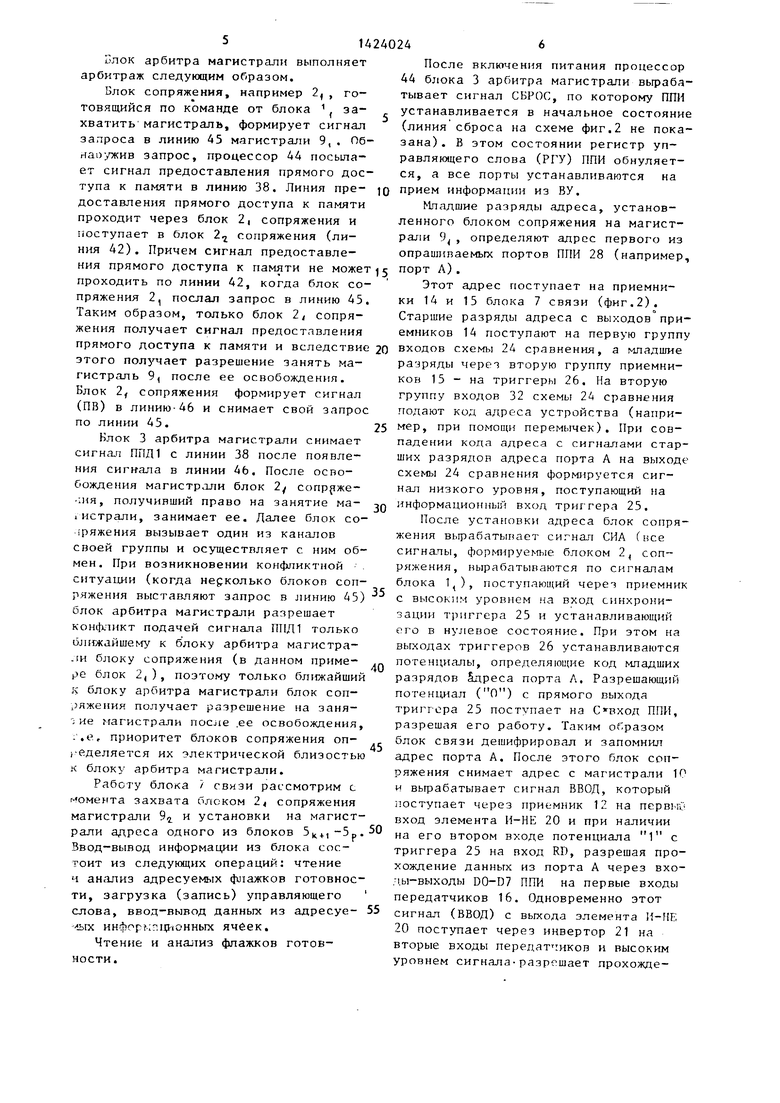

Блок умощнения магистрали содержит магистральные приемники 47-61, магистральные передатчики 62-65, первый элемент Шта 66, магистральные передатчики 67 и 68, второй элемент

| название | год | авторы | номер документа |

|---|---|---|---|

| Система обработки информации | 1990 |

|

SU1795468A1 |

| Устройство индикации состояния ЭВМ | 1989 |

|

SU1667067A1 |

| Устройство для сопряжения ЭВМ с М внешними устройствами | 1986 |

|

SU1374232A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1988 |

|

SU1515167A1 |

| Отказоустойчивая вычислительная система | 1990 |

|

SU1798800A1 |

| Многоканальная система управления распределением ресурсов в вычислительном комплексе | 1987 |

|

SU1432580A1 |

| Устройство для сопряжения ЭВМ с разноскоростными группами внешних устройств | 1990 |

|

SU1837302A1 |

| Устройство для сопряжения двух ЭВМ | 1986 |

|

SU1363230A1 |

| Устройство для сопряжения двух ЭВМ | 1987 |

|

SU1499360A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

Изобретение относится к области вычислительной техники и может быть использовано для автоматизации научных и прикладных исследований. Цель изобретения - повышение быстродействия вычислительной системы за счет уменьшения времени на подключение каналов к вычислительным блокам - достигается тем, что в систему, содержащую первый и «торой вычислительные блоки 1 второго уровня, первьш и второй блоки 2 сопряжения, первую и вторую группы блоков 5 обработки информации, дополнительно введены блок 4 умощнения магистрали и блок 3 арбитра магистрали, причем каждьаЧ блок 5 обработки информации первой группы содержит блок сопряжения, вычислительной блок первого уровня, блок связи и группу информационных входов-выходов системы, каждый блок 5 обработки информации второй группы содержит блок связи и группу информационных входов-выходов системы. 23.п, ф-лы, 10 кл. S (Л

2( и второй 2,2 блоки сопряжения, блок 25 69, магистральные передатчики 70

3 арбитра магистрали, блок 4 умощнения магистрали, первую группу блоков 3, -5к; обработки информации, вторую группу блоков 5(41 -5р обработки ин- юрмации, каждый блок обработки ин- формации первой группы содержит блок .: сопряжения, вьршслительный блок 6 первого уровня, блок 7 связи и группу из М информационных входов-выходов 8 системы, каждый какал второй группы годержит блок 7 связи и группу из М информационных входов-вьп одов 8 сис- reMt.i. Позициям}1 и 10 о ;означены магистрали.

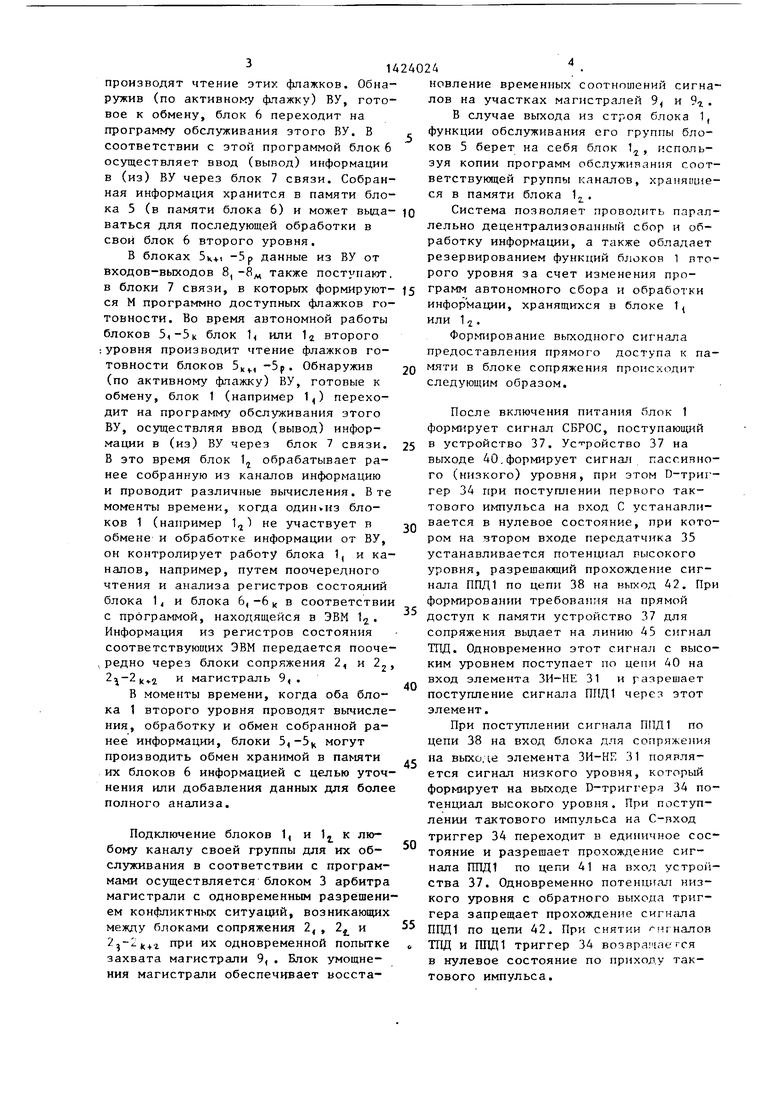

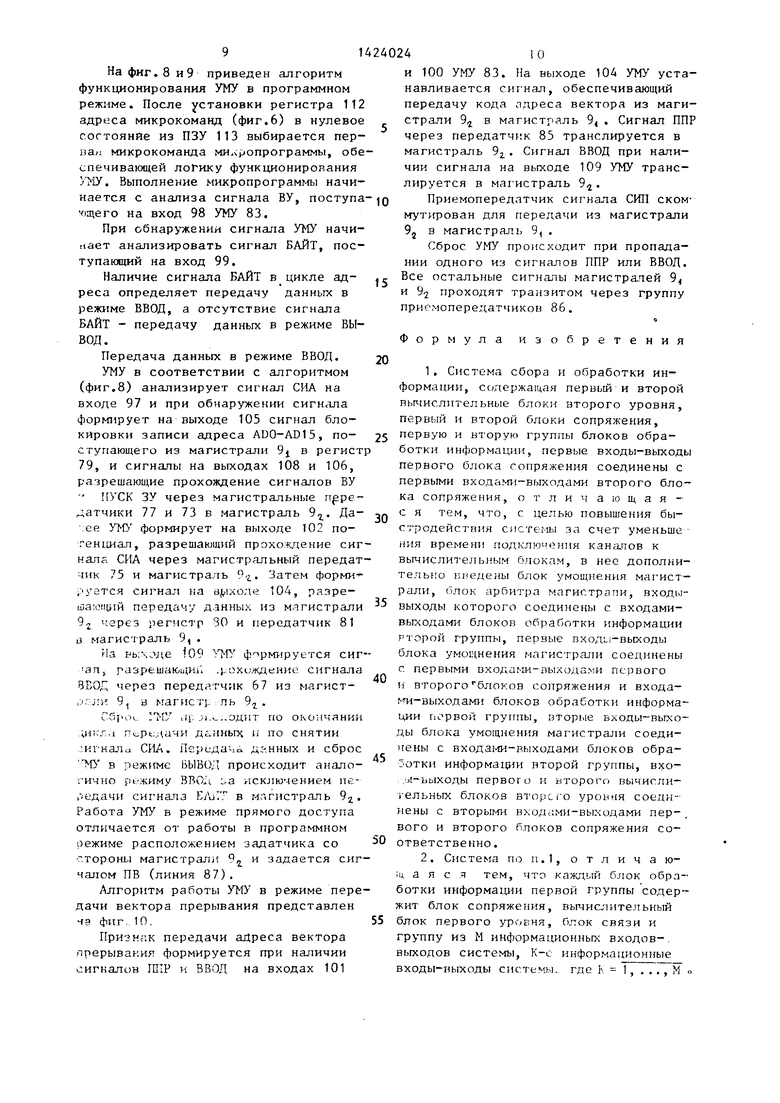

БЛОК связи включает з себя первый М, второй 12 и третий 13 приемники, ервую и вторую группы приемников 14 15, группу перС : тчикор 16, шинный V OpMHpoBaTenb 17, элементы 18 и 19 задержки, элемент И-НЕ 20, инвертор : 1, элементы И-НЕ 22 и 23, элемент 24 сравнения, триггеп 25 выборки, триг- 26 адреса, ре-чстр 27 цанных, ; ;ар.аллельный программируемый интерфейс (ППИ) 28 и входы-выходы 29 для связи с внешними устройствами (ВУ). Блок арбитра магистрали образуют гливертор 30, элемент ЗИ-НЕ 31, эле- .,нты И-НЕ 32 и 33, триггер 34, передатчики 35 и 36, устройство 37 для сопряжения двух вычислительных бло- ов, цепа j3 входного (для блока соп- чжения) сигнала предоставления пря- ..ого доступа к памяти (ППД1, , цепь 39

5

0

Q

5

5

0

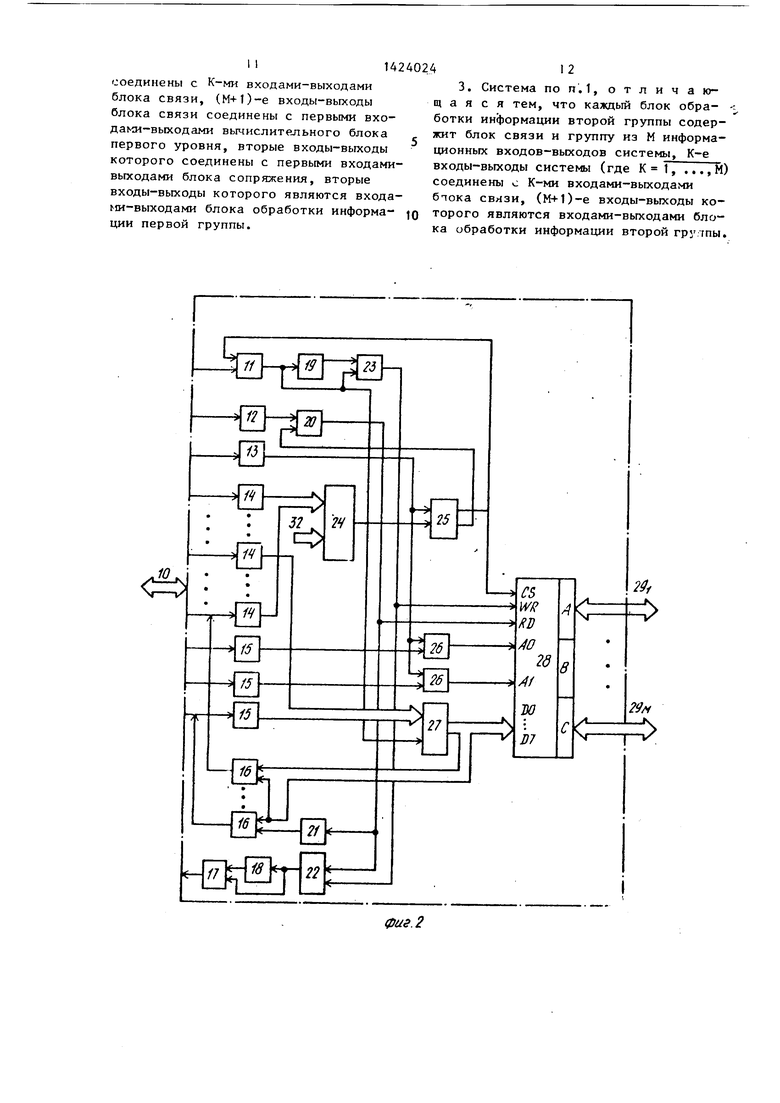

78, приемные регистры 79 и 80, магистральные передатчики 81 и 82, микропрограммный автомат(УМУ) 83, магист- рчльный приемник 84 , магистральный передатчик 85, группу 86 магистральных 1гриемопередатчиков, линию 87 сигнала ПВ, линию 88 СИП, линию 89 сигнала ВЫВОД, . тинию 90 сигнала СИА, линию 91 сигна.па ВВОД, линию 92 сиг- ня-иа ВУ, линию. 93 сигнала ВАЙТ, линию 94 сигнала ПУСК ЗУ, линию 95 сиг- ,ала ПОР, линию 96 сигнала АДО - АД 15, входы 97-101 Т-1У, выходы 102- 109 T ly.

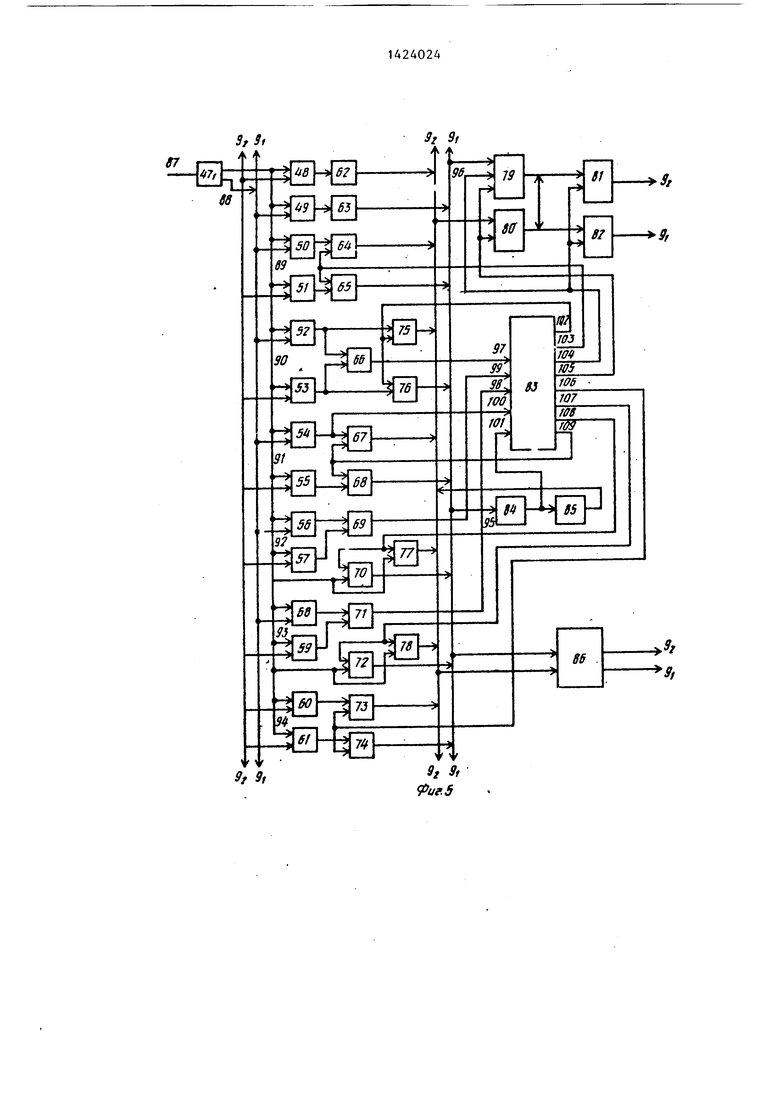

Узел ми кропрограммного управления выполнен на мультиплексоре 110, за- генераторе 111, регистре 112 адреса микрокоманд и постоясном запоминающем устройстве (ПЗУ) 113.

В системе сбора и обработки информации блоки 5 разбиты на ДВ Э группы i-S, и 5,, 5р, из г.оторых

с:1уживаетс5г своим блокг.м , .2 I соответстви 1 с гтр о граммам, П,-Пц и Пр Блоки 5.-5К производят автономный сбор и обработку информации по программам, храняш.имся в блоках 6. Блоки 5кч1 производят только сбор информации и немедленную г;ередачу ее в свой блок 1. В блоках данные из внешних устро. :ств по Бходам-выхо- дам 1(-В поступают в блоки 7 связи, в которых формируются М программно доступных флажков готовности. Блоки 6

производят чтение этих флажков. Обнаружив (по активному флажку) ВУ, готовое к обмену, блок 6 переходит на программу обслуживания этого ВУ. В , соответствии с этой программой блок 6 осуществляет ввод (вывод) информации в (из) ВУ через блок 7 связи. Собранная информация хранится в памяти блока 5 (в памяти блока 6) и может вьиа- Q ваться для последующей обработки в свой блок 6 второго уровня.

В блоках 5к, -5р данные из ВУ от входов-выходов 8, -8д, также поступают.

новление временных соотношений сигна лов на участках магистралей 9 и 9

В случае выхода из строя блока 1, функции обслуживания его группы блоков 5 берет на себя блок 1, используя копии программ обслуживания соот ветствующей группы каналов, хранящие ся в памяти блока 1.

Система позволяет проводить парал лельно децентрализованный сбор и обработку информации, а также обладает резервированием функций блоков 1 вто рого уровня за счет изменения пров блоки 7 связи, в которых формируют- 15 грамм автономного сбора и обработки ся М программно доступных флажков готовности. Во время автономной работы блоков 5,-5 к блок или Ij второго .уровня производит чтение флажков гоинформации, хранящихся в блоке 1 или 12.

Фор№5рование выходного сигнала предоставления прямого доступа к па мяти в блоке сопряжения происх(1дит следующим образом.

товности блоков 5к, -5р. Обнаружив (по активному флажку) ВУ, готовые к обмену, блок 1 (например 1) переходит на программу обслуживания этого ВУ, осуществляя ввод (вывод) информации в (из) ВУ через блок 7 связи. В это время блок 1 обрабатывает ранее собранную из каналов информацию и проводит различные вычисления. В те моменты времени, когда блоков 1 (например 1) не участвует в обмене и обработке информации от ВУ, он контролирует работу блока 1, и каналов, например, путем поочередного чтения и анализа регистров состоялий блока 1, и блока 6,-6 в соответствии с пр6гра чмой, находящейся в ЭВМ Ij . Информация из регистров состояния соответствующих ЭВМ передается пооче- ,редно через блоки сопряжения 2, и 2, ,.2 и магистраль 9,.

В моменты времени, когда оба блока 1 второго уровня проводят вычисления, обработку и обмен собранной ранее информации, блоки 5,-5 могут производить обмен хранимой в памяти их блоков 6 информацией с целью уточнения или добавления данных для более полного анализа.

Подключение блоков 1, и Ij к любому каналу своей группы для их обслуживания в соответствии с программами осуществляется блоком 3 арбитра магистрали с одновременным разрешением конфликтных ситуаций, возникающих между блоками сопряжения 2, , 2, и пр одновременной попытке захвата магистрали 9,. Блок умощне- ния магистрали обеспечивает восстановление временных соотношений сигналов на участках магистралей 9 и 9.

В случае выхода из строя блока 1, функции обслуживания его группы блоков 5 берет на себя блок 1, используя копии программ обслуживания соответствующей группы каналов, хранящиеся в памяти блока 1.

Система позволяет проводить параллельно децентрализованный сбор и обработку информации, а также обладает резервированием функций блоков 1 второго уровня за счет изменения программ автономного сбора и обработки

информации, хранящихся в блоке 1 или 12.

Фор№5рование выходного сигнала предоставления прямого доступа к памяти в блоке сопряжения происх(1дит следующим образом.

После включения питания блок 1 формирует сигнал СБРОС, поступаюищй в устройство 37. Ус ройство 37 на выходе 40.формирует сигнал пассивного (низкого) уровня, при этом В-трИ1 гер 34 при поступлении первого тактового импульса на вход С устанавливается в нулевое состояние, при котором на втором входе передатчика 35 устанавливается потенциал высокого уровня, разрешающий прохождение сигнала ППД1 по цепи 38 на выход 42. При формировании требования на прямой доступ к памяти устройство 37 для сопряжения выдает на линию 45 сигнал ТПД. Одновременно этот сигнал с высоким уровнем поступает по цепи 40 на вход элемента ЗИ-НЕ 31 и разрешает поступление сигнала ППД1 через этот элемент.

При поступлении сигнала ППД1 по цепи 38 на вход блока для сопряжения на выхо.че элемента ЗИ-НГ 31 появляется сигнал низкого уровня, который формирует на выходе В-трип-ера 34 по- тенц11ал высокого уровня. При поступлении тактового импульса на С-вход триггер 34 переходит в единичное состояние и разрешает прохождение сигнала ППД1 по цепи 41 на вход устройства 37. Одновременно потенциал низкого уровня с обратного выхода триггера запрещает прохождение сигнала ППД1 по цепи 42. При снятии нгналов ТПД и П1Щ1 триггер 34 возвра-цается в нулевое состояние по приходу тактового импульса.

Блок арбитра магистрали выполняет арбитраж следующим образом.

Блок сопряжения, например 2,, готовящийся по команде от блока захватить магистраль, формирует сигнал запроса в линию 45 магистрали 9,. Пб- наоужив запрос, процессор АА посылает сигнал предоставления прямого досКлок 3 арбитра магистрали снимает сигнал ППД1 с линии 38 после появления сигнала в линии 46. После освобождения магистрали блок 2 сопрржетупа к памяти в линию 38. Линия пре- JQ прием информации из ВУ. доставления прямого доступа к памяти Младшие разряды адреса, установ- проходит через блок 2, сопряжения и ленного блоком сопряжения на магист- Г оступает в блок 2 сопряжения (ли- рали 9 , определяют адрес первого из ния 42). Причем сигнал предоставле- опрашиваемых портов ППИ 28 (например, ния прямого доступа к памяти не может 5 порт Л).

проходить по линии 42, когда блок со- Этот адрес поступает на приемни- пряжения 2, послал запрос в линию 45. ки 14 и 15 блока 7 связи (фиг.2). Таким образом, только блок 2, сопря- Старшие разряды адреса с выходов при- жения получает сигнал предоставления емников 14 поступают на первую группу прямого доступа к памяти и вследствие 20 входов схемы 24 сравнения, а младшие этого получает разрешение занять ма- разряды через вторую группу приемни- гистраль 9( после ее освобождения. ков 15 - на триггерь 26. На вторую Блок 2, сопряжения формирует сигнал группу входов 32 схемы 24 сравнения (ПВ) в линию-46 и снимает свой запрос подают код адреса устройства (напри- по линии 45.25 при помощи перемычек). При совпадении кода адреса с сигналами старших разрядов адреса порта А на выходе схемы 24 сравнения формируется сигнал низкого уровня, поступающий на 1ИЯ, получивший право на занятие ма- -JQ информационный вход триггера 25. 1истрали, занимает ее. Далее блок со- После установки адреса блок сопря- фяжения вызывает один из каналов своей группы и осуществляет с ним обмен. При возникновении конфликтной ситуации (когда несколько блоков сопряжения выставляют запрос в линию 45) блок арбитра магистрали разрешает кон(}х 1икт подачей сигнала ППД1 только ближайшему к блоку арбитра магистрали блоку сопряжения (в данном примере блок 2(), поэтому только ближайший к блоку арбитра магистрали блок сопряжения получает разрешение на занятие магистрали после .ее освобождения, ;.е, приоритет блоков сопряжения оп- 1 еделяется их электрической близостью к блоку арбитра магистрали.

Работу блока / связи рассмотрим с r-fOMeHTa захвата блоком 2 сопряжения магистрали 9 и установки на магистрали адреса одного из блоков 5,-5р.50 Ввод-вывод информации из блока состоит из следующих операций: чтение 1 анализ адресуемых флажков готовности, загрузка (запись) управляющего слова, ввод-вывод данных из адресуе- 55 сигнал (ВВОД) с выхода элемента И-НЕ -ых инфг ркг,ц1 1онных ячеек.20 поступает через инвертор 21 на

Чтение и анализ флажков готовности.

40

45

жения вырабатывает сигнал СИЛ (все сигналы, формируемые блоком 2 сопряжения, вырабатываются по сигналам блока 1,), поступающий через приемник с высоким уровнем на вход синхронизации триггера 25 и устанавливающий его в нулевое состояние. При этом на выходах триггеров 26 устанавливаются потенциалы, определяющие код младших разрядов 5дреса порта Л. Разрешающий потенилал (О) с прямого выхода триггера 25 поступает на С вход ППИ, разрешая его работу. Таким образом блок связи дешифрировал и запомнил адрес порта А. После этого блок сопряжения снимает адрес с магистрали 10 и вьфабатывает сигнал ВВОД, который 1юступает через приемник 12 на вход элемента И-НР 20 и при наличии на его втором входе потенциала 1 с триггера 25 на вход RD, разрешая прохождение данных из порта А через вхо- ,-1,ы-выходы DO-D7 ППИ на первые входы передатчиков 16. Одновременно этот

вторые входы передатчиков и высоким уровнем сигнала-разр шает прохождеПосле включения питания процессор 44 блока 3 арбитра магистрали вьфабя- тывает сигнал СБРОС, по которому ППИ устанавливается в начальное состояние (линия сброса на схеме фиг.2 не показана) . В этом состоянии регистр управляющего слова (РГУ) ППИ обнуляется, а все порты устанавливаются на

падении кода адреса с сигналами старших разрядов адреса порта А на выходе схемы 24 сравнения формируется сигнал низкого уровня, поступающий на -JQ информационный вход триггера 25. После установки адреса блок сопря-

0 5 сигнал (ВВОД) с выхода элемента И-НЕ 20 поступает через инвертор 21 на

0

5

жения вырабатывает сигнал СИЛ (все сигналы, формируемые блоком 2 сопряжения, вырабатываются по сигналам блока 1,), поступающий через приемник с высоким уровнем на вход синхронизации триггера 25 и устанавливающий его в нулевое состояние. При этом на выходах триггеров 26 устанавливаются потенциалы, определяющие код младших разрядов 5дреса порта Л. Разрешающий потенилал (О) с прямого выхода триггера 25 поступает на С вход ППИ, разрешая его работу. Таким образом блок связи дешифрировал и запомнил адрес порта А. После этого блок сопряжения снимает адрес с магистрали 10 и вьфабатывает сигнал ВВОД, который 1юступает через приемник 12 на вход элемента И-НР 20 и при наличии на его втором входе потенциала 1 с триггера 25 на вход RD, разрешая прохождение данных из порта А через вхо- ,-1,ы-выходы DO-D7 ППИ на первые входы передатчиков 16. Одновременно этот

вторые входы передатчиков и высоким уровнем сигнала-разр шает прохождение данных через передатчики 16 на магистраль 10, а также обеспечивает формирование сигнала ответа (СИП) при прохождении его через элемент И-НЕ 22, элемент 18 задержки и шинный формирователь 17. Блок сопряжения принимает сигнал СИП, принимает данные во внутренний регистр и снимает сигнал ВВОД. По снятии сигнала ВВОД на выходе шинного формирователя 17 снимается сигнал СИП, завершая операцию передачи данных. Блок сопряжения снимает сигнал СИЛ, завершая цикл ВВОД. Далее блок 1, анализирует принятые данные на наличие сигналов активности флажков готовности.

При отсутствии сигналов готовности в данных порта А блок 1, аналогичным

образом производит чтение данных еле- }0 порта А (в (из) обслуживаемого ВУ)

дующего порта канала. При наличии в слове данных порта А бита готовности от ВУ ЭВМ переходит на программу обслуживания этого ВУ. Программа обслуживания ВУ включает загрузку управ- ляющего слова, определяющего режим работы с ВУ (ввод или вывод информации) и ввод (вывод) информации в (из ВУ.

Загрузка управляющего слова в ППИ (цикл-ЭВМ ВЫВОД).

Блок 2 сопряжения в адресной части цикла ВЫВОД устанавливает на магистрали 92 адрес регистра управлявде- го слова ППИ и сигнал СИА.

Аналогично блок связи дешифрует и запоминает адрес. После этого блок 2 , сопряжения снимает адрес и помещает данные на магистраль 10. Данные являются управляющим словом, по коду которого ППИ будет запрограммирован для работы в нулевом режиме, а порт А установлен в режим ввода информации (для примера). Затем блок сопряжения вьфабатывает сигнал ВЫВОД, который поступает на первый вход приемника 11, на втором входе которого находится разрешающий потенциал с триггера 25. С выхода приемника 11 высокий уровень сигнала поступает на вход выбора режима буферного регистра 27, разрешая передачу данных с выходов приемников 14 и 15 (связи на фиг.2 не показаны) через буферный регистр 27 на входы DO-D7 ППИ.

Одновременно сигнал ВЫВОД с выхо- да приемника 11 через элемент.19 задержки и элемент И-НЕ 23 портупает низким уровнем на вход ,WR ППИ, осу-

j

0248

ществляя запись данных в РГУ. Таким образом в РГУ находится код, определяющий режим работы и направление передачи информации через порт А, В то же время сигнал ВЫВОД обеспечивает формирование сигнала СШ, поступая с выхода элемента И-НЕ 23 через элемент И-НЕ 22 и элемент 18 задержки на входы шинного формирователя 17. Блок сопряжения принимает сигнстл СИП и снимает сигнал ВЫВОД. По снятии сигнала ВЫВОД на выходе шинного формирователя 17 снимается сигнал СИП, завершая операцию приема данных. Блок сопряжения снимает сигнал CtL, завершая цикл ВЫВОД.

Ввод-вывод информации.

Ввод (вывод) информации в (из)

10

0

5

5

5

0

5

0

производит блок 1, через блок 2 в цикле ВВОД или ВЫВОД соответственно и аналогичен операциям с установкой на магистрали 9 адреса порта А.

Обмен информацией по магистрали 10 между блоками 6 первого уровня и блоком 7 связи аналогичен опислипому.

Блок умощнения магистрали (фиг.5) обеспечивает прохождение из магистрали 9( в магистраль 9 и обратно сигналов общей с восстановлением временных соотношений. Блок работает в трех режимах: nporpaNfMHOM, прямого доступа, передачи вектора прерывания.

В программном режиме блок осуи;ест- вляет передачу информации под управлением задатчика, рлсполсженпого со стороны магистрали 9, . Признак работы в программном режиме - отсутстпие сигналов ПВ (линия 87) и ППР (г;и- ния 95).

При работе в программном рржиме магистральные приемники 60, 58, 54, 50, 52 и 56 сигналов ПУСК ЗУ, B/vl iT, ВВОД, 1)ЫВОД, СИА и ВУ включены гля приема со стороны магистрали ч,, а магистральный приемник 48 (для сигнала СИП) - со стороны магистрали 9. Передатчики. 81 и 82 скомм тиропдны для трансляции из 9 и 9.

Передача информации через умощни- тель магистрали происходит следующим образом.

Адрес обращения из магистра.пи 9 поступает через приемный регистр 79 и передатчик 82 в магистра.-г1 92. Сигналы ВУ и БАЙТ с магистрат 9, через приемиики 56 и 58, элементы ИЛИ 69 и 71 поступают на вход 8:i.

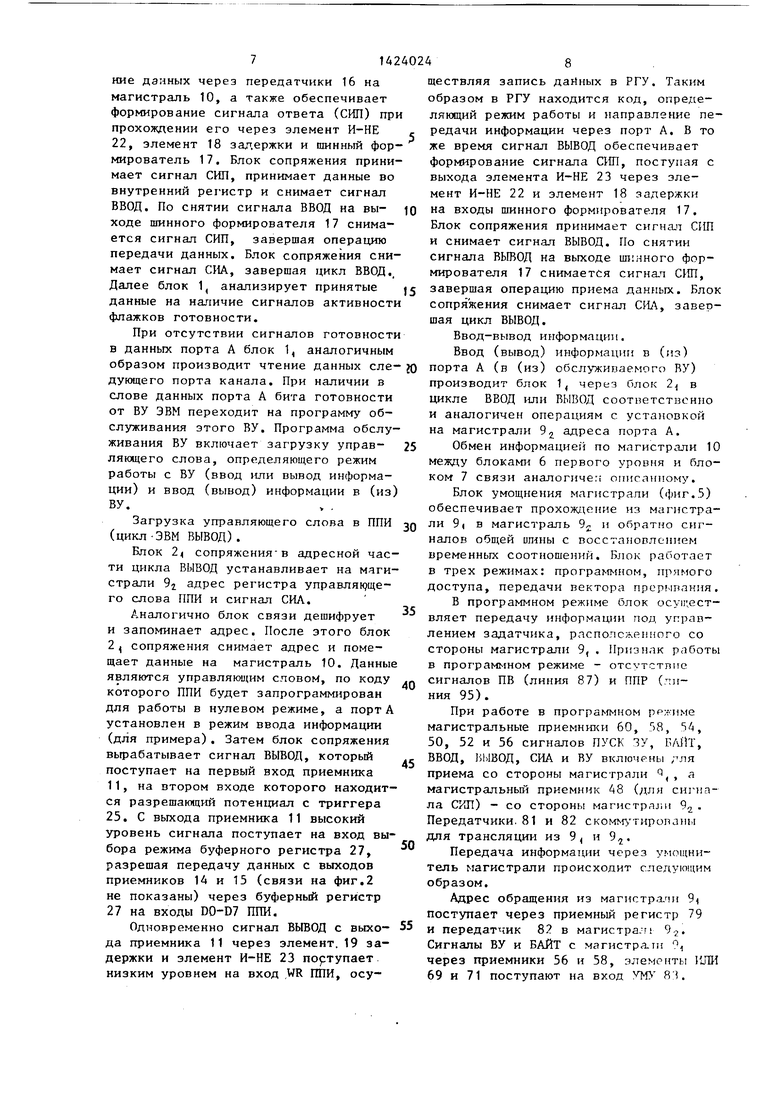

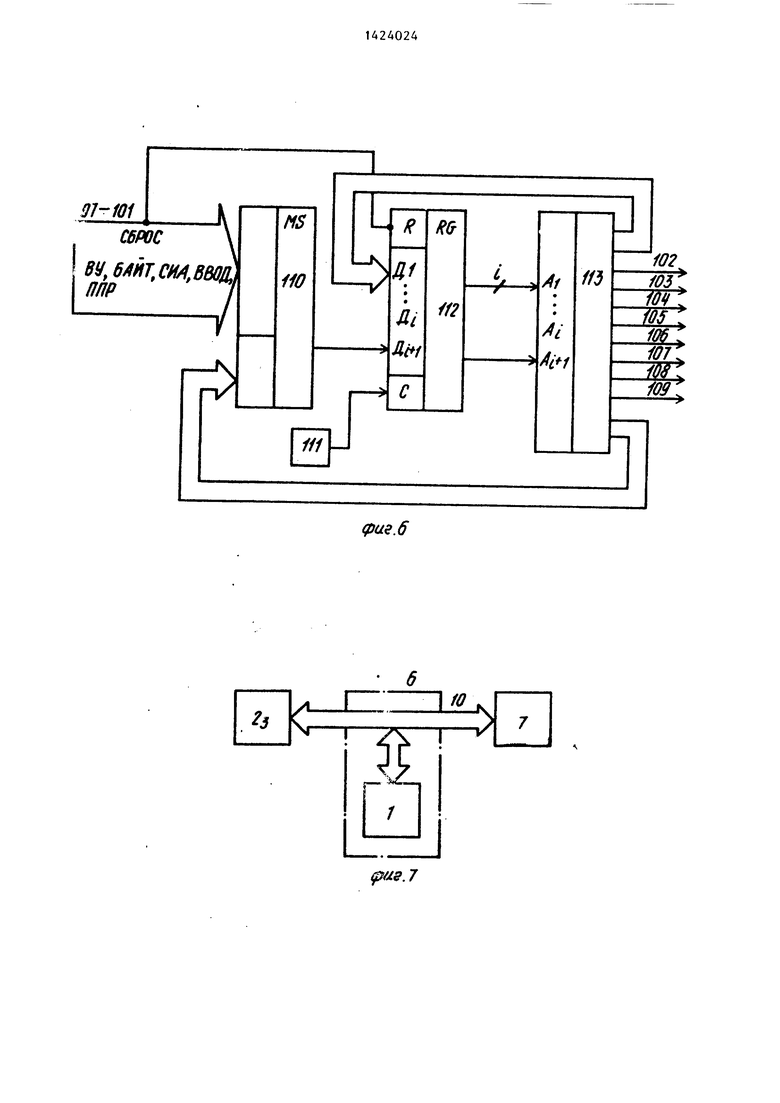

На фиг,8 и9 приведен алгоритм функционирования УМУ в программном режиме. После установки регистра 112 адреса микрокоманд (фиг,6) в нулевое состояние из ПЗУ 113 выбирается пер- ввд микрокоманда микропрограммы, обеспечивающей логику функционирования yi iy. Выполнение микропрограммы начинается с анализа сигнала ВУ, поступа на вход 98 УМУ 83.

При обнаружении сигнала УМУ начи- пает анализировать сигнал БАЙТ, поступающий на вход 99,

Наличие сигнала БАЙТ в цикле адреса определяет передачу данных в режиме ВВОД, а отсутствие сигнала БАЙТ - передачу данных в режиме ВЫВОД,

Передача данных в режиме ВВОД,

УМУ в соответствии с алгоритмом (фиг,8) анализирует сигнал СИЛ на входе 97 и при обнаружении сигнала формирует на выходе 105 сигнал блокировки записи адреса ADO-AD15, поступающего из магистрали 9 в регист 79, и сигналы на выходах 108 и 106, разрешающие прохождение сигналов ВУ

УСК ЗУ через магистральные датчики 77 и 73 в магистраль 9. Да- :ее формирует на выходе 102 по- гетцлал, разрешающий прохо.адение сигнала СНА через магистральный передатчик 75 и магистраль 9.. Затем форми ;;1уется сигнал на si ixoae 104, разре- iijaioii;im передачу данных из магистрали 92 через регистр 30 и передатчик 81 о магистраль 9,,

fla рь:ходе f09 тЖ формируется сиг ап. разрешаюи4Н1 , .{- - - ВД ние сигнала ВВОД через передатчик 67 из магист

9, в магистр:ль 9

г C6poL. 7- У lit. л....одит по окончании

Ли;-г-:1 nt,pt:.;(,a4H li по снятии ,;игнала CH/v, Передач дйнных и сброс в режиме ВЫВОД происходит аналогично i:l.-жимy ВВОд исключением пе- .- Сдачи сигнала K/uIT в магистраль 9. Работа УМУ в режиме прямого доступа отличается от работы в программном режиме расположением задатчика со -птороны магистрали 9 и задается сиг- чалом ПВ (линия 87).

Алгоритм работы УМУ в режиме передачи вектора прерывания представлен ча фиГ:, to.

Признак передачи адреса вектора . Трерывакия формируется при наличии сигналов ГШР и ВВОД на входах 101

5

и 100 УМУ 83, На выходе 104 УМУ устанавливается сигнал, обеспечивающий передачу кода адреса вектора из магистрали 9 в магистраль 9, , Сигнал ППР через передатчик 85 транслируется в магистраль 9. Сигнал ВВОД при наличии сигнала на выходе 109 УМУ транслируется в мах истраль 9 Q Приемопередатчик сигнала СИП ском- мутирован для передачи из магистрали 9j в магистраль 9 .

Сброс происходит при пропадании одного из сигналов ППР или ВВОД. Все остальные сигналы магистралей 9 и 9 проходят транзитом через группу приемопередатчиков 86,

о

Формула изобретения

первую и вторую группы блоков обработки информации, первые входы-выходы первого блока сопряжения соединены с первыми входамт- -вр)Гходами второго блока сопряжения, отличающая - с я тем, что, с целью повышения быстродействия системы за счет уменьшения времени подключения каншюв к вычислительным блокам, в нес дополнительно введены блок умощнения магистрали, блок арбитра магистрали, входы- выходы которого соединены с входами- выходами блоков обработки информации рторой группы, первые вход11-вь ходы блока умоцнения магистрали соединены с первыми входами-выходами первого и второго блоков сопряжения и входа- n -выxoдaми блоков обработки информации Г1ОРВОЙ группы, вторые входы-выходы блока умощнения магистрали соединены с входаг ги-выходами блоков обработки информащ1и второй группы, вхо- : , первого и второго вычисли- гельных блоков второго уровня соединены с вторыми входами-выходами пер-. вого и второго блоков сопряжения соответственно,

блок первого уровня, блок связи и группу из М информационных входов-, выходов системы, К-с информационные входы-выходы системы., где К 1, . . . , М о

соединены с К-ми входами-выходами блока связи, (M-t-l)-e входы-выходы блока связи соединены с первыми вхо- даьм-выходами вычислите-пьного блока первого уровня, вторые входы-выходы которого соединены с первыми входами- выходами блока сопряжения, вторые входы-выходы которого являются входами-выходами блока обработки информа- ции первой группы.

9г SS S

/ //

1

/

/

7

2

3S

J

2з

ь

J Фиг.

фие,д

i

9z

в

4

L

ь

J г.

;

AVP

9fS,

Sf 9,

3f 9i

Sf -9,

9 г 9, ue.S

97-101

С6РОС

By,6m,

ППР

Л V

(pus.б

JL

,-. ...

h

gyusj

намз сигнала ВУна бходе 98

Нет

Ана/1из си г на/га на бходе 99

Нет

А на/ из сигмам СИ А на Sходе 97

jcmaHoSxo сигнала 5мки- робки адреса на отходе 105

Устанодка сигна/гараз- рсшения ВУна бо/ходе W8

стоноохд сигнала разрешения ПУСК ЗУ на бшоде 106

станоокасигна/ й разрешения СИЛ на оь/коде

Чстаноока сигнала разре - шения передаva оанн1 /х иа бшоде fG4

ЧстаноВка сигнала разрешения В80М на быхаое JQS

Анализ сигнала СИЛ на бходе 97

Сброс осех сигналов на быходе ПЗУ

( Конец

( j

иа

Анализ сигнала СИЛ набходе 97

VcmoHoSxa сигнала олохи - poSxu адреса но др/ходе

а

(actJгнp/ a раз - решения В У на бшоде 108

Чстанобха сигала оазре - шения оАигна быходе Ю7

у с та но Ока сигнсзла разрешения ПУСК ЗУ ма йшоде i06

Устанооха сигна/ а раз- решений СИ А на

быходе 102

остановка сигнала разрешения передали данных на оыхаде 10

Устаноока JSHa/ja разрешения ЬыВоддна дыхоае 103

Анализ сигна/га СИАно бходе 97

Cfpoc Scex сигна/ о8 на 6i ixode ПЗУ

С Конец )

( Начало j

Анализ сигнала ВВОД . на б ходе 100

Анализ сигна/}а ППР не дходе /Of

Чстанобка сигио/ia разрешения передQiitj данных на бшходе 10 if

станобна суенала разрешение t додана дыходе W5

Анализ сигнала ППР на дходе 101

С Spec сигнамб но бы ходе ПЗУ

ФиеЮ

Конец

| Мультипроцессорный крейтконтроллер | 1980 |

|

SU1072054A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Система автоматизации исследований | 1980 |

|

SU900287A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-09-15—Публикация

1987-02-16—Подача