Изобретение относится к вычислительной и измерительной технике и может быть использовано при построении вычислительных многопроцессорных систем и устройств управления конт- ррльно-измерительных управляющих . систем.

Цель изобретения - сокращение аппаратурных затрат устройства.

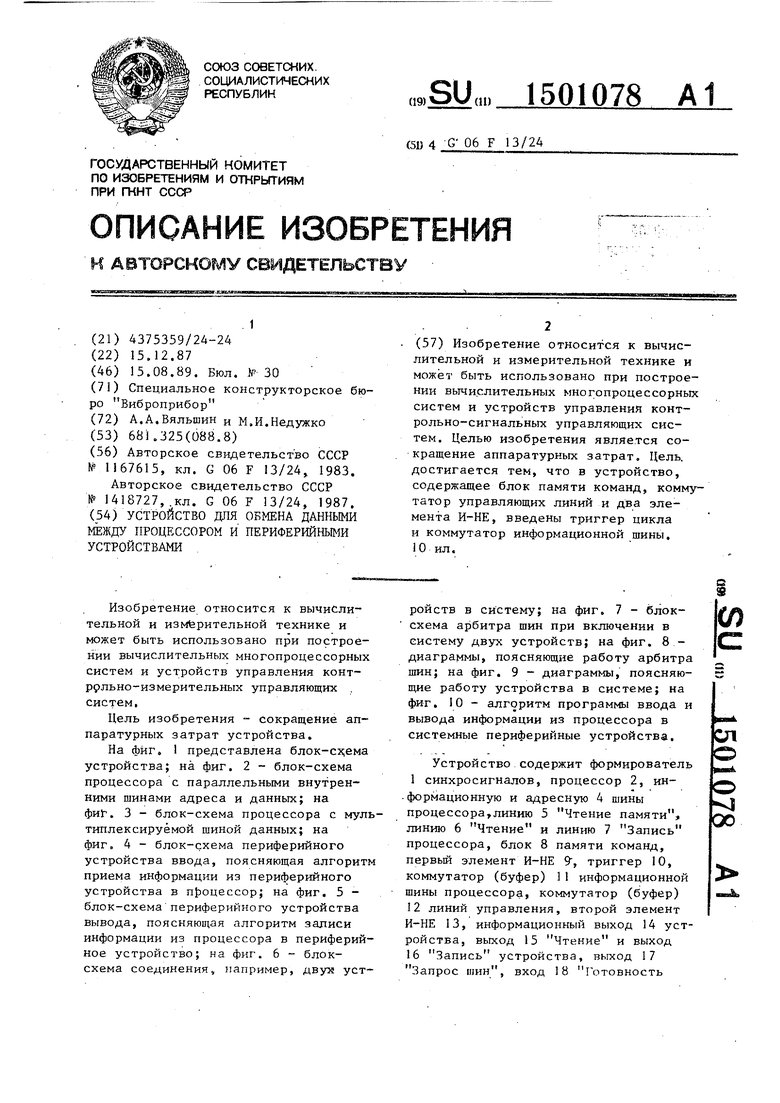

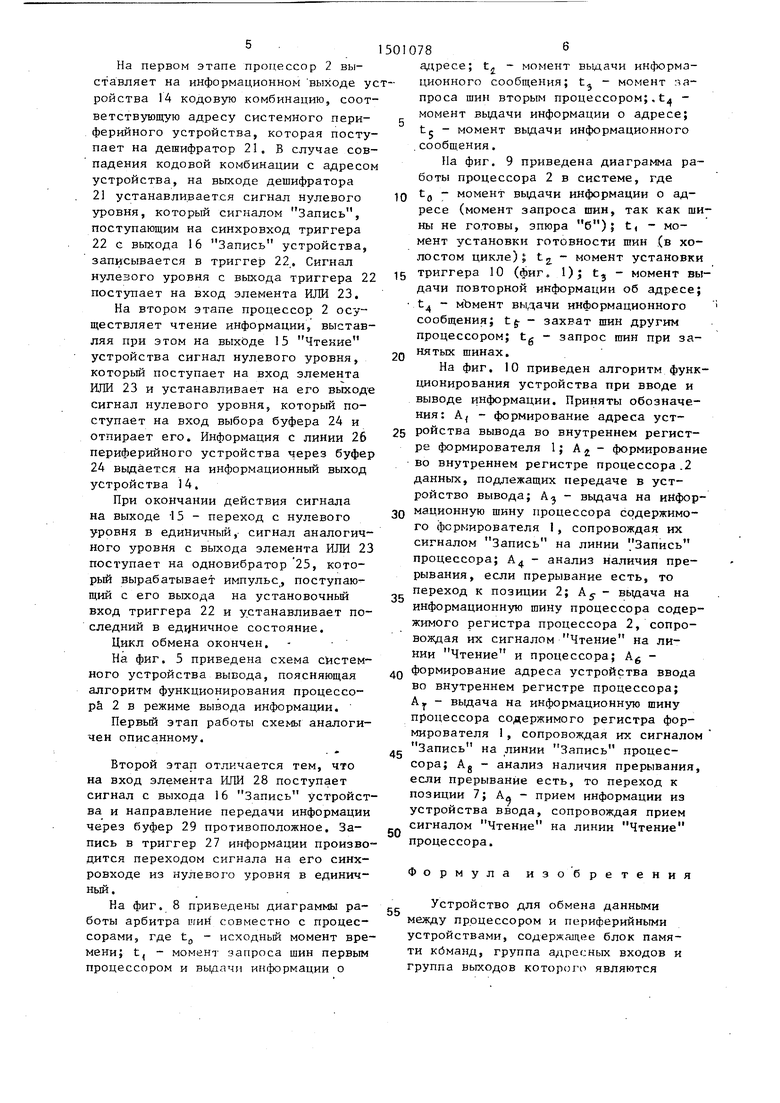

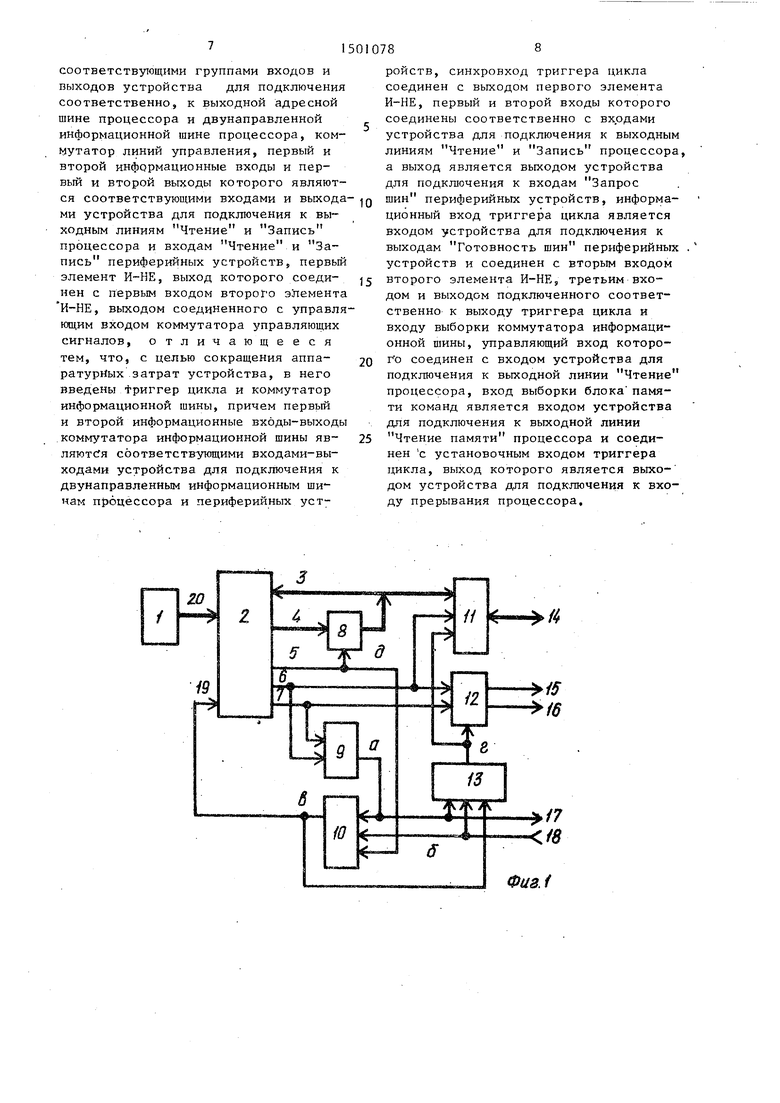

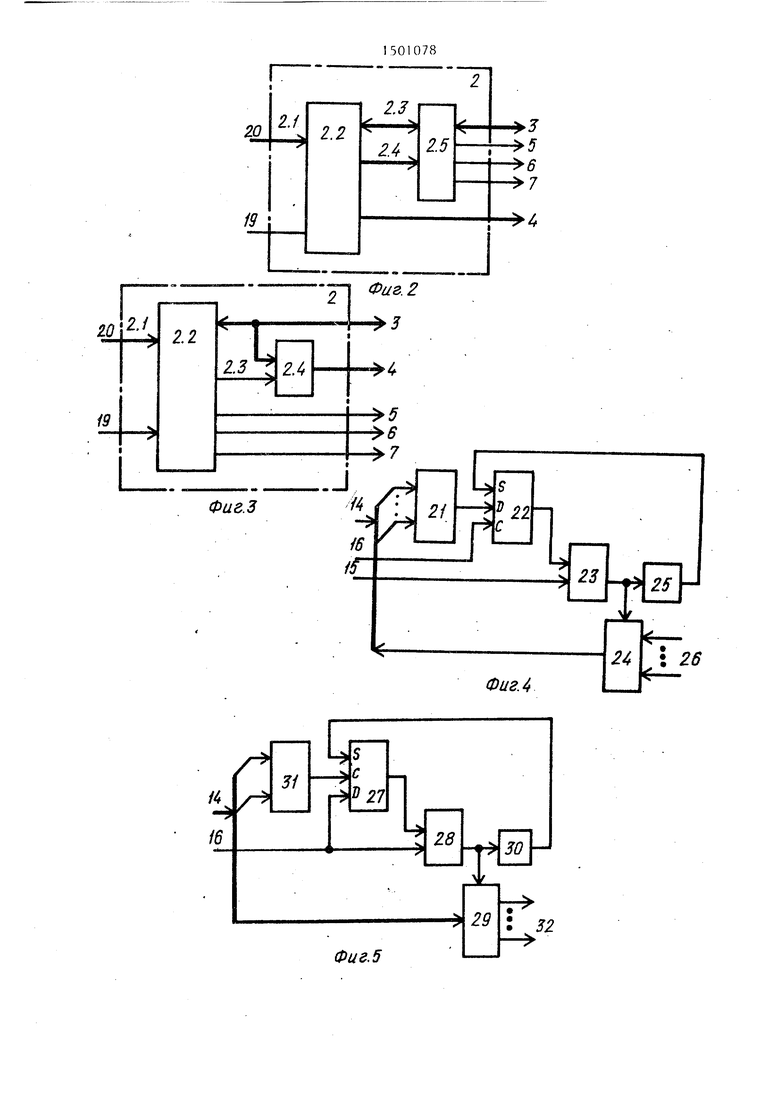

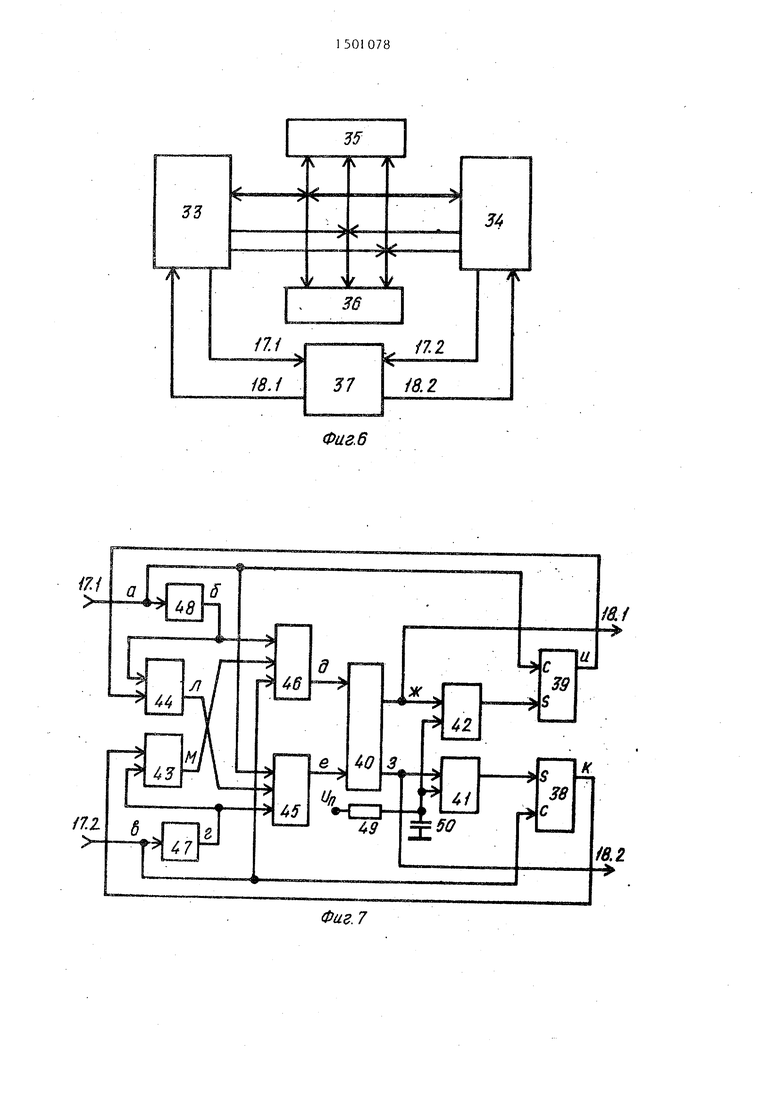

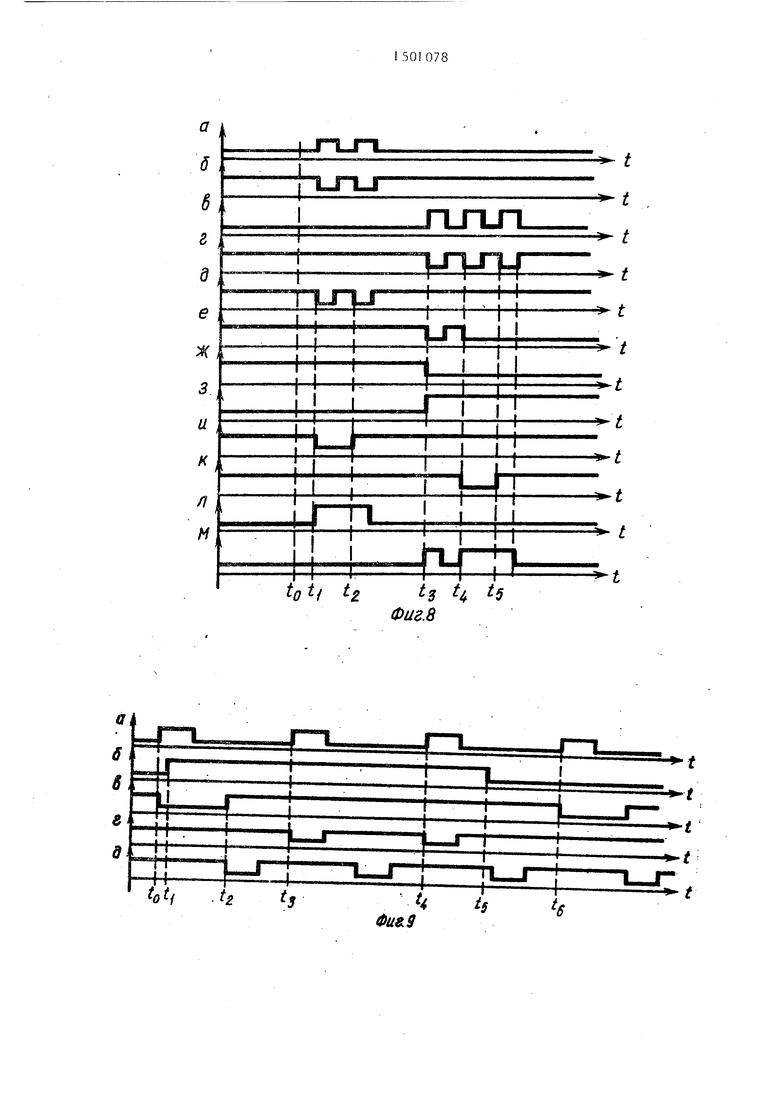

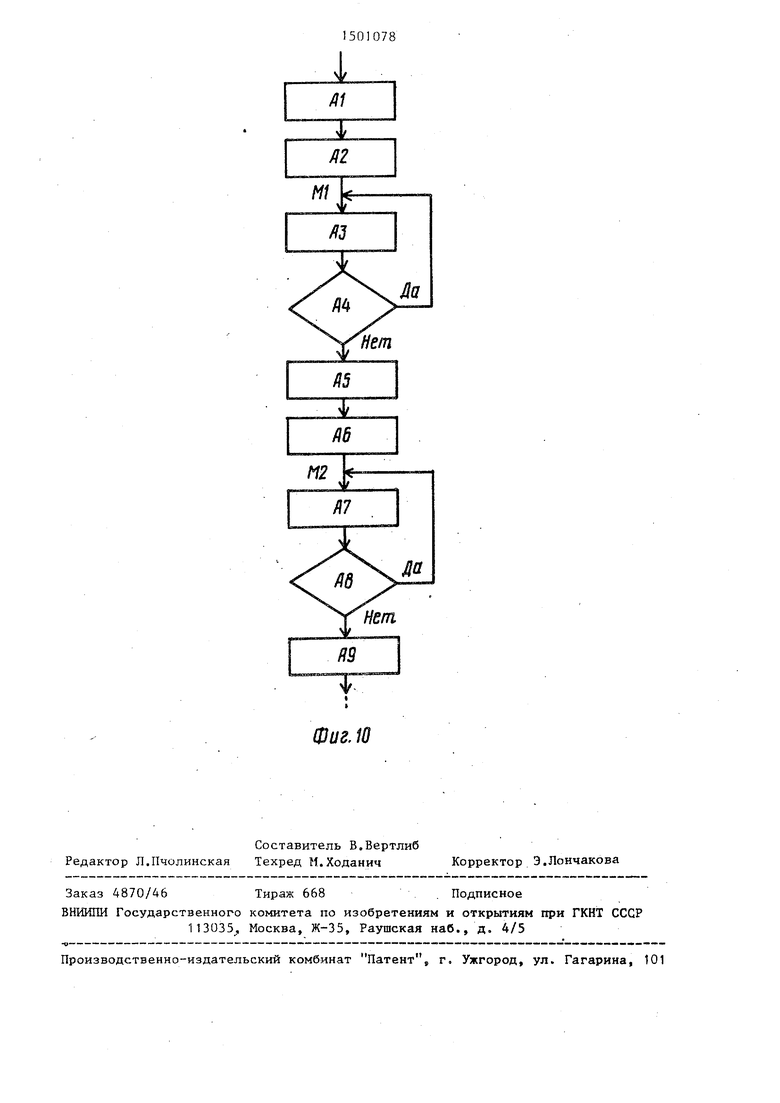

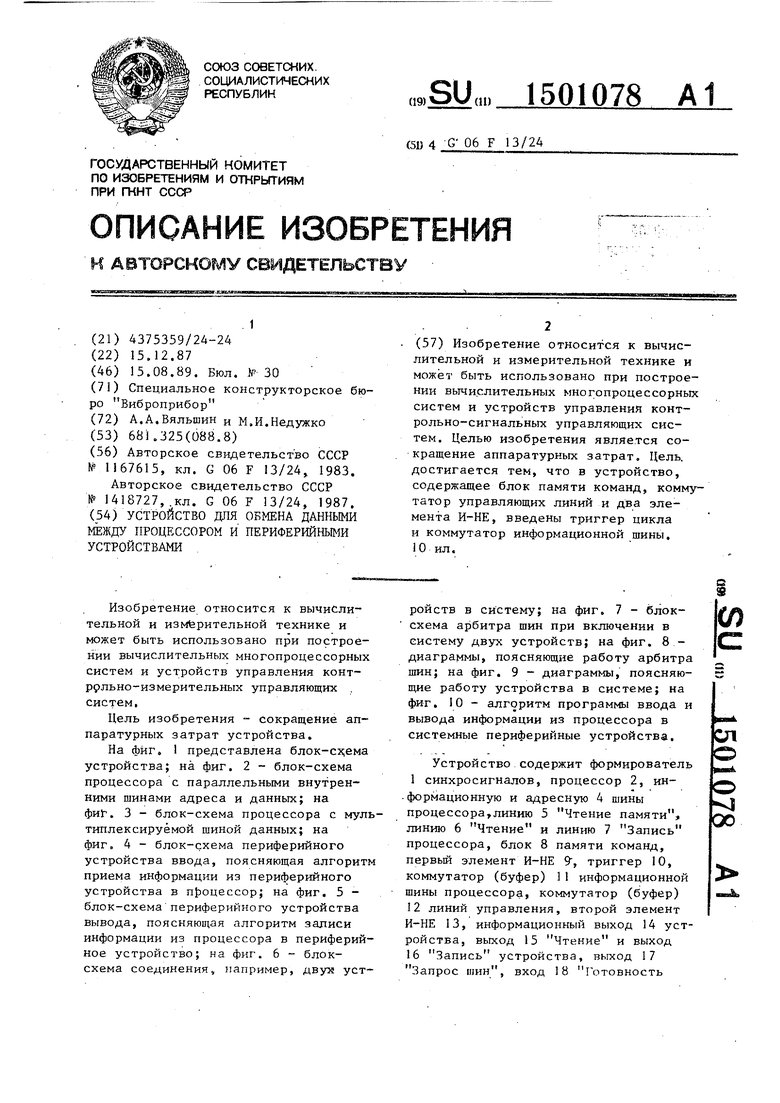

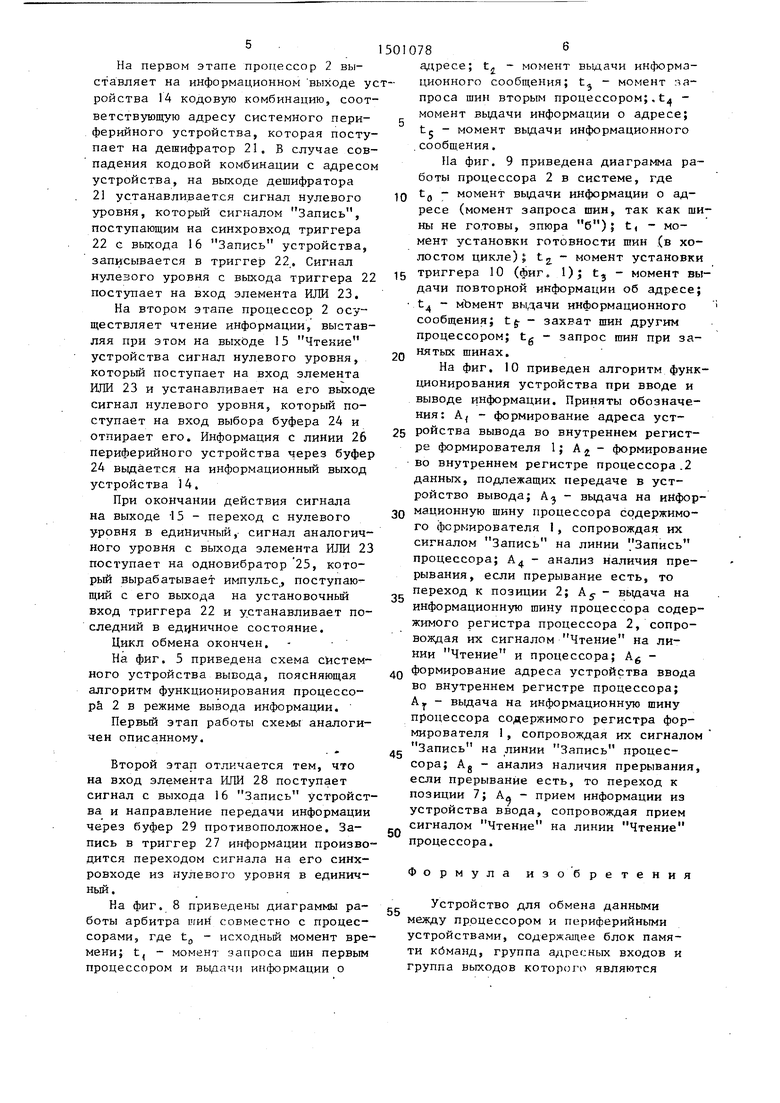

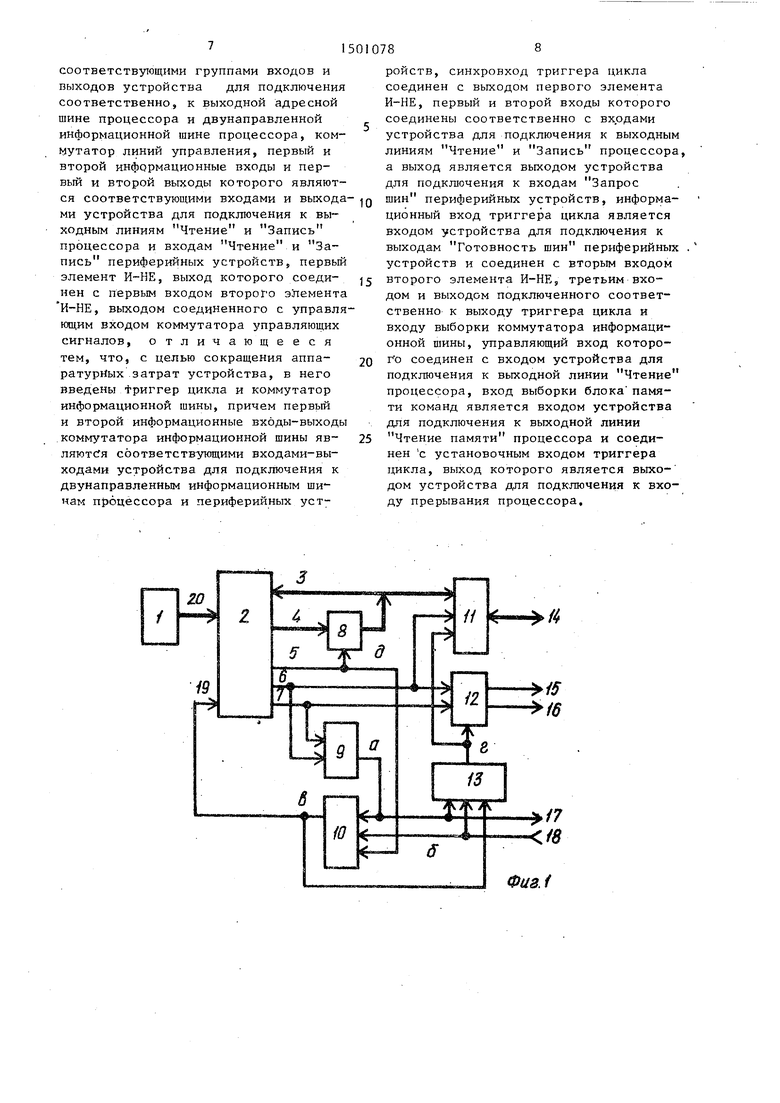

На фиг. 1 представлена блок-сх;ема устройства; на фиг. 2 - блок-схема процессора с параллельными внутренними шинами адреса и данных; на фи):-. 3 - блок-схема процессора с мультиплексируемой шиной данных; на фиг. 4 - блок-схема периферийного устройства ввода, поясняющая алгоритм приема информации из периферийного устройства в процессор; на фиг. 5 - блок-схема периферийного устройства вывода, поясняющая алгоритм записи информации из процессора в периферийное устройство; на фиг. 6 блок- схема соединения, например, двух устройств в систему; на фиг. 7 - блок- схема арбитра шин при включении в систему двух устройств; на фиг. 8 - диаграммы, поясняющие работу арбитра шин; На фиг. 9 - диаграммы, поясняю- S щие работу устройства в системе; на фиг. 10 - алгоритм программы ввода и вывода информации из процессора в системные периферийные устройства.

(Л

СП

Устройство содержит формирователь 1 синхросигналов, процессор 2, ин- формационную и адресную 4 шины процессора линию 5 Чтение памяти, линию 6 Чтение и линию 7 Запись процессора, блок 8 памяти команд, первьй элемент И-НЕ 9, триггер 10, коммутатор (буфер) 11 информационной шины процессора, коммутатор (буфер) 12 линий управления, второй элемент И-НЕ 13, информационный выход 14 устройства, выход 15 Чтение и выход 16 Запись устройства, выход 17 Запрос шин, вход 18 Готовность

41

Ъо

шп, вход 19 прерывания процессора и вход 20 синхронизации процессора. Процессор 2 при выполнении (фиг,2) а базе микропроцессора с раздельными с инами адреса и данных (например, на ИС К580ВМ80) содержит тактовый вход .1, микропроцессор 2.2, информационую шину 2. 3, линии 2,4 управления и системный контроллер 2,5 (например, Ю БИС К580БК28),

При выполнении (фиг, 3) на базе однокристальной ЭВМ (например, на БИС К1816ВЕ48), имеющей мультиплексную шину адреса и данных, процессор 15 2 содержит тактовый вход 2 „ I , ЭВМ 2,2, линию 2.3 синхронизации адреса и регистр 2,4 адреса (например, К589ИР12),

Периферийное устройство ввода 20 состорт из дешифратора 21 адреса, триггера. 22, элемента ИЛИ 23, коммутатора (буфера) 24, одновибратора 25 и информационных линий -26,

Периферийное устройство вывода 25 (фиг, 5). содержит триггер 27, элемент ИЛИ 28, коммутатор (буфер) 29, одновибрЯтор ЗО, дешифратор 31 адреса и информационные линии 32,

Система из двух процессоров 30 (фиг« 6) .состоит из процессоров 33 и 34, устройств 35 и 36 ввода и вывода j арбитра 37 шин, включающего, например, триггеры 38-40, элементы И 41 и 42, элементы И-НЕ 43 и 44, 35 элементы ИЛИ 45 и 46, элементы,НЕ 47 и 48,ограничительный резистор 49 и накопительньш конденсатор 50,

Устройство работает следующим образом,40

В исходный момент времени от схемы предустановки (на схеме не тюказа- но) процессор 2 устанавливается в состояние, при котором адрес первой выбираемой команды является началь- 45 HbfM адресом программы его работы

Под действием синхросигналов, .поступающих от формирователя 1 в процессор 2, последний начинает в каждом машинном цикле вырабатывать сиг- о нал на линии 5 (импульс нулевого уровня), который совместно с кодовой комбинацией, устанавливаемой процессором.-2 на адресной шине 4 и поступающей на адресные входы блока 8 памяти. По этому сигналу процессор 2 считывает код текущей команды, выдаваемой из соответствующей ячейки памяти 8 на информационную

шину 3, Код команды дешифрируется внутри процессора 2 и если это команда ввода или вывода информации из процессора 2 в периферийнре устройство, то осуществляется соответствующий .цикл Чтение или Запись,

Цикл Чтение осуществляется следующим образом,

С выхода процессора 2 на линию 6 выдается импульс отрицательной полярности (сигнал переходит из единичного уровня в нулевой и обратно в единичный), который через элемент И-НЕ 9 поступает на вход триггера 10 на первый вход элемента И-НЕ 13 и на выход 17, В триггер 10 .записывается информация о готовности шин системы. Если шины были не готовы (на входе 1 Готовность шин сигнал нулевого уровня), то в триггер 10 записывается сигнал нулевого уровня, который поступает на вход элемента И-НЕ 13 и запирает его, а также поступает на вход 19 прерывания процессора.При этом.буфер 11 информационной шины, установленный сигналом Чтение на линии 6 на ввод информации с информационного выхода 14 на информационную шину 3, и буфер 12 выбраны не будут. После окончания цикла (холостого) чтения процессор 2 по сигналу на входе прерывания переходит к обработке прерывания - внутренний счетчик команд процессора 2 з еньшает свое содержимое на единицу и цикл Чтение повторяется. Триггер 10 установлен в единичное состояние первым сигналом на линии 5.

Цикл Запись аналогичен циклу Чтение, только буфер 11 устанабли- вается на пропускание информации с информационной шины 3 на информационный выход 14,

В случае готовности системных шин (сигнал единичного уровня на входе 18) единичные сигналы с выходов элемента И-НЕ 9, триггера 10 и входа 18 поступают на входы элемента И-НЕ 13, выходной сигнал которого разрешает выборку буферов 11 и 12. Происходит обмен информацией между процессором 2 и системным периферийным оборудованием.

На фиг, 4 приведена схема системного устройства ввода, .поясняющая алгоритм функционирования процессора 2 в режиме приема информации.

На первом этапе процессор 2 вы- ставляет на информационном выходе ройства 14 кодовую комбинацию, сооветствующую адресу системного пери ферийного устройства, которая постпает на дешифратор 21, В случае сопадения кодовой комбинации с адрес устройства, на выходе дешифратора

21устанавливается сигнал нулевого уровня, который сигналом Запись, поступающим на синхровход триггера

22с выхода 16 Запись устройства записывается в триггер 22, Сигнал нулевого уровня с выхода триггера поступает на вход элемента ИЛИ 23,

На втором этапе процессор 2 осуществляет чтение информации, выставляя при этом на выходе 15 Чтение устройства сигнал нулевого уровня, которьй поступает на вход элемента ИЛИ 23 и устанавливает на его выход сигнал нулевого уровня, который поступает на вход выбора буфера 24 и отпирает его. Информация с линии 26 периферийного устройства через буфе 24 вьщается на информационный выход устройства 14.

При окончании действия сигнала на выходе 15 - переход с нулевого уровня в единичный, сигнал аналогичного уровня с выхода элемента ИЛИ 2 поступает на одновибратор 25, который вырабатывает импульс, поступаю щий с его выхода на установочный вход триггера 22 и устанавливает последний в единичное состояние,

Цикл обмена окончен.

На фиг, 5 приведена схема с 1стем ного устройства вывода, поясняющая алгоритм функционирования процессо- р& 2 в режиме вывода информации.

Первый этап работы схемы аналогичен описанному.

Второй этап отличается тем, что на вход элемента ИЛИ 28 поступает сигнал с выхода 16 Запись устройства и направление передачи информации через буфер 29 противоположное. Запись в триггер 27 информации производится переходом сигнала на его синх- ровходе из нулевого уровня в единич- ньй.

На фиг, 8 приведены диаграммы работы арбитра игий совместно с процессорами, где tg - исходный момент времени; t( - момйнт запроса шин первым процессором и выдачи информации о

адресе;

t - момент выдачи информационного сообщения; t - момент проса шин вторым процессором;.t - момент выдачи информации о адресе; tf - момент выдачи информационного сообш.ения,

Па фиг. 9 приведена диаграмма работы процессора 2 в системе, где tg - момент выдачи информации о адресе (момент запроса шин, так как шины не готовы, эпюра б); t, - момент установки готовности шин .(в холостом цикле); t момент установки триггера 10 (фиг, 1); t. - момент выдачи повторной информации об адресе; t, - мЪмент ВЦ-дачи информационного

Ч захват шин другим запрос гаин при засообщения; tj- - процессором; нятых шинах.

На фиг, 10 приведен алгоритм функционирования устройства при вводе и выводе информации. Приняты обозначения: А - формирование адреса устройства вывода во внутреннем регистре формирователя 1; А - формирование во внутреннем регистре процессора .2 данных, подлежащих передаче в устройство вывода; А - выдача на инфор- мационную шину процессора содержимого формирователя 1, сопровождая их

сигналом Запись на линии Запись

процессора; А - анализ наличия прерывания, если прерывание есть, то переход к позиции 2; А у - выдача на информационную шину процессора содержимого регистра процессора 2, сопровождая их сигналом Чтение на линии Чтение и процессора; Ag - формирование адреса устройства ввода во внутреннем регистре процессора; А - выдача на информационную шину процессора содержимого регистра формирователя 1, сопровождая их сигналом Запись на линии Запись процессора; Ag - анализ наличия прерывания, если прерывание есть, то переход к позиции 7; Ад - прием информации из устройства ввода, сопровождая прием сигналом Чтение на линии Чтение процессора.

Формула изобретения

Устройство для обмена данными между процессором и периферийными устройствами, содержащее блок памяти кбманд, группа адресных входов и группа выходов которого являются

соответствующими группами входов и выходов устройства для подключения соответственно, к выходной адресной шине процессора и двунаправленной информационной шине процессора, коммутатор линий управления, первый и второй информационные входы и первый и второй выходы которого являются соответствующими входами и выхода ми устройства для подключения к выходным линиям Чтение и Запись процессора и входам Чтение и Запись периферийных устройств, первый элемент И-НЕ, выход которого соеди- нен с первым входом второго элемента И-НЕ, выходом соединенного с управля нлцим входом коммутатора управляющих сигналов, отличающееся тем, что, с целью сокращения аппа- ратурНых затрат устройства, в него введены Фриггер цикла и коммутатор информационной шины, причем первьй и второй информационные входы-выходы коммутатора информационной шины яв- ляютсГя соответствующими входами-выходами устройства для подключения к двунаправленным информационным шинам процессора и периферийных устройств, синхровход триггера цикла соединен с выходом первого элемента И-НЕ, первый и второй входы которого соединены соответственно с входами устройства для подключения к выходным линиям Чтение и Запись процессора а выход является выходом устройства для подключения к входам Запрос шин периферийных устройств, информационный вход триггера цикла является входом устройства для подключения к выходам Готовность шин периферийных устройств и соединен с вторым входом второго элемента И-НЕ, третьим входом и выходом подключенного соответственно к выходу триггера цикла и входу выборки коммутатора информационной шины, управляющий вход которого соединен с входом устройства для подключения к выходной линии Чтение процессора, вход выборки блока памяти команд является входом устройства для подключения к выходной линии Чтение памяти процессора и соединен с установочным входом триггера цикла, выход которого является выхо- дом устройства для подключения к входу прерывания процессора.

Фиг. 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультиплексное устройство для обмена информацией | 1983 |

|

SU1157546A1 |

| Микропроцессорное устройство обработки данных | 1982 |

|

SU1291999A1 |

| Многоканальная система управления распределением ресурсов в вычислительном комплексе | 1987 |

|

SU1432580A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1987 |

|

SU1501077A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство для сопряжения ЭВМ с магистралью | 1988 |

|

SU1508227A1 |

| Многопроцессорная система | 1989 |

|

SU1647597A1 |

| Устройство для сопряжения двух магистралей | 1984 |

|

SU1241249A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для сопряжения ЭВМ с магистралью внешних устройств | 1985 |

|

SU1408440A1 |

Изобретение относится к вычислительной и измерительной технике и может быть использовано при построении вычислительных многопроцессорных систем и устройств управления контрольно-сигнальных управляющих систем. Целью изобретения является сокращение аппаратурных затрат. Цель достигается тем, что в устройство, содержащее блок памяти команд, коммутатор управляющих линий и два элемента И-НЕ, введены триггер цикла и коммутатор информационной шины. 10 ил.

Фиг.6

Фиг.7

tot tz

ty t ts

Фиг.В

Фи&9

м

Нет

Аи

Нет

| Устройство для обмена данными между процессором и периферийными устройствами | 1983 |

|

SU1167615A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обмена данными между процессором и периферийными устройствами | 1987 |

|

SU1418727A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-08-15—Публикация

1987-12-15—Подача