2

4

Ч

СО ч

Изобретение относится к вычислительной технике и предназначено для создания децентрализованных высокопроизводительных вычислительных систем.

Целью изобретения является повышение производительности устройства за счет уменьшения интенсивности обращения процессоров многопроцессорной системы к общей шине при работе со спусковыми функциями.

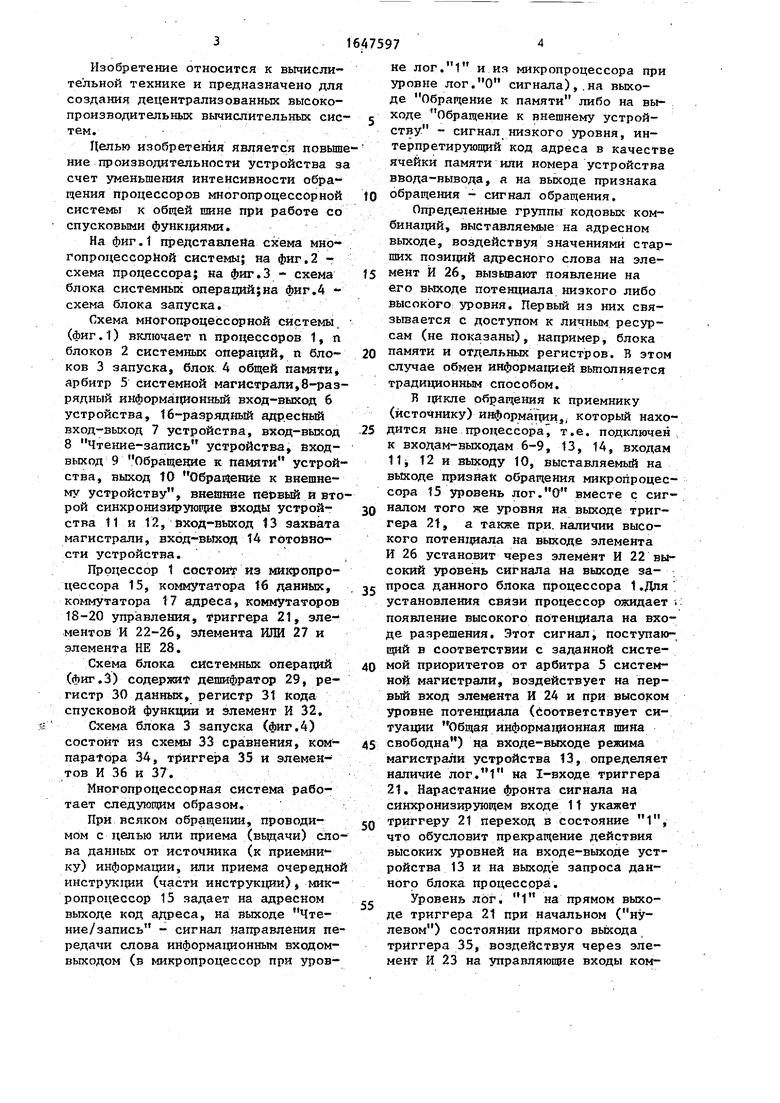

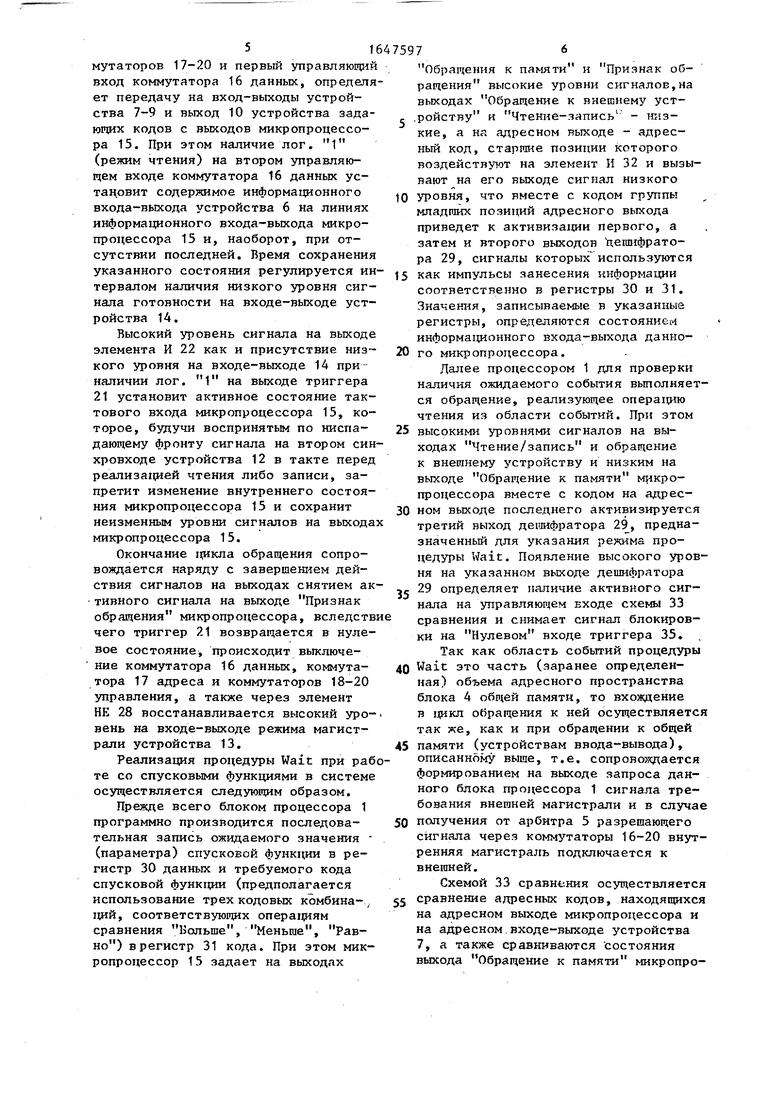

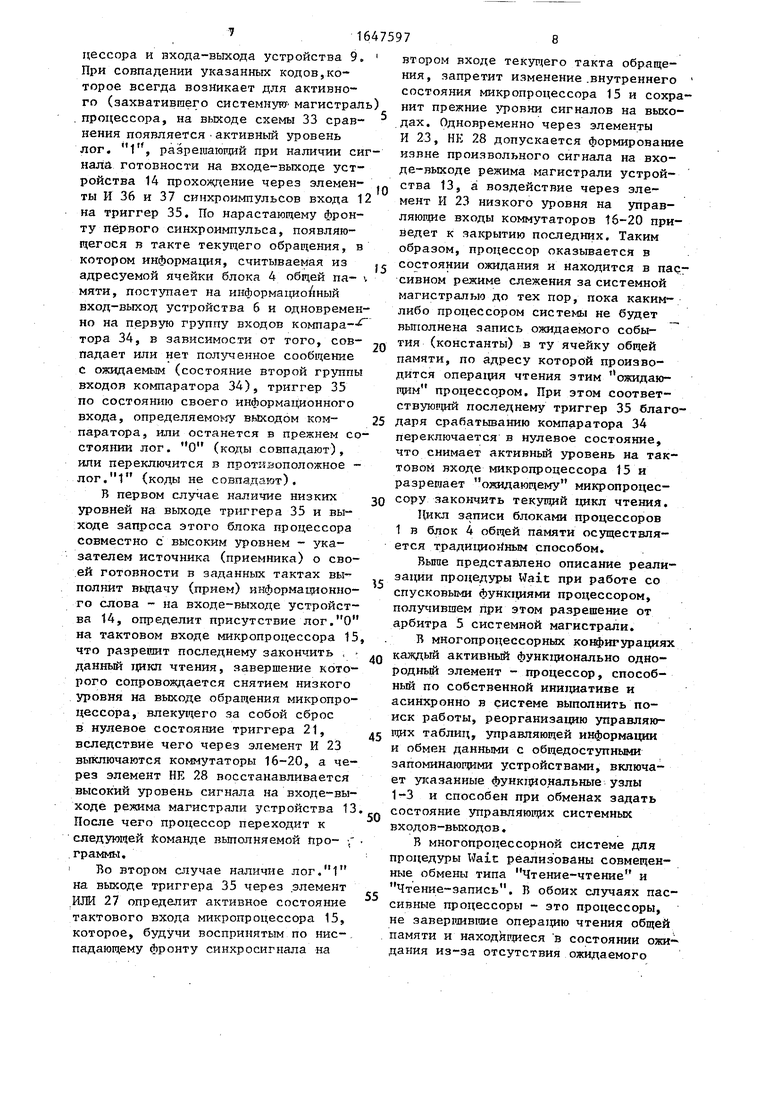

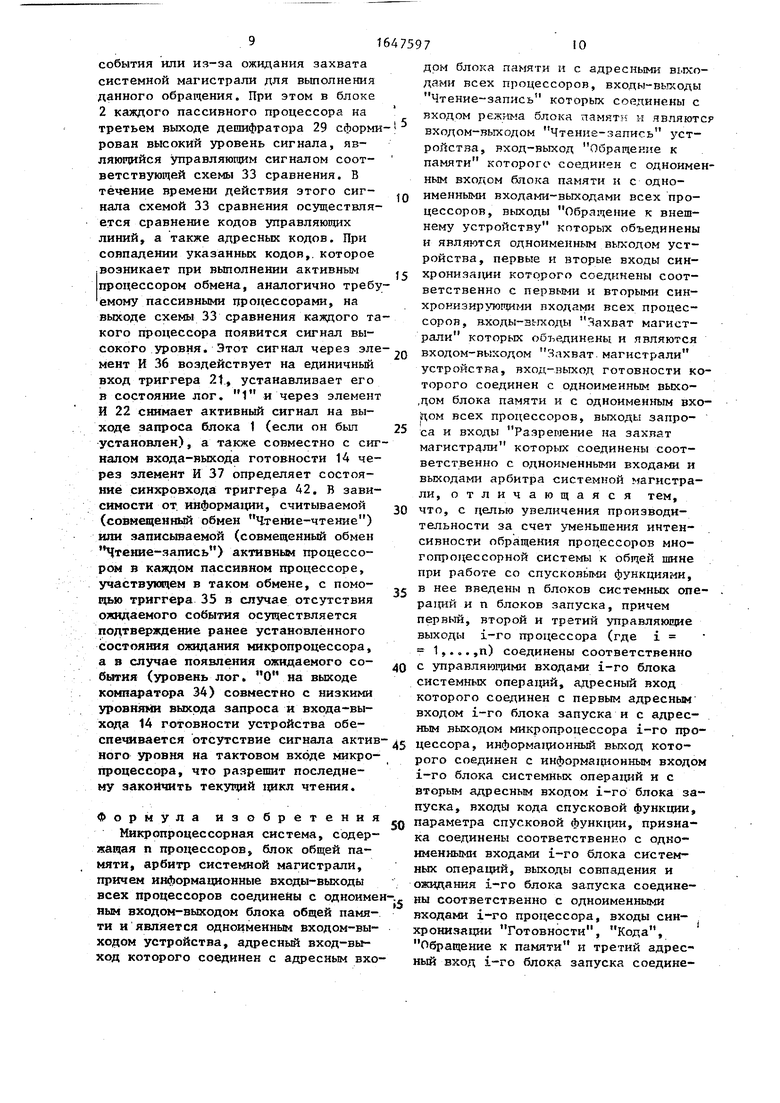

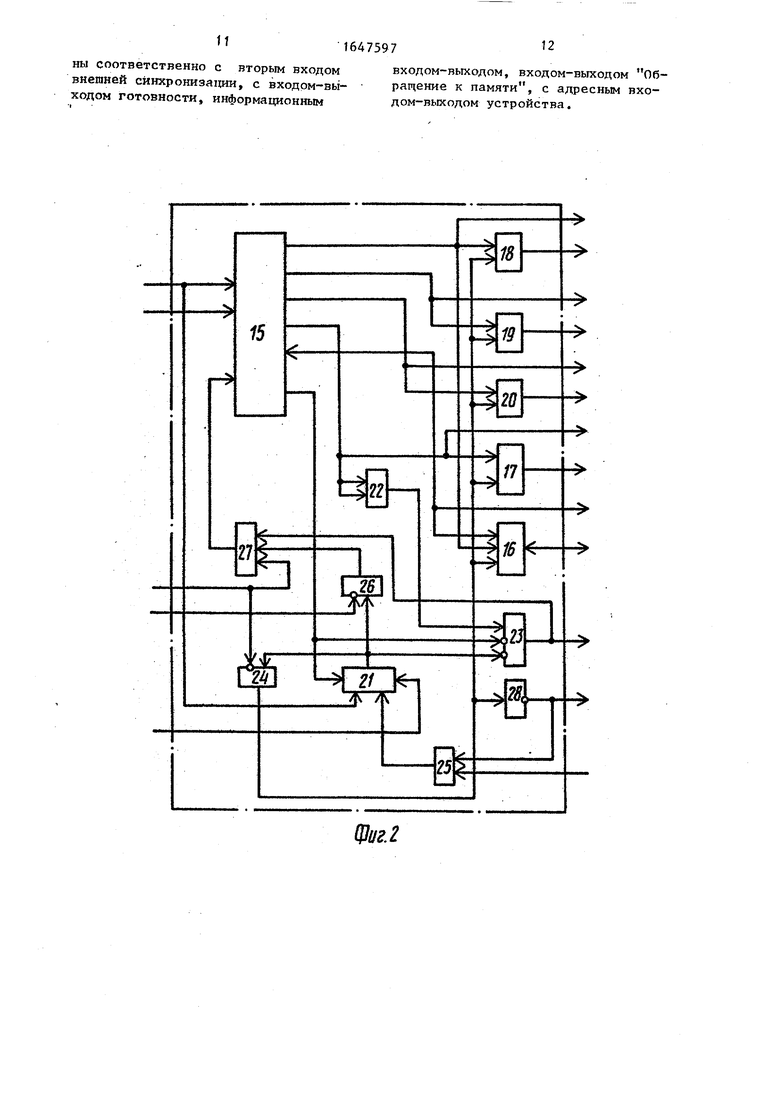

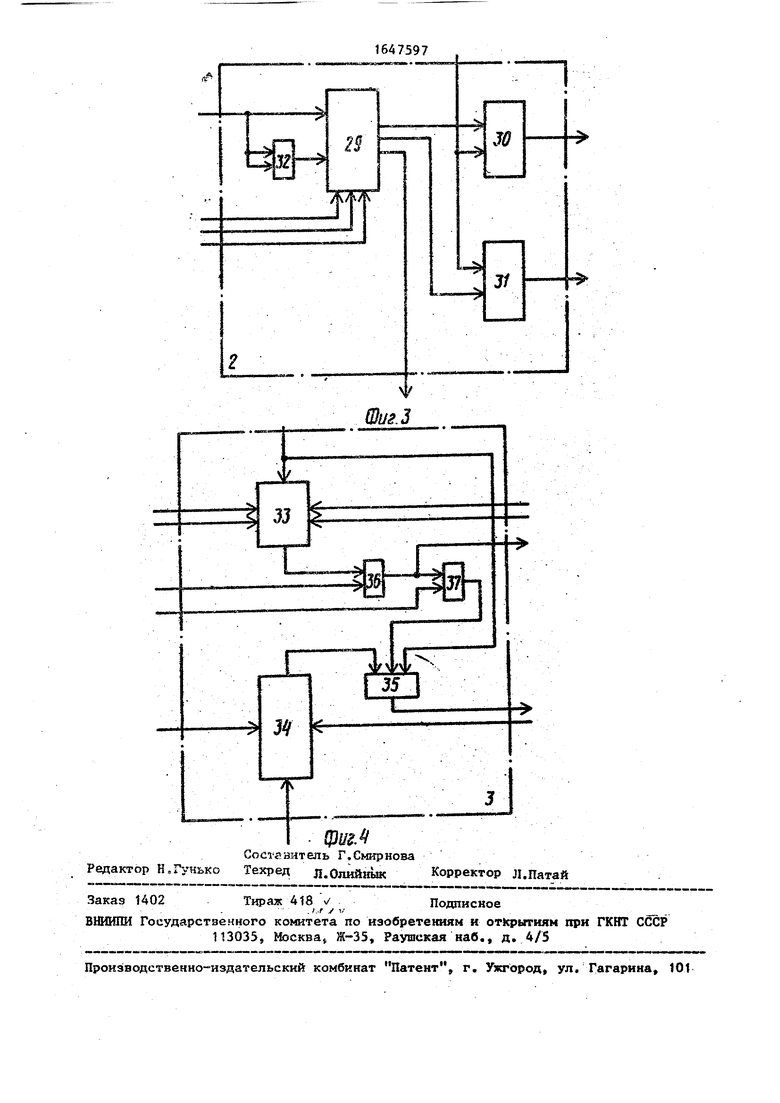

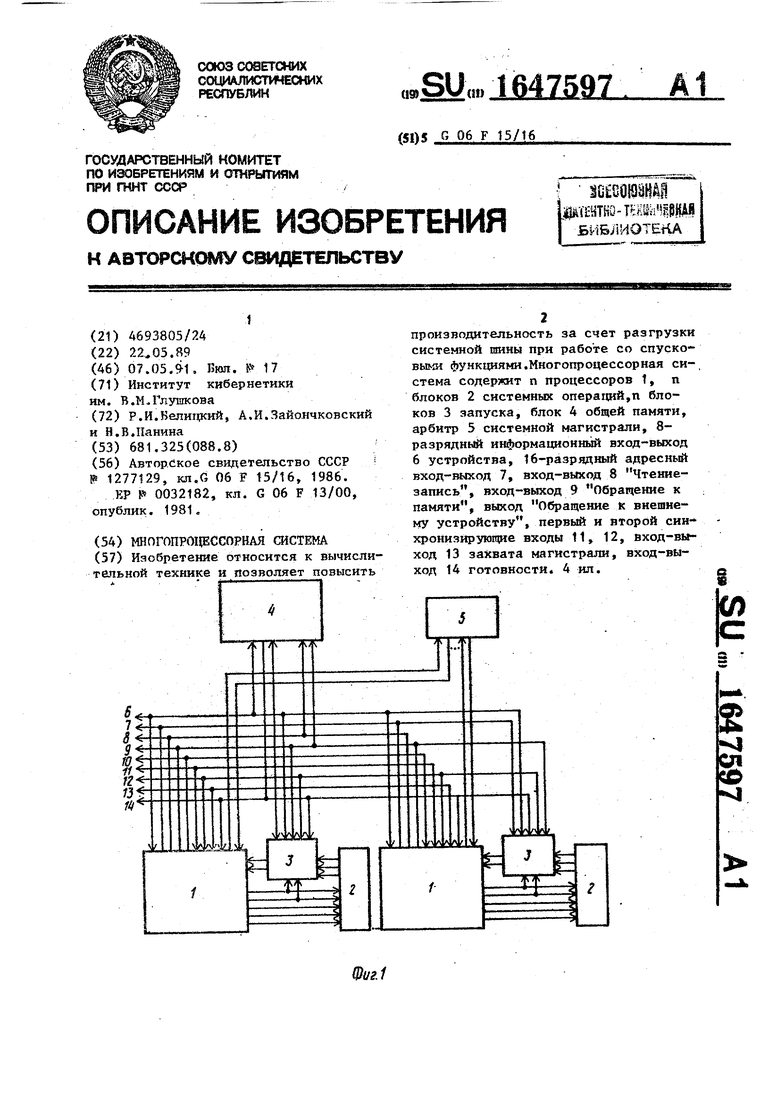

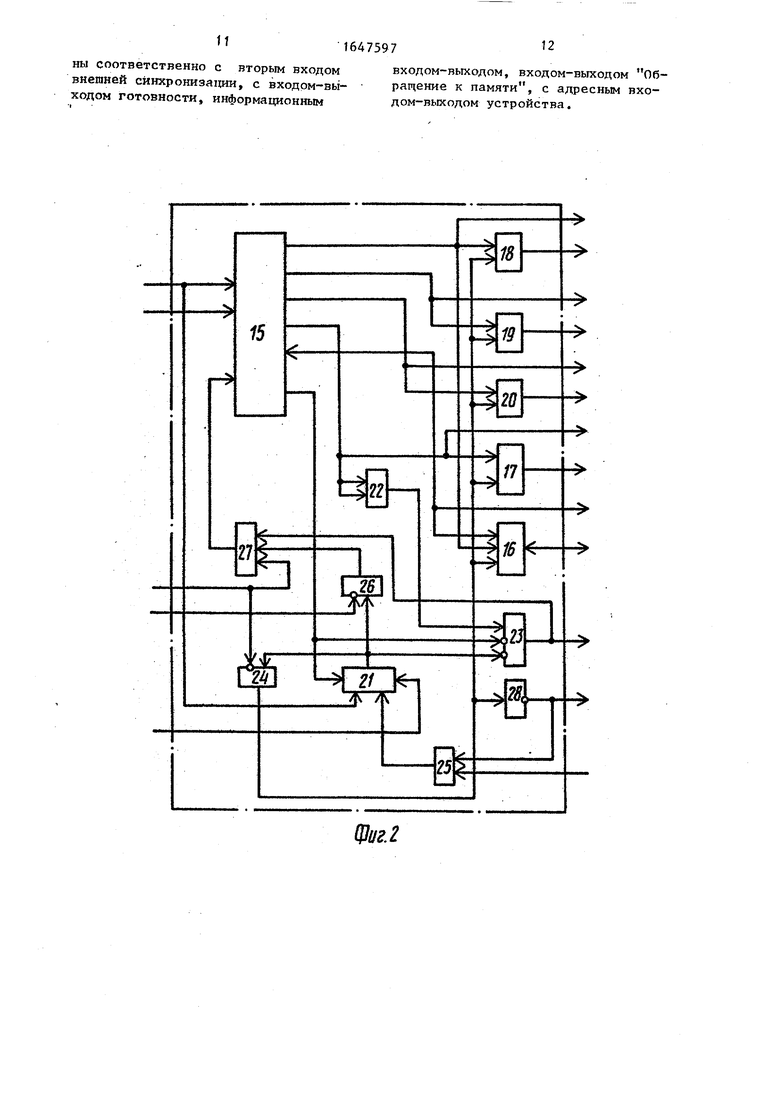

На фиг.1 представлена схема многопроцессорной системы; на фяг.2 - схема процессора; на фиг.З - схема блока системных операций;на фиг.4 - схема блока запуска.

Схема многопроцессорной системы (фиг.1) включает п процессоров 1, п блоков 2 системных операций, п блоков 3 запуска, блок 4 общей памяти, арбитр 5 системной магистрали,8-разрядный информационный вход-выход 6 устройства, 16-разрядный адресный вход-выход 7 устройства, вход-выход 8 Чтение-запись устройства, вход- выход 9 Обращение к памяти устройства, выход tO Обращение к внешнему устройству, внешние первый и второй синхронизирующие входы устройства 11 и 12, вход-выход 13 захвата магистрали, вход-выход 14 готовности устройства.

Процессор 1 состой из микропроцессора 15, коммутатора 16 данных, коммутатора 17 адреса, коммутаторов 18-20 управления, триггера 21, элементов И 22-26, элемента ИЛИ 27 и элемента НЕ 28.

Схема блока системных операций (Лиг.З) содержи дешифратор 29, регистр 30 данных, регистр 31 кода спусковой Функции и элемент И 32,

Схема блока 3 запуска (фиг.4) состоит из схемы 33 сравнения, компаратора 34, триггера 35 и элементов И 36 и 37.

Многопроцессорная система работает следующим образом.

При всяком обращении, проводимом с целью или приема (выдачи) слова данных от источника (к приемнику) информации, или приема очередно инструкции (части инструкции), микропроцессор 15 задает на адресном выходе код адреса, на выходе Чтение/запись - сигнал направления передачи слова информационным входом- выходом (в микропроцессор при уровне лог.1 и ия микропроцессора при уровне лог.О сигнала), на выходе Обращение к памяти либо на вы- ходе Обращение к внешнему устройству - сигнал низкого уровня, интерпретирующий код адреса в качестве ячейки памяти или номера устройства ввода-вывода, а на выходе признака

0 обращения - сигнал обращения.

Определенные группы кодовых комбинаций, выставляемые на адресном выходе, воздействуя значениями старших позиций адресного слова на эле5 мент И 26, вызывают появление на его выходе потенциала низкого либо высокого уровня. Первый из них связывается с доступом к личным ресурсам (не показаны), например, блока

0 памяти и отдельных регистров. В этом случае обмен информацией выполняется традиционным способом.

В цикле обращения к приемнику (источнику) информации,, который нахо5 дится вне процессора, т.е. подключен к входам-выходам 6-9, 13, 14, входам 11, 12 и выходу 10, выставляемый на выходе признак обращения микропроцессора 15 уровень лог.О вместе с сигQ налом того же уровня на выходе триггера 21, а также при. наличии высокого потенциала на выходе элемента И 26 установит через элемент И 22 высокий уровень сигнала на выходе за5 проса данного блока процессора 1 .Для установления связи процессор ожидает . появление высокого потенциала на входе разрешения. Этот сигнал, поступающий в соответствии с заданной систе0 мой приоритетов от арбитра 5 системной магистрали, воздействует на первый вход элемента И 24 и при высоком уровне потенциала (соответствует ситуации Общая информационная шина

5 свободна) на входе-выходе режима магистраЛи устройства 13, определяет наличие лог.1 на 1-входе триггера 2t. Нарастание фронта сигнала на синхронизирующем входе 11 укажет

д триггеру 21 переход в состояние 1, что обусловит прекращение действия высоких уровней на входе-выходе устройства 13 и на выходе запроса данного блока процессора.

Уровень лог. 1 на прямом выходе триггера 21 при начальном (нулевом) состоянии прямого выхода триггера 35, воздействуя через элемент И 23 на управляющие входы ком5

мутаторов 17-20 и первый управляющий вход коммутатора 16 данных, определяет передачу на вход-выходы устройства 7-9 и выход 10 устройства задающих кодов с выходов микропроцессора 15. При этом наличие лог. 1 (режим чтения) на втором управляющем входе коммутатора 16 данных установит содержимое информационного входа-выхода устройства 6 на линиях информационного входа-выхода микропроцессора 15 и, наоборот, при отсутствии последней. Время сохранения указанного состояния регулируется интервалом наличия низкого уровня сигнала готовности на входе-выходе устройства 14.

Высокий уровень сигнала на выходе элемента И 22 как и присутствие низкого уровня на входе-выходе 14 при- наличии лог. 1 на выходе триггера 21 установит активное состояние тактового входа микропроцессора 15, которое, будучи воспринятым по ниспадающему фронту сигнала на втором син- хровходе устройства 12 в такте перед реализацией чтения либо записи, запретит изменение внутреннего состояния микропроцессора 15 и сохранит неизменным уровни сигналов на выходах микропроцессора 15.

Окончание цикла обращения сопровождается наряду с завершением дей Обращения к памяти и Признак обращения высокие уровни сигналов,на выходах Обращение к внешнему уст- ройству и Чтение-запись1 - низкие, а на адресном выходе - адресный код, старшие позиции которого воздействуют на элемент И 32 и вызывают на его выходе сигнал низкого

УРОВНЯ, что вместе с кодом группы младгаих позиций адресного выхода приведет к активизации первого, а затем и второго выходов дешифратора 29, сигналы которых используются

5 как импульсы занесения информации соответственно в регистры 30 и 31. Значения, записываемые в указанные регистры, определяются состоянием информационного входа-выхода данно-

0 го микропроцессора.

Далее процессором 1 для проверки наличия ожидаемого события выполняется обращение, реализующее операцию чтения из области событий. При этом

5 высокими уровнями сигналов на выходах Чтение/запись и обращение к внешнему устройству и низким на выходе Обращение к памяти микропроцессора вместе с кодом на адрес0 ном выходе последнего активизируется третий выход дешифратора 29, предназначенный для указания режима процедуры Wait. Появление высокого уровня на указанном выходе дешифратора

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления доступом к памяти для обмена массивами данных в многопроцессорной системе | 1989 |

|

SU1633418A1 |

| Многопроцессорная вычислительная система | 1985 |

|

SU1277129A1 |

| Устройство для обмена данными между процессором и периферийными устройствами | 1987 |

|

SU1501078A1 |

| Устройство для обмена данными между процессорами | 1988 |

|

SU1566361A1 |

| Микропроцессорная система с встроенным контролем | 1986 |

|

SU1417651A1 |

| Устройство управления сегментированной памятью многопроцессорной системы | 1990 |

|

SU1753477A1 |

| Процессор для мультипроцессорной системы | 1987 |

|

SU1517035A1 |

| Микропроцессорное устройство обработки данных | 1982 |

|

SU1291999A1 |

| Многопроцессорная вычислительная система | 1988 |

|

SU1569843A1 |

| Микропроцессорная система | 1989 |

|

SU1686454A1 |

Изобретение относится к вычислительной технике и позволяет повысить производительность за счет разгрузки системной шины при работе со спусковыми функциями.Многопроцессорная система содержит п процессоров 1, п блоков 2 системных операций,п блоков 3 запуска, блок 4 общей памяти, арбитр 5 системной магистрали, 8- разрядный информационный вход-выход 6 устройства, 16-разрядный адресный вход-выход 7, вход-выход 8 Чтение- запись, вход-выход 9 Обращение к памяти, выход Обращение к внешнему устройству, первый и второй синхронизирующие входы 11, 12, вход-выход 13 захвата магистрали, вход-выход 14 готовности. 4 ил.

ствия сигналов на выходах снятием ак- 29 определяет наличие активного сиг тивного сигнала на выходе Признак нала на управляющем нходе схемы 33 обращения микропроцессора, вследствие сравнения и снимает сигнал блокиров- чего триггер 21 возвращается в нулеки на Нулевом входе триггера 35. Так как область событий процедуры

вое состояние, происходит выключение коммутатора 16 данных, коммутатора 17 адреса и коммутаторов 18-20 управления, а также через элемент НЕ 28 восстанавливается высокий уровень на входе-выходе режима магистрали устройства 13.

Реализация процедуры Wait при рабте со спусковыми функциями в системе осуществляется следующим образом.

Прежде всего блоком процессора 1 программно производится последовательная запись ожидаемого значения (параметра) спусковой функции в регистр 30 данных и требуемого кода спусковой функции (предполагается использование трех кодовых комбина- , ций, соответствующих операциям сравнения Больше, Меньше, Равно) в регистр 31 кода. При этом микропроцессор 15 задает на выходах

29 определяет наличие активного сиг нала на управляющем нходе схемы 33 сравнения и снимает сигнал блокиров-

ки на Нулевом входе триггера 35. Так как область событий процедуры

Wait это часть (заранее определенная) объема адресного пространства блока 4 общей памяти, то вхождение в цикл обращения к ней осуществляется так же, как и при обращении к общей

памяти (устройствам ввода-вывода), описанному выще, т.е. сопровождается формированием на выходе запроса данного блока процессора 1 сигнала требования внешней магистрали и в случае

получения от арбитра 5 разрешающего сигнала через коммутаторы 16-20 внутренняя магистраль подключается к внешней.

Схемой 33 cpaBHt-ния осуществляется

сравнение адресных кодов, находящихся на адресном выходе микропроцессора и на адресном входе-выходе устройства 7, а также сравниваются состояния выхода Обращение к памяти микропро-

цессора и входа-выхода устройства 9. При совпадении указанных кодов,которое всегда возникает для активного (захватившего системную магистраль) процессора, на выходе схемы 33 срав- нения появляется .активный уровень лог. 1, разрешающий при наличии сигнала готовности на входе-выходе устройства 14 прохождение через элемен- ,„ ты И 36 и 37 синхроимпульсов входа 12 на триггер 35. По нарастающему фронту первого синхроимпульса, появляющегося в такте текущего обращения, в котором информация, считываемая из адресуемой ячейки блока 4 общей па- v мяти, поступает на информационный вход-выход устройства 6 и одновременно на первую группу входов компара- тора 34, в зависимости от того, совпадает или нет полученное сообщение с ожидаемым (состояние второй группы входов компаратора 34), триггер 35 по состоянию своего информационного входа, определяемо выходом комJ5

20

25

паратора, или останется в прежнем состоянии лог. О (коды совпадают), или переключится в противоположное - лог,1 {коды не совпадают).

В первом случае наличие низких уровней на выходе триггера 35 и выходе запроса этого блока процессора совместно с высоким уровнем - указателем источника (приемника) о своей готовности в заданных тактах выполнит выдачу (прием) информационного слова - на входе-выходе устройства 14, определит присутствие лог.О на тактовом входе микропроцессора 15 что разрешит последнему закончить , - данный цикл чтения, завершение рого сопровождается снятием низкого уровня на выходе обращения микропроцессора, влекущего за собой сброс в нулевое состояние триггера 21, вследствие чего через элемент И 23 выключаются коммутаторы 16-20, а через элемент НЕ 28 восстанавливается высокий уровень сигнала на входе-выходе режима магистрали устройства 13 После чего процессор переходит к следующей команде выполняемой про- -, граммы.

Во втором случае наличие лог. Ч на выходе триггера 35 через элемент ИЛИ 27 определит активное состояние тактового входа микропроцессора 15, которое, будучи воспринятым по ниспадающему фронту синхросигнала на

„

5

0

втором входе текущего такта обращения, запретит изменение.внутреннего состояния микропроцессора 15 и сохранит прежние уровни сигналов на выходах. Одновременно через элементы И 23, НЕ 28 допускается формирование извне произвольного сигнала на входе-выходе режима магистрали устройства 13, а воздействие через элемент И 23 низкого уровня на управляющие входы коммутаторов t6-20 приведет к закрытию последних. Таким образом, процессор оказывается в состоянии ожидания и находится в пассивном режиме слежения за системной магистралью до тех пор, пока каким- либо процессором системы не будет выполнена запись ожидаемого события (константы) в ту ячейку общей памяти, по адресу которой производится операция чтения этим ожидающим процессором. При этом соответ„

0

5

0

0

5

ствующий последнему триггер 35 благо- 5 даря срабатыванию компаратора 34 переключается в нулевое состояние, что снимает активный уровень на тактовом входе микропроцессора 15 я разрешает ожидающему микропроцессору закончить текущий цикл чтения.

Цикл записи блоками процессоров 1 в блок 4 общей памяти осуществляется традиционным способом.

Выше представлено описание реализации процедуры Wait при работе со спусковыми функциями процессором, получившем при этом разрешение от арбитра 5 системной магистрали.

В многопроцессорных конфигурациях каждый активный функционально однородный элемент - процессор, способный по собственной инициативе и асинхронно в системе выполнить поиск работы, реорганизацию управляю- 5 ксих таблиц, управляющей информации и обмен данными с общедоступными запоминающими устройствами, включает указанные функциональные узлы 1-3 и способен при обменах задать состояние управляющих системных входов-выходов.

В многопроцессорной системе для процедуры Wain реализованы совмещенные обмены типа Чтение-чтение и Чтение-запись. В обоих случаях пассивные процессоры - это процессоры, не завершившие операцию чтения общей памяти и находящиеся в состоянии ожидания из-за отсутствия ожидаемого

события или из-за ожидания захвата системной магистрали для выполнения данного обращения. При этом в блоке 2 каждого пассивного процессора на третьем выходе дешифратора 29 сформирован высокий уровень сигнала, являющийся управляющим сигналом соответствующей схемы 33 сравнения. В течение времени действия этого сигнала схемой 33 сравнения осуществляется сравнение кодов управляющих линий, а также адресных кодов. При совпадении указанных кодов, которое возникает при выполнении активным процессором обмена, аналогично требуемому пассивными процессорами, на выходе схемы 33 сравнения каждого такого процессора появится сигнал высокого уровня. Этот сигнал через эле

мент И 36 воздействует на единичный вход триггера 2t, устанавливает его в состояние лог. 1 и через элемент И 22 снимает активный сигнал на выходе запроса блока 1 (если он был установлен), а также совместно с сигналом входа-выхода готовности 14 через элемент И 37 определяет состояние синхровхода триггера 42. В зависимости от информации, считываемой (совмещенный обмен Чтение-чтение) или записываемой (совмещенный обмен Чтение-запись) активным процессором в каждом пассивном процессоре, участвующем в таком обмене, с помощью триггера 35 в случае отсутствия ожидаемого события осуществляется подтверждение ранее установленного состояния ожидания микропроцессора, а в случае появления ожидаемого события (уровень лог. О на выходе компаратора 34) совместно с низкими уровнями выхода запроса и входа-выхода 14 готовности устройства обеспечивается отсутствие сигнала актив ного уровня на тактовом входе микропроцессора, что разрешит последнему закончить текущий цикл чтения.

Формула изобретения Микропроцессорная система, содержащая п процессоров, блок общей памяти, арбитр системной магистрали, причем информационные входы-выходы всех процессоров соединены с одноименным входом-выходом блока общей памяти и является одноименным входом-выходом устройства, адресный вход-выход которого соединен с адресным вхо0

5

0

0

5 с

дом блока памяти и с адресными выходами всех процессоров, входы-выходы Чтение-запись которых соединены с входом режима блока памяти и являются входом-выходом Чтение-запись устройства, вход-выход Обращение к памяти которого соединен с одноименным входом блока памяти и с одноименными входами-выходами всех процессоров, выходы Обращение к внешнему устройству которых объединены и являются одноименным выходом устройства, первые и вторые входы синхронизации которого соединены соответственно с первыми и вторыми синхронизирующими пходами всех процессоров, нходы-знходы Чахват магистрали которых соединены и являются входом-выходом Захват магистрали устройства, вход-ныход готовности которого соединен с одноименным выхо- ,дом блока памяти и с одноименным входом всех процессоров, выходы запроса и входы Разрешение на захват магистрали которых соединены соответственно с одноименными входами и выходами арбитра системной магистрали, отличающаяся тем,

5

0

что, с целью увеличения производительности за счет уменьшения интенсивности обращения процессоров многопроцессорной системы к общей шине при работе со спусковыми функциями, в нее введены п блоков системных операций и п блоков запуска, причем первый, второй и третий управляющие выходы 1-го процессора (где i 1,...,п) соединены соответственно с управляющими входами 1-го блока системных операций, адресный вход которого соединен с первым адресным входом 1-го блока запуска и с адресным выходом микропроцессора 1-го процессора, информационный выход которого соединен с информащ-юнным входом 1-го блока системных операций и с вторым адресным входом 1-го блока запуска, входы кода спусковой функции, 0 параметра спусковой функции, признака соединены соответственно с одноименными входами 1-го блока системных операций, выходы совпадения и ожидания 1-го блока запуска соединены соответственно с одноименными входами 1-го процессора, входы синхронизации Готовности, Кода, Обращение к памяти и третий адресный вход 1-го блока запуска соединены соответственно с вторым входом внешней синхронизации, с входом-выходом готовности, информационным

15

21

%

jfrt

входом-выходом, входом-выходом Обращение к памяти, с адресным входом-выходом устройства.

Ј

-

30

U

в

16

-

-Им |W

JL

jfrt

ч

-

Фиг. 2

L

®UeM

Составитель Г.Смирнова Редактор Н.Гунысо Техред л.ОлийныкКорректор л.Патай

-н

JO

Шиг.З

| Многопроцессорная вычислительная система | 1985 |

|

SU1277129A1 |

| Устройство для крепления плоской подушки в платформенных весах | 1928 |

|

SU32182A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

Авторы

Даты

1991-05-07—Публикация

1989-05-22—Подача