Иэобретение относится к автоматике и вычислительной технике и может быть использовано в цифровых системах управления, в частности, при построении программируемых контроллеров.

Целью изобретения является расши- рение функциональных возможностей за счет обеспечения одновременной независимой работы по двум магистралям и повышение производительности

Это позволяет рационально и эффективно использовать процессоры с 8- и 16-разрядными шинами данных, подключая их к разным магистралямо При этом появляется дополнительная возможность вести параллельную обработку данных на локальной шине и осуществлять одновременно сбор и выдачу информации от периферийных устройств по системной шине„

Подключение магистралей и их взаимное объединение осуществляется программным способом. Наличие возможности групповой пересылки массива данных между системной и локальной магистралями в монопольном режиме существенно повышает быстродействие обмена, сокращает время реакции по любой из магистралей,

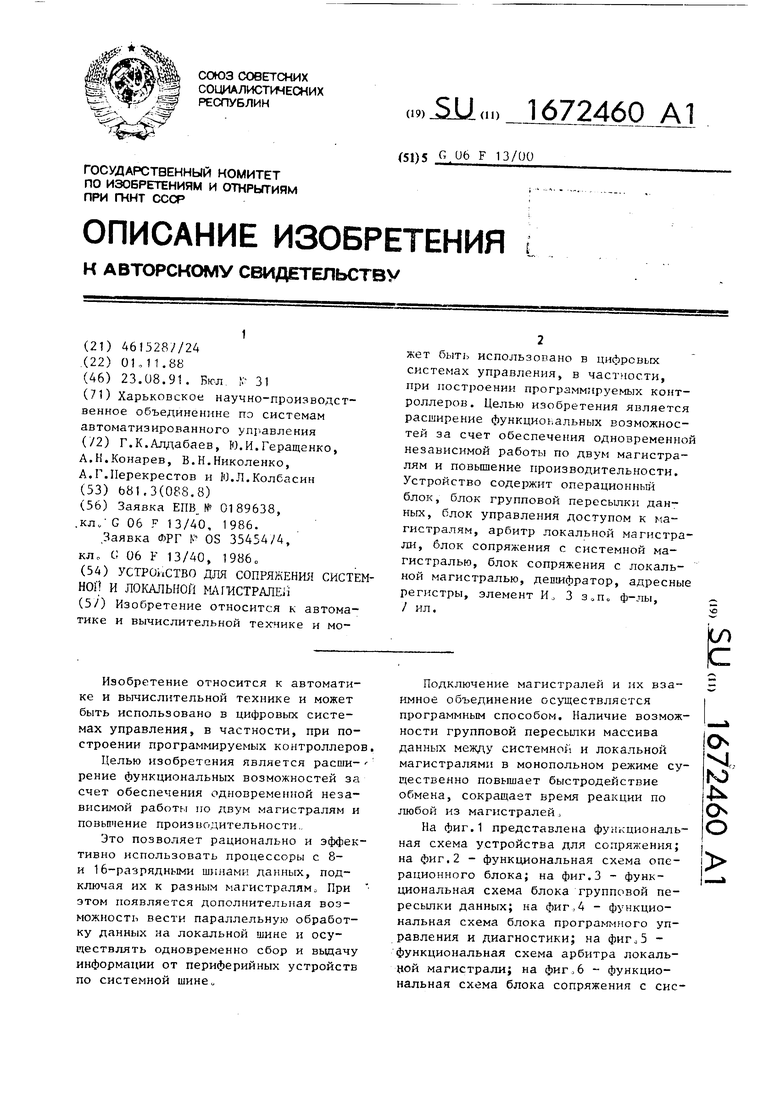

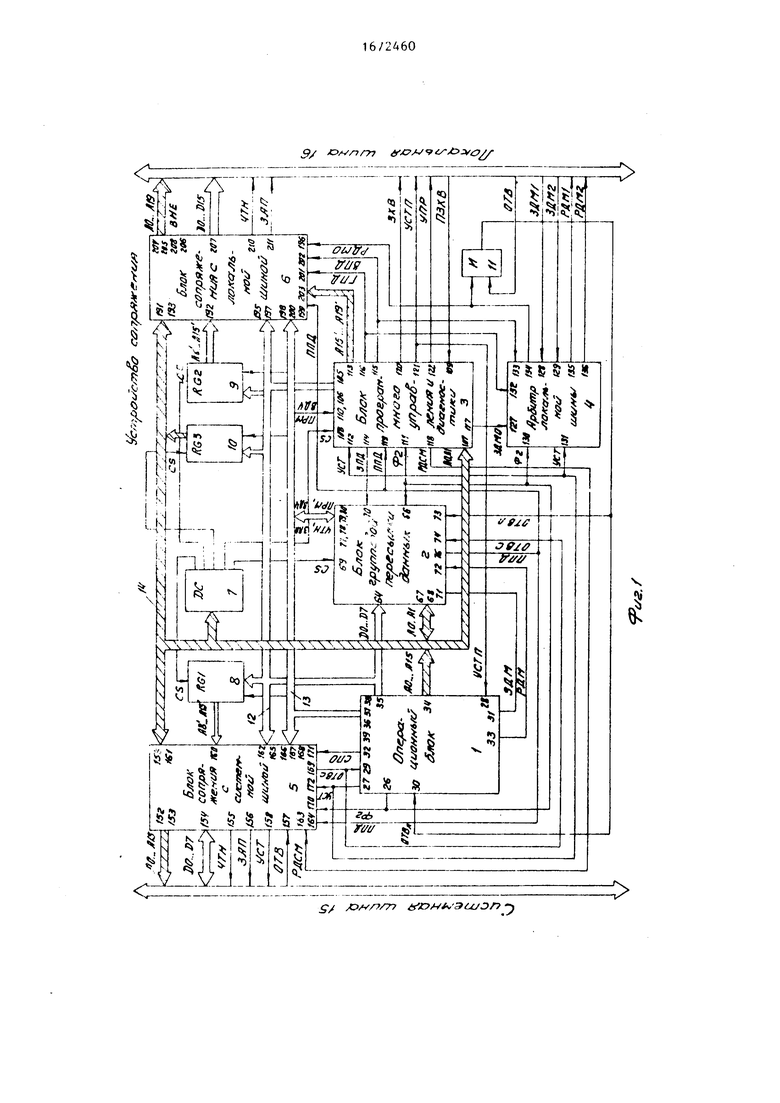

На фиг.1 представлена функциональная схема устройства для сопряжения; на фиг.2 - функциональная схема операционного блока; на фиг.З - функциональная схема блока групповой пересыпки данных; на фиг Л - функциональная схема блока программного управления и диагностики; на фиг.З - функциональная схема арбитра локальной магистрали; на фиг,6 - функциональная схема блока сопряжения с сиеО

ы

КЗ

о о

темной магистралью; на фиг / - функ- циональная схема блока сопряжения с локальной магистральюс

Устройство содержит операционный блок 1, блок 2 групповой пересылки данных, блок 3 управления доступом к магистралям, арбитр 4 локальной магистрали, блок 5 сопряжения с системной магистралью, блок 6 сопряжения с локальной магистралью, дешифратор /, первый 8, второй 9 и третий 10 адресные регистры, элемент И 11, внутренние шины: информационные 1 2, управления 13, адресные 14, системную ма- гьстраль 15 и локальную магистраль 16 Шины 12Сс,14 образуют внутреннюю магистраль с

Операционный блок 1 подключен адресными 14, информационными 12 и уп- равляюррчми 13 винами к внутренней магистрали, к КОТОРОЙ подключены блок 5 сопряжения с системной магистралью и блок 6 сопряжения с локальной ма- гистралькп

Нлок 5 сопряжения с системной магистралью своими адресными, информационными и у фазлякячими шинами т тения, записи, ответа и установки соединен с с- темной магистралью 15

Нлок 6 сопряжения с лекальной магистралью своими адресными, информационными и управляющими пиюми чтения и записи соединен с локальной магистралью 16.

Вход дешифратора / соединен с адресными тинами 14 внутренней магистрали, а выходы дешифратора соединены соответственно с входами выбооки (CS) первого 8, второго 9 и третьего 10 регистров, лока 2 групповой пересылки данных и блока 3 программного управления и диагностики.

Блок 2 групповоА пересылки данных соединен с внутренней магистралью устройства (шины 12-14) адресными АО1,..А/ , информационными DO . .,D7 и управляющими шинами чтения (ЧТН), записи (3AJO , двунаправленным шинами Прием (ПРК) и Выдача (ВДЧ).

Шинами запроса (ЗДМ) и разрешения РДМ) доступа к магистрали бЛ Ж 2 групповой пересылки данных соединен с операционным блоком 1„ Выход сигнала подтверждения прямого доступа (ПЦЦ) соединен с аналогичными входа- ми блоков сопряжения с системной магистралью 5, сопряжения с локальной магистралью Ь и программного урав

5

0 5

0

Q

с Q

с

5

ления и диагностики 3- Выходы адресных сигналов и входы АО и А1 соединены с соответствующими разрядами внутренней адресной шины 14. Вход сигнала выборки CS соединен с одним из выходов дешифратора /„ Вход тактовой частоты Ф2 соединен с соответствующими входами блоков сопряжения с системной магистралью 5 и программного управления и диагностики 3, арбитром локальной магистрали 4 и соответствующим выходом операционного блока 1 о Вход сигнала ответа от системной магистрали (ОТВс) соединен с соответствующим входом операционного блока 1 и аналогичным выходом блока 5 сопряжения с системной магистралью. Выход сигнала ответа от локальной магистрали (ОТВл) соединен с соответствующим входом операционного блока 1 и выходом этого же сигнала с элемента И 11„ Вход сигнала Запрос прямого доступа (ЗПД) соединен с вьгходом этого же сигнала блока 3 программного управления и диагностики

Блок 3 своими адресными выходами А15 „„оА19 соединен с входами аналогичных сигналов блока 6-, Выходы групповой (1ТЩ) и внутриблочнон (ВГЩ) пересылки соединены соответственно с аналогичными входами арбитра 4 и блока 6. Выходы сигналов Захват (ЗХВ), Программный перезапуск (УСТП), Управление (УПР) и вход сигнала Подтверждение захвата (ПЗХВ) соединены с локальной магистралью 16, а выход сигнала УСТП соединен с входом операционного блока 1 „

Выход сигнала Запрос доступа к магистрали (ЗДМО) соединен с входом арбитра 4. Выход сигнала Разрешение доступа к системной магистрали (РДСМ) соединен с входом блока 5. Вход сигнала установки (УСТ) соединен с аналогичными входами арбитра 4, блока 5 и выходом операционного блока 1.

Операционный блок 1 управляет работой системной магистрали 15, локальной магистрали 16, а также устройства сопряжения в соответствии с программой хранимой в его памяти.

Блок 2 групповой пересылки данных осуществляет пересылку массива данных в монопольном режиме между системной и локальной шинами, а также -рупповую пересыпку массива данных из памяти операционного блока f на одну из внешних магистралей устройства (системную или локальную), и наоборот.,

Влок 3 позволяет программным образом расширять адресное пространство локальной магистрали, изменять режимы работы системной и локальной шин, выполнять функции формирования диагностических сообщений.

Блоки 5 и b сопрягают устройство по электрическим и логическим условиям соответственно с системной 15 и локальной 16 магистралями„

Дешифратор / адреса осуществляет выборку функциональных узлов устройства по адресному принципу„

Арбитр 4 позволяет по приоритету подключать, например, до трех активных микропроцессоров к локальной магистрали 16.

Регистры 8-1,0 адреса используются для формирования старших разрядов адреса А8 o.oAIS пересылаемых блоком 2 массовой данных при пересылке массива информации из одной магистрали на другую, и наоборот, а также при пересылке массива данных из памяти операционного блока 1 на одну из внешних магистралей (системную 15 или локальную 16), и наоборот, из внешних магистралей 15 и 16 в память операционного блока 1,

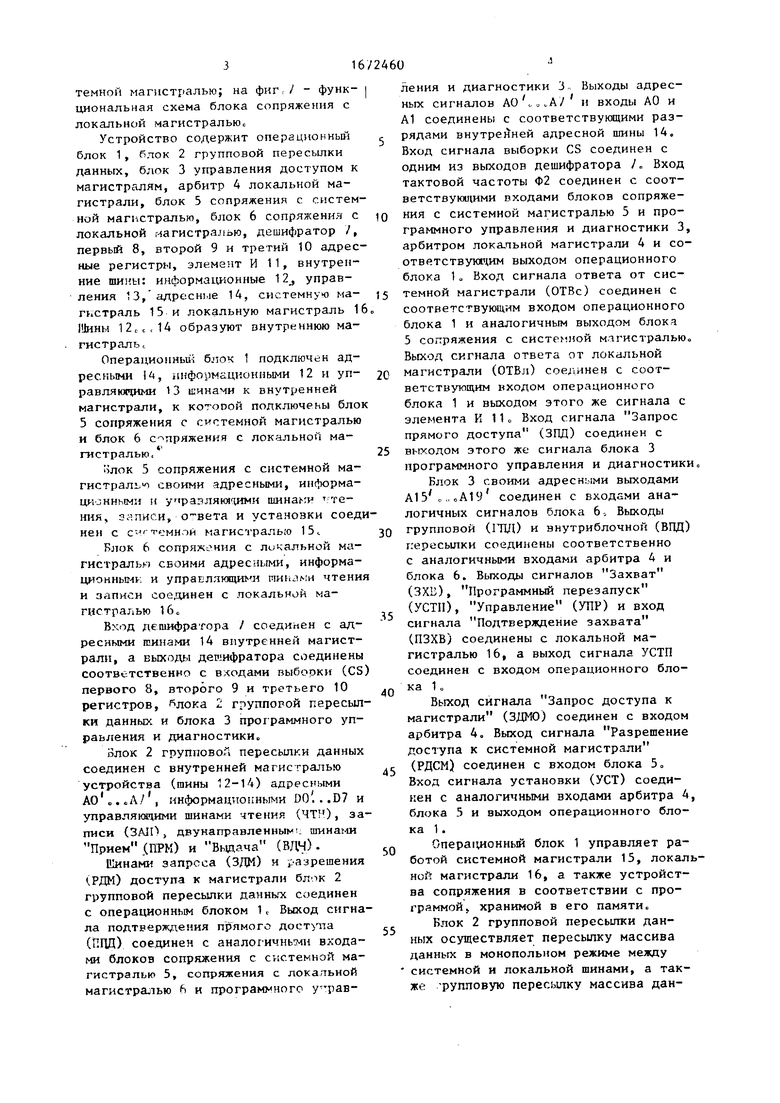

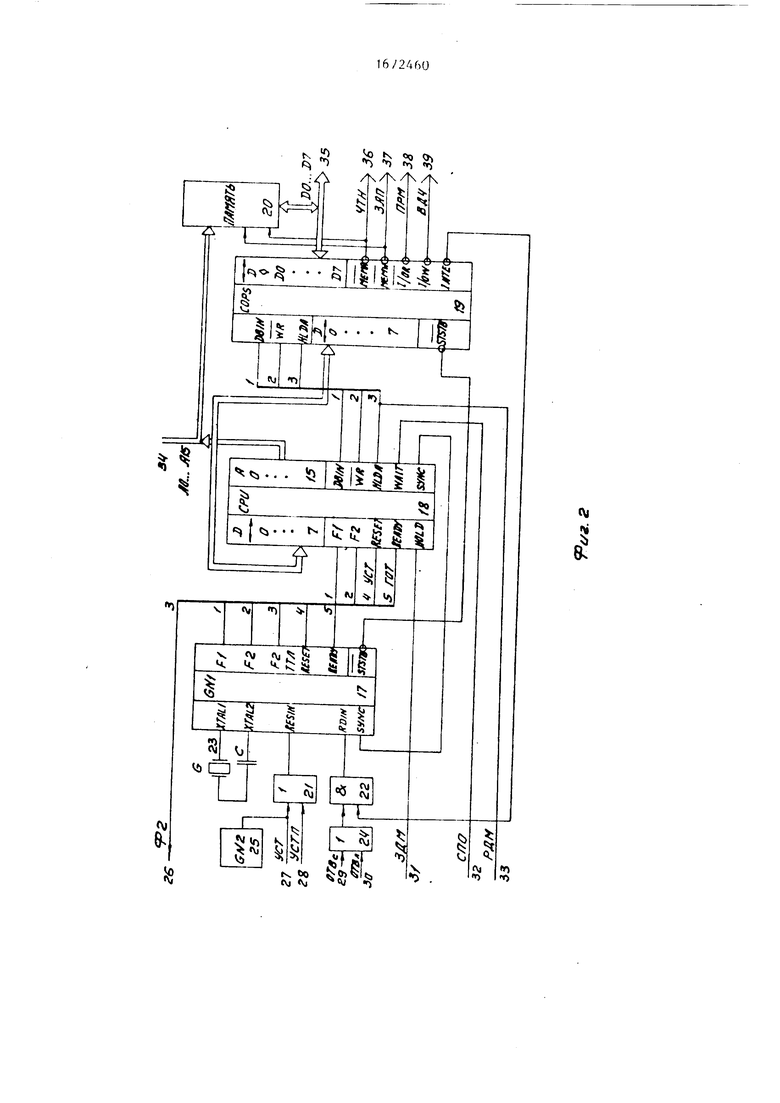

Операционный блок (фиг„2) содержит генератор 1/ тактовых сигналов (например, микросхема КР580/Ф2А), микропроцессор 18 (например, микросхема КР580ИК80А), системный контроллер 19 (например, микросхема КР580ВК28), память 20 (например, микросхема К537РУ1U), первый элемент ИЛИ 21, элемент И 22, генератор 23, второй элемент ИЛИ 24 и формирователь 25 одиночных импульсов по включению питания. Позициями 26,ot39 обозначены входы и выходы операционного блока 1.

Адресные шины АО о„0А15 микропроцессора 18 подключены к выходу 34 блока и к адресным входам памяти 20„ Двунаправленные шины данных DO.JOD7 микропроцессора 18 через системный контроллер 19 подключены к информационному выходу-входу 35 и информационным шинам памяти 20„

Выходы сигналов Прием, Выдача, Подтверждение захвата микропроцессора 18 соединены с соответствующими входами системного контроллера 19,

0

0

5

который соответствующими выходами ЧТН ЗАП, ПРМ и ВДЧ соединен соответственно с. выходами 36 - 39 операционного блока о Выходы ЧТН и ЗАП системного контроллера, кроме того, подключены к соответствующим входам памяти 20 0

Входы сигналов тактовой частоты, установки, готовности микропроцессора 18 соединены с соответствующими выходами генератора 17 тактовых сигналов.

Вход сигнала НО микропроцессора 18 соединен с входом 31 блока, выход сигнала Ожидание - с выходом 32 5 блока, выход сигнала Синхро - с вхо- дом этого же сигнала генератора 17 тактовых сигналов„

Выход сигнала Разрешение прерывания системного контроллера 19 соединен с одним из входов элемента И 22, второй вход которого подключен к выходу элемента ИЛИ 24„ Входы элемента ИЛИ 24 соединены соответственно с входами 29 и 30 операционного блока На вход 29 поступает сигнал ответа (ОТВс) от системной шины, на вход 30 - сигнал ответа от локальной пшны (ОТВл)о Выход элемента И 22 соединен с входом готовности генератора 1/ тактовых сигналов

Вход сигнала Строб состояния системного контроллера 19 соединен с соответствующим выходом генератора 1/ тактовых сигналов. Выход сигнала Подтверждение захвата микропроцессора 18 соединен с выходом 33 блока и с входом соответствующего сигнала системного контроллера 19 о

Выход формирователя 25 одиночных импульсов по включению питания соединен с одним из входом элемента ИЛИ 21 и выходом 21 блока. Второй вход элемента ИЛИ 21 подключен к входу 28 блока, на который подается сигнал 5 УСТ1Ь

Установочный выход генератора 1/ тактовых сигналов соединен с соответствующим входом установки микропроцессора 18„ Выход тактовой частоты (ТТЛ) генератора 1/ тактовых сигналов соединен с выходом 26 операционного блока0

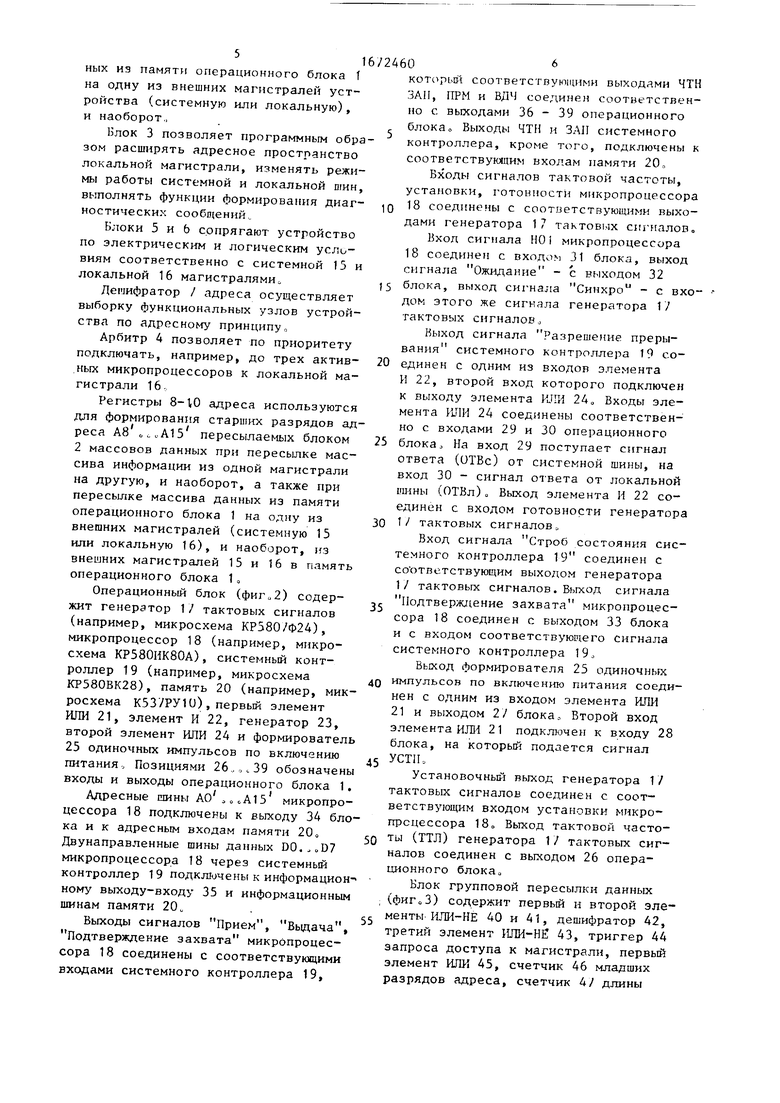

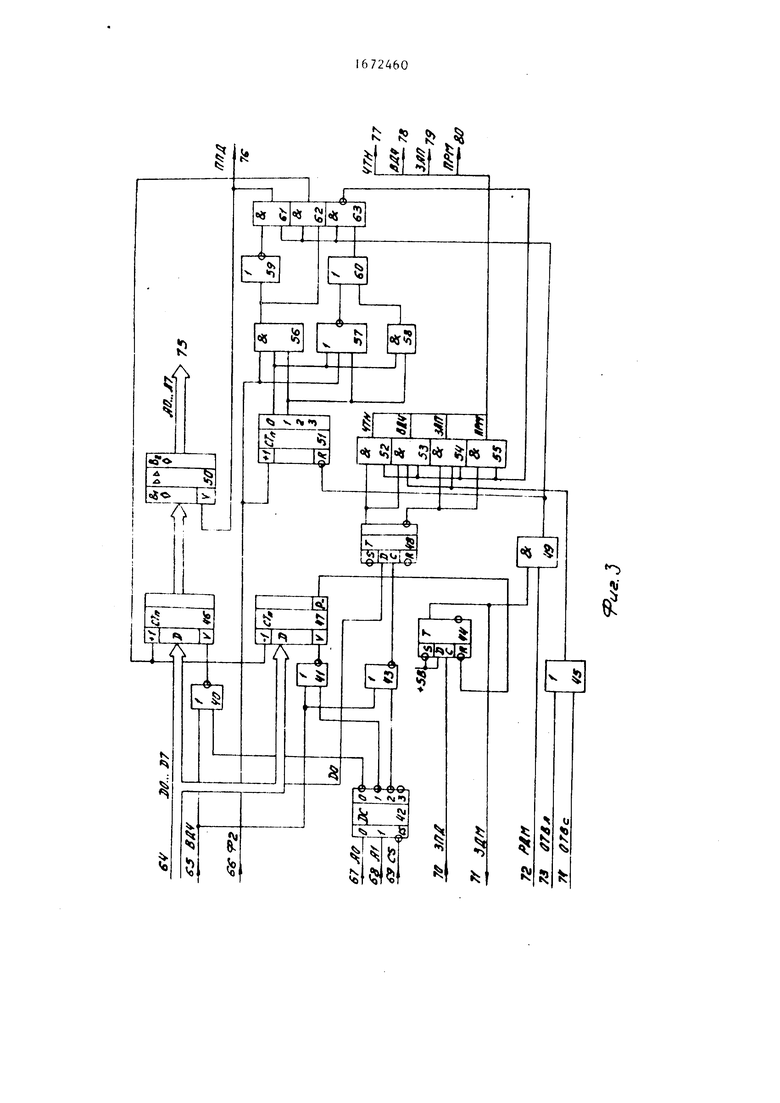

Блок групповой пересылки данных (фиг,3) содержит первый и второй элементы ИЛИ-НЕ 40 и 41, дешифратор 42, третий элемент ИЛИ-НЁ 43, триггер 44 запроса доступа к магистрали, первый элемент ИЛИ 45, счетчик 46 младших разрядов адреса, счетчик 47 длины

0

5

0

0

5

массива, триггер 48 режима работы, первый элемент И 49, магистральный усилитель 50, счетчик 51 управления, второй, третий, четвертый и пятый элементы И 52. 55, шестой элемент И ЬЬ, четвертый элемент ИЛИ-НЕ 5/, седьмой элемент И 58, элемент НЕ 59, второй элемент ИЛИ 60, восьмой и девятый элементы У 61 и И 62 и зиемент И-НЕ 63. Позициями (4,..С80 обозначены зходы IT выходы блока 2 групповой нерись пки данных с

Счетчик 4ь используется для формирования младн их разрядов адреса при групповой пересылке, счетчик 4/ - для определения конца передачи массива данных, счетчик Ы - для формирования временной диаграммы управления групповой пересылки массива данных, Дешифратор 42 используется для выборки псртоп правления счетчиков 46 и 4/ и триггера 48 при обращении к блоку 1. со стороны операционного блока 1

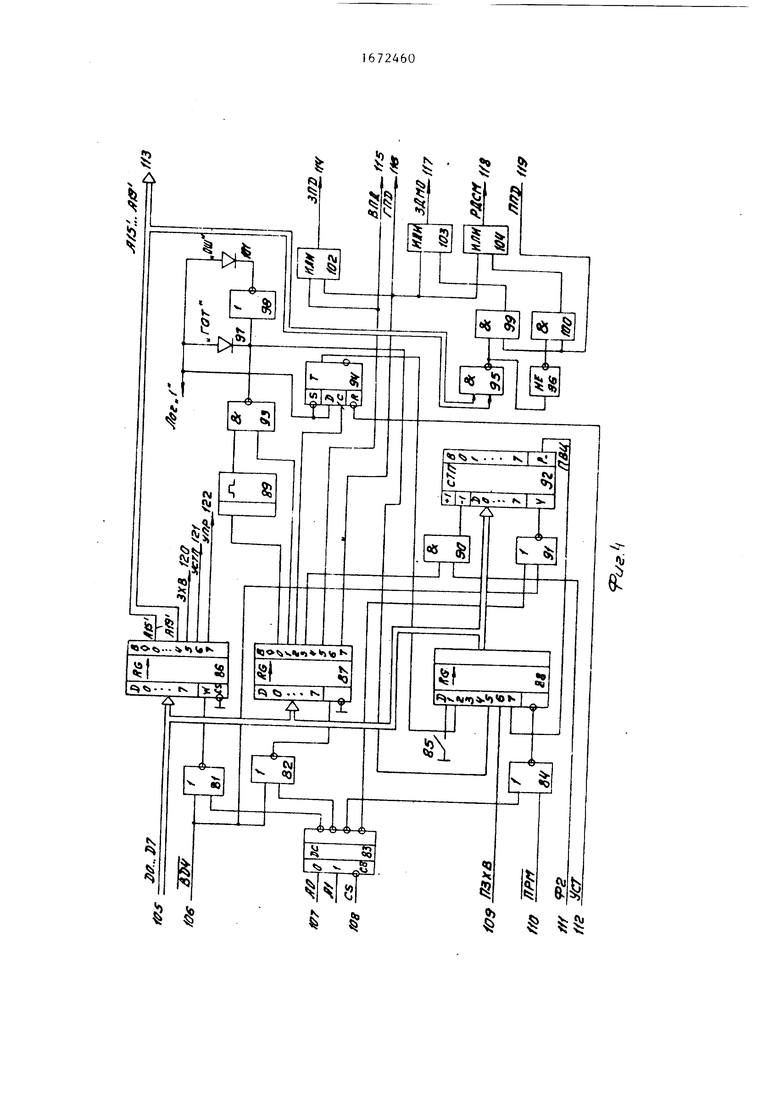

Члок } управления доступом к ма- гистрачям .Фиг,4) содержит первый 81 и чторои 8 элементы ИЛИ-HF, дешгфра- тлр HJ, тр-x-ui элемент ГЛИ-ИИ 84, пе ректх г п . Ль У5 режкмор работа - отладка гто1 mi H Ьо, второй 87 и третий 88 рггг .-. ры. однсниСфитог 89, первый Э Ь 9о, 1ет ертый элемент ИЛИ- НЕ i , счэтчнк 92, первый элемент И-НЕ УЗ, триггер 94 установки в ис- ходиА.е состояние, второй элемент И-НЕ gr, i элемент НЕ 46, светодиод - / гсгозно(тк (ГОТ), второй элемент rlii 98, агорой 9 } и третий 100 элемен- т И, светодиод 101 отказа (ошибки OLliJ первый 102, второй 103 и третий 104 элементы ИЛИ. Позициями 105.122 о О- начены входы и выходы блока 3 программного угшавл чия и диагностики

Регистр 8Ь ислользуется для расширения адресного пространства локаль- лой шины л хранения команд управления , yLTi;, Речист 31 и -пользует ся д. -ь ко трспл и дчаг мостили работы операционного блока, контроля за длительностью времени цикла сканирования раб, программы отерад -..ьным блокам формч / ч)аи5 и чндигацл-i сигналов ГптоЬ - л i а Ошибка, формирования признаков гру.товой (ПЭД и вкутри- баочной (Bi, О перес.лыки данных Регистр 88 преднязначен для здания ргжнмоз работы устройстваs передачи диагног, i1 зсчих сообщ нед в операционный f 1OV „

5 0

(,

5

Счетчик 92 предназначен для контроля длительности времени цикла сканирования программы операционным блоком

Дешифратор 83 осуществляет выборку одного из регистров 86tll88 или счетчика 92 в зависимости от состояния адресных сигналов АО и А1 на входе 10/„

Элементы ИЛИ-НЕ 81, 82, 84 и 91 вы- выполняют функции И по низким уровням сигналов ВДЧ и одного иа выходов дешифратора 83. Триггер 94 установки в исходное состояние однозначно определяет причину устаногки устройства в исходное состояние сигналом УСТ Установка (УСТ) или сигналом Программный перезапуск(УСТП).

Одновибратор 89 предназначен для слежения за работой микропроцессора Это достигается путем анапи- а воздействия на одновибратор запускающих импульсов, формируемых операционным блоком 1 в каждом цикле программы и выдаваемых косвенно по шинам данным DO..D7 в сопровождении управляющего сигнала ВДЧ. Подтверх;щ нием переза- ггуска ицнонибратор 1 является съем сигнал состояния триггера перезапуска по шинам данным b0.0D7 по управ- ичяадему сигналу ПР в случае правильной работы микропроцессора операционного блока 1.

Элемент И-НЕ 95 формирует признак выбора магистрали. Элементы И 99 и ИЛИ 103 формируют сигнал запроса доступа к локальной шине (ЗДМО) на выходе 11/. Элементы НЕ 96, И 100 и ИЛИ 104 формируют сигнал разрешения доступа к системной магистрали (РДСК) на выходе 118. Элемент ИЛИ 102 формирует сигнал Запрос прямого доступа (ЗПД) на выходе 114 при наличии признаков групповой (ГПД) и внутриблоч- ной (ВПД) пересылки данных

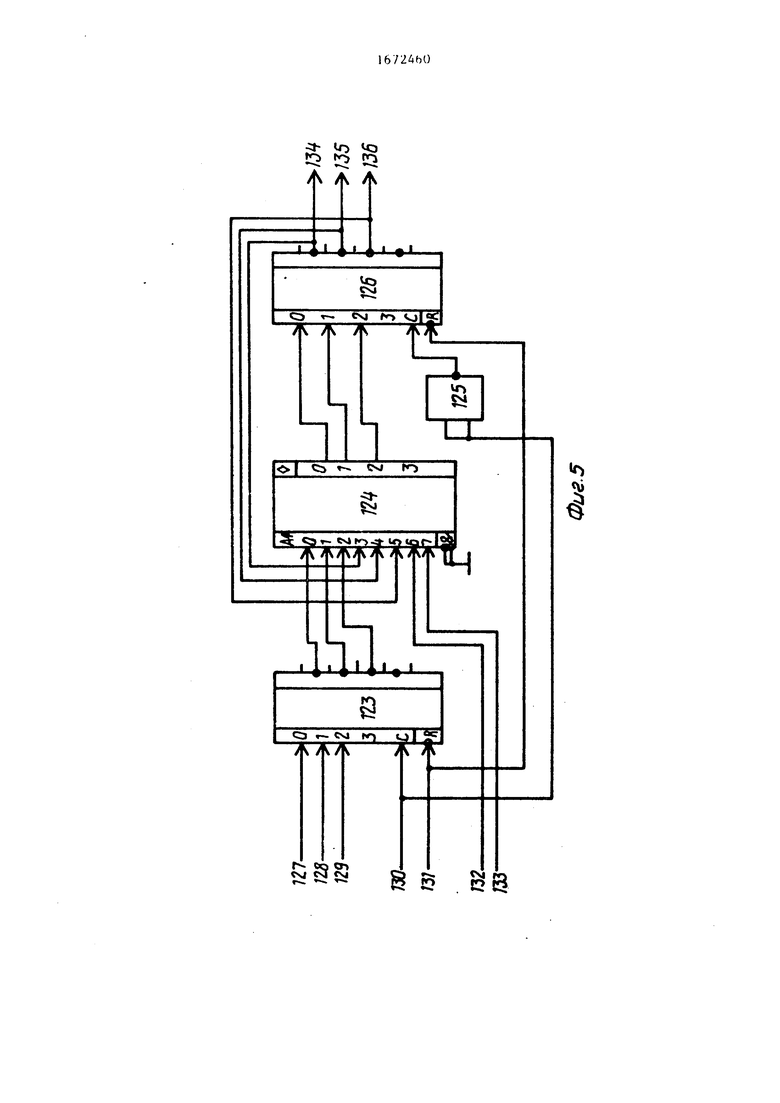

Арбитр (фиг,5} содержит первый регистр 123, приоритетный шифратор 124, элемент НЕ 125 и второй регистр 126, Позициями 12/ос с 136 обозначены вхоцы и выходь; арбитра локальной шиныАрбитр 4 предназначен для устранения конфликтных ситуаций на локальной магистрали при одновременном обращении к Ней нескольких активных микропрочессорой(напримерs до 3 микропроцессоров одновременно)L

Регистр 123 предназначен для занес шя еостгяний сынслов запросов

доступа к магистрали для их дальнейшей обработки Фиксация состояний необходима для устранения гонок в процессе обработки.

Приоритетный шифратор 124 реализует все возможные комбинации выходных сигналов, обеспечивая приоритетность входных сигналов и их однозначный выход

Регистр 126 фиксирует выходной сигнал, исключая1 ложные появления выходных сигналов в момент изменений состояния входного регистра.

Элемент НЕ 125 позволяет осуществ лять занесение информации в регистры 123 и 126 в противофазе.

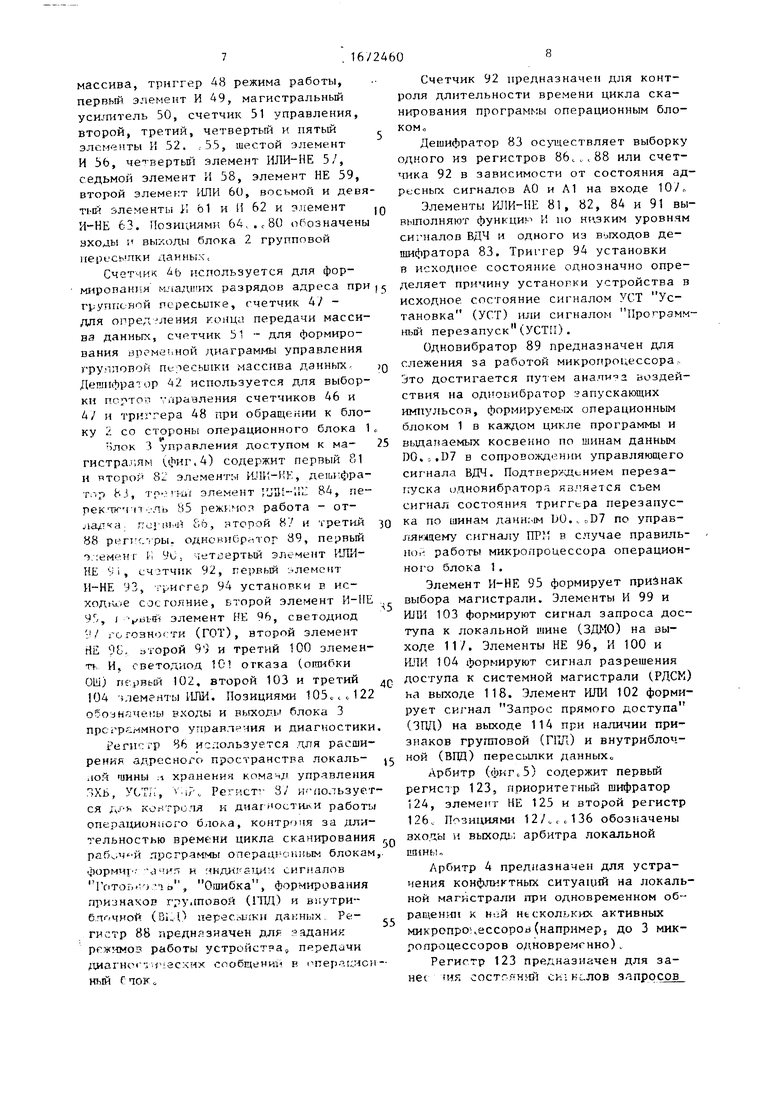

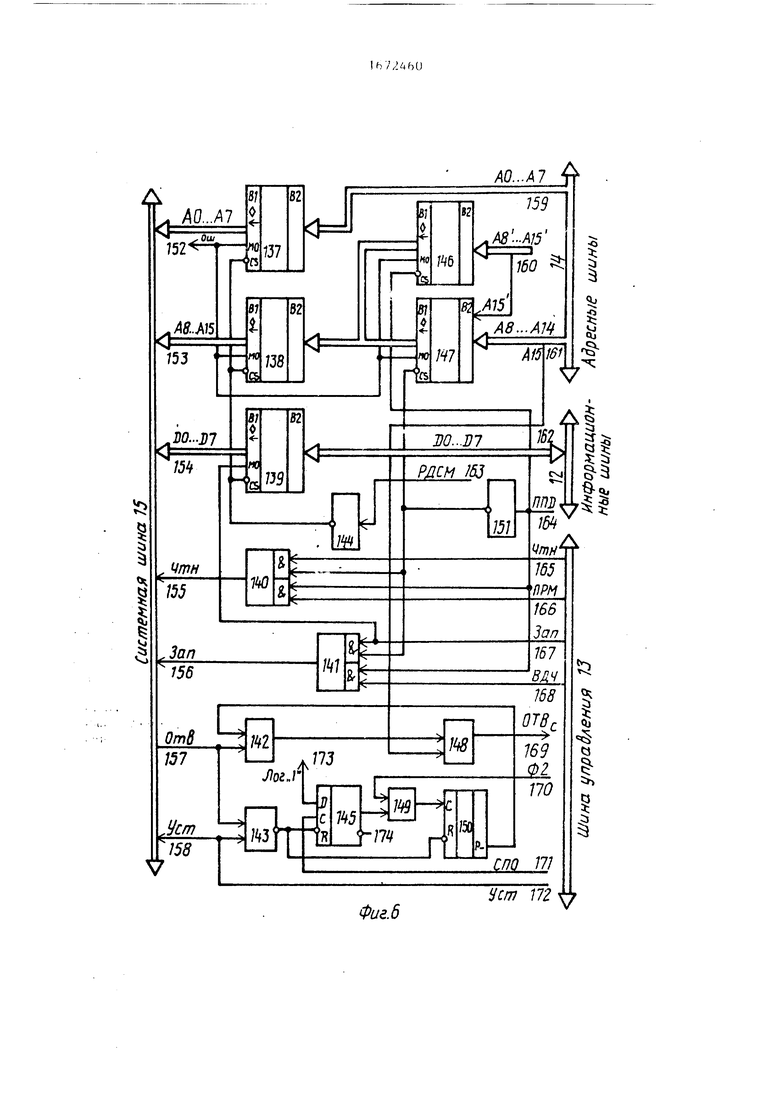

Блок 5 сопряжения с системной магистралью (фиг.6) содержит первый и второй магистральные усилители 13/ и 138 адресных сигналов, двунаправленный магистральный усилитель 139 информационных сигналов, первый и второй элементы 2И-КЛИ 140 и 141, первый и второй элементы КЛК 142 и 143, первый элемент НЕ 144, триггер 145, третий и четвертый магистральные усилители 146 и 14/ адресных сигналов, первый 148 и второй 149 элементы И, счетчик 150 и второй элемент НЕ 151„ Позициями 152с о о 1/4 обозначены входы и выходы блока

Однонаправленные магистральнле усилители адресных сигналов предназначены для коммутации адресных сигналов с внутренней адресной шины на системную „ Двунаправленные магистральные усилители информационных сигналов предназначены для коммутации данных с внутренней магистрали на внешнюю системную шину и, наоборот с системной шины на внутреннюю информационную шину

Элементы 2И-ИЛИ 140 и 141 и элемент НЕ 151 предназначены для коммутации управляющих сигналов.ЧТН и ЗАЛ на системную шину при отсутствии сигнала ПОД на входе 166„ При наличии этого сигнала на системную шину поступают сигналы ПРМ (вход 166) на БДЧ (вход 168)о

Элементы ИЛИ 142 и 143, триггер 145, элементы И 148 и 149 и счетчик 150 предназначены для формирования сигнала ОТВ на выходе 169 при наличии его на входе 157 блока. При отсутствии сигнала ОТВ на входе 15/ в течение установленного интервала времени производится искусственное его

0

0

5

з

0

5

0

0

5

формирование элементом ИЛИ 143, триггером 145, счетчиком 150 и элементом II 149Выходы магистральных усилителей

137и 138 адресными шинами АО .„„А7 первьр и А8 ,А15 второй соединены с системной шиной, а адресные входы первого подключены к адресным ji/инам внутренней магистрали, адресные входы второго магистрального усилителя

138соединены с соответствующими выходами магистральных усилителей 146 и 14/0 Вход магистрального усилителя 146 соединен с входом 160 блока,вход магистрального усилителя 147 - с входом 161 блока. Двунаправленный магистральный усилитель 139 данных подключен к системной шине выходом 154 и к внутренней шине данных входом 1б2„

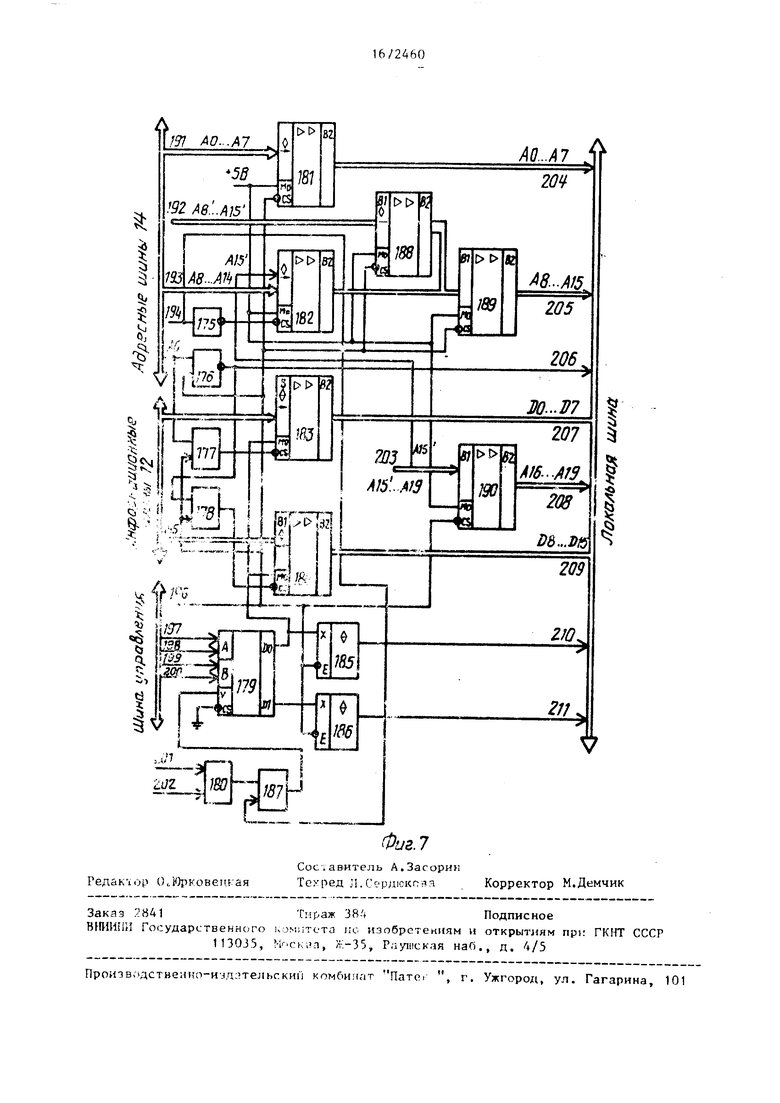

Блок b сопряжения с локальной магистралью (фиг,/) содержит элемент НЕ 1/5, первый 1/6, второй 17/ и третий 1/8 элементы И, мультиплексор 1/9, элемент ШТИ 180, первый 181 и второй 182 однонаправленные усилители адресных сигналов, первый 183 и второй 184 двунаправленные магистральные усилители, первый 185 и второй 186 выходные усилители, четвертый элемент И 18/, третий 188, четвертый 189 и пятый 190 однонаправленные усилители адресных сигналов Позициями 191,„ о 211 обозначены входы и выходы блока 6„

Однонаправленные магистральные усилители 181, 182, 188, 189 и 190 адресных сигналов предназначены для коммутации адресных сигналов АО „„„ А19

с внутренней адресной магистрали на локальную шину„ Младшие разряды адреса АО 000А/ , поступающие на вход 191, передаются с помощью магистрального усилителя 181 на выход 5 204. Старшие разряды А8 0,оА15 передаются с входа 193 через магистральные усилители 182 и 189 при отсутствии сигнала ПОД на входе 194, формируемого элементом НЕ 1/5, на выход 205„

При наличии сигнала ППД на входе 194 старшие разряды адреса передаются с входа 192 на выход 205 через магистральные усилители 188 и 189„ Магистральный усилитель 190 расширяет адресное поле локальной шины. Адресные сигналы А15 «, о оА19 поступают на вход 203 и коммутируются на выход 208 при наличии разрешения сигнала

РДМ 1 на 1ЦЬ. Двунаправленные магистральные ус и питали 1 Г 3 и 184 коммуrupv i 8-разрядч гю нн реннюю шин данных (вход 1Ч54 на 16-разряд- чл о шину дгннмх )Uov i 7 (выход 2 / ) и D. „D15 (выход 2и9) Подключение мпа/iLJt ro ил 1 парного паи га данных на локальную осуществляется элементами И 11 и 1/Чс

bTHincK -op 1/q, вых )дчые уси- ш-ели 1 5е) и 186, пементъ, ИЛИ 180 и И i8/ о г vi v г лчякп коммутацию управляющих (Hii. ЧТИ, ЗАП. ПРИ и ВДЧ на локальну-i шину

vCTpoucrBo дп сопряжения работает н сле умцих реким х обмена информацией между магистралями: передача информации с системном тины на ло- кальну 1 и наоборот, передача информа- ции с систе; HI иины на внутреннюю памят.. o7it i ацчонно с блока и наобо- ро1, пег сдача информяции с локальной на 4hv 1ррннк ю памяти операционного блс xJ и наэСороГс

Начичие независимых магистра- 1ей - системней (с 8-раз;ядной шиной ца мы ч i ;, ччы ий с 16 разряднсй иьс и д.ынь л) ю ьопяет организовать оди - врс . чч траЧ тк цат.ных по локальной члчс ч ( ip и накоппер ие 1cin -,,(х ;i j.i iHi-i 1«не, Объединение . °иг геиной шин ос щесгв- чтотс т пргл г. -№ но путем наст 1Йки бл на nport я- мь г о /прявления и ди.и- пост1 кн гп соответствукчций режим Уп- 1 1глериЕ обском осуществляется бло- лл, i ,,( пересылки данных в со- ОТЙРТГВНЬ заданием, предварительно занесен ым ь .iero операционным блгкг м

Групп ,«. пересиг-а массива данных по ноляет значительно повысить быстродействие счот автоматического формиров, иия текущеп адресе, и авто- маг«-гческог о Лорнирования к «па массива п. pec IP ем v дан jix

Обмен Hhcjop iaiineft магистралями осуществляете следующим of аэом

Микропроцессор операционного блока я соответствии с хранимой в памяти программой астраирает блок программ Hi.ro управления и диагностику на со- ответствучтций аид групповой пересылки

Информация в блок пересылается по внутренним шинаи данных DCb.bD7 в сопровождении управляющего сигнала ВДЧ, После занесения управляющего слота в бпок программного управления

и диагностики локальная и системная магистрали подготавливаются к обмену. В блок групповой пересылки данных заносится управляющее слово, содержащее длину массива, а в буферные регистры заносятся начальные адреса пересылаемого массива состемной и локальной магистралей и -выставляется сигнал запроса доступа магистрали (ЗДМ) в опе- рщионный блок

Микропроцессор операционного блока входит в режим Захват, по которому адресные, информационные и управляющие сигналы отключаются от внутренней магистра/В При этом формируется сш- нал разрешения доступа магистрали (РДМ), поступающий в блок групповой пересылки данных, по которому адресные, управляющие и шипи данных подключатся к внутренним магистратам, В дальнейшем управление внутренней магистралью осуществляет блок групповой пересылки данных. Выполняется групповая пересылка массива данных в соответствии с заданием, хранимым в блоке групповой пересь -ки данных. После выполнения пересылки массива данных блок групповой пересилки цанных от- клютгается от внутренней магистрали н управление передается операционному блоку путем снятия сигнала захвата (ЗДМ). Операционный блок отключается от системной и локальной магистралей , Каждая магистраль переходит в автономную работу. На локальной шине осуществляется параллельная, управляемая арбитром, обработка полученной при пересылке информации, на системной шине - сбор и накопление полученной от объекта информацииt

При включении питания операционный блок 1 устанавпинается в исходное состояние внутренним сигналом установки (УСТ), формируемым форми- пователем 25 () По сигналу УСТ микропроцессор 18 (фиг.2) устанавливается в исходное состояние по цепи: вход 2/ элемента ИЛИ 21, вход RESIN генератора 1/, выход РЕЬЬТ генератора 1/, вход PESET микропроцессора 18 В программный счетчик микропроцессора заносятся нули, и микропроцессор обращается к памяти 20 (фиг„2) с нулевым адресом Память предназначена для хранения рабочей программы управления объектом В соответствии с алгоритмом работы программы, записанной в памяти, oneрационный блок 1 (фиг.1) обращается к различным блокам устройства, передавая им или принимая от них информацию,, При этом на шине 14 микропроцессор операционного блока 1 формирует адресные сигналы ACh. „„A15, соответственно с которыми дешифратор / формирует признак обращения к одному из внутренних блоков. На внутренней шине 13 операционный блок 1 формирует сигналы ЧТН, ЗАЛ, ПРМ, ВДЧ. По внутренней информационной шине 12 производится обмен данными между блоками устройствао При этом необходимо согласовать между собой быстродействие операционного блока 1 и других блоков устройства. Для этого после каждого обращения операционного блока 1 к другим блокам он переходит на анализ сигнала Готовность, который поступает от магистрали 15 через блок 5 в виде сигнала ОТВс на вход

29операционного блока при обращении

к системной магистрали или поступает от локальной магистрали 16 через элемент И 11 в виде сигнала ОТВл на вход

30операционного блока при обращении к локальной шине о Если готовность не подтверждается, то микропроцессор 18 (фиг.2) операционного блока 1 переходит к состояние ожидания и выставляет сигнал Подтверждение ожидания (СПО) который сохраняет активный уровень

до тех пор, пока не поступит сигнал 1 Готовность В течение состояния ожидания информация на внутренних магистралях адреса и управляющих сигналов остается неизменной.

Блок 3 предназначен для формиро- вания сигналов расширения адресного пространства А15 CJ-A19 , сигналов управления локальной магистралью Захват (ЗХВ), Программный перезапуск (УСТП), Управление (УПР), сигналов Запрос доступа к локальной шине (ЗДТЮ), Групповая пересылка данных (ЭГПД), Внутриблочная пересылка данных (ВПД), Разрешение доступа к системной магистрали (РДСМ), Запрос прямого обмена (ЗНД), анализа сигнала Подтверждение захвата (ПЗХВ) , Признаком прямого обмена между локальной и системной шинами является сигнал ГПД„

Из адресов А18 и А19 в блоке 3 формируются сигнал ЗДМО, который поступает в арбитр 4, и сигнал РДСМ, который поступает на блок 5о Сигнал

РДСМ формируется, если операционному блоку 1 необходимо обменяться информацией с системной магистралью,, По этому сигналу блок 5 открывает магистральные усилители для осуществления обмена с системной магистралью. Сигнал ЗДМО формируется, если операционный блок 1 обменивается информацией с локальной магистралью 16 - Сигнал ЗДМО поступает на арбитр 4 локальной шины. Арбитр 4 в соответствии с состоянием сигналов ЗДМ1 и ЗДМ2 (запросы на доступ к локальной магистрали от других активных элементов, подключенных к этой шине) и в соответствии с их приоритетами формирует один из сигналов Разрешение доступа к локальной магистрали : РДМО, РДМ1, РДМ2 Сигнал РДМО поступает на блок 6 и разрешает обмен между устройством и локальной магистралью Кроме того, он подается на один из входов элемента И 11, на другой вход которого приходит сигнал Ответ с локальной магистрали 16„

На выходе элемента К 11 формируется сигнал ответа ОТВл, который поступает в операционный блок 1 для формирования сигнала Готовность

Блок 2, первьй 8, второй 9 и третий 10 регистры адреса предназначены для прямого (минуя операционный блок) обмена информацией между памятью операционного блока 1 и системной 15 или локальной 16 магистралями (внутри- блочная пересылка данных - ВПД) или для прямого обмена данными между локальной и системной магистралями (групповая пересылка данных ГПД)о

Прямой обмен информацией (минуя операционный блок) удобен тем, что перемещение больших массивов информации (файлов) идет быстрее, чем под управлением операционного блока„ Это связано с тем, что отпадает необхо- .димость операционному блоку следить за текущим адресом перемещаемого файла для формирования признака конца перемещения и нет необходимости в последовательном чтении информации операционным блоком из источника и записи в приемник.

Под управлением микропроцессора операционного блока в блок 2 заносятся начальный адрес перемещаемого массива, длина массива и направление перемещения, В блоке 3 из адресов расширения А18 и А19 формируются

признаки обращения к локальной или к системной шинам ОДНО или РДСМ)„

В спучае обмена данными между шинами в блоке 3 формируется сигнал Групповая пересыпка данных (ГИД) и одновременно сигналы РДСМ и ЭДМСК

В блоке 3 происходит также формирование сигнала Запрос пряного обмена данными (ЗПД), в ответ на который бпок 2 Нормирует сигнал Запрос достугя на внутреннюю магистраль () г.а операционный блок 1 „ Блок

1отвечает сигналом разрешения доступа на внутреннюю магистраль (РДМ) и отключается от внутренних магистралей путем снятия адресных, информационных и управляющих сигналов г Блок

2выставлю -т га внутреннюю адресную шину инфцжацию начальном адресе АО...Л7 перемещаемого массива и в

соо iтствли с направлением аил 1. -41 Ч1Н, ВДЧ или ЗАП, ПГК на si шину управления Счн- хрониз41ру г:ь сигналом 2, блок 2 инкрементирует нччэтьный адрес и выставляв err на адресную тайну до тех

игр,

1 И

ntреголнится счетчик

длш-ifci массива, ет i .г Ш,

rvo грал л( ,- -I ленл г т

rhj.ii том блок 2 снимагаи;.,,; 1тгггрнней ма- mредаются под прав- .. го a laf как блок 2 фор; (рует только МЛАДШИЙ байт адреса /О „СА/, ;:лк формирования ст 1ршег о байта адреса с« „А1г; служ- первым 8, второй 9 н третий 10 . Под управлением операционного блока старший байт адреса для устройств системной магистра ч зан ситс« Е псовый регистр 8, для устройств локальной магистрали - во второй регистр 9, для внутренних блоков уст(зсмства - в третий регчстр 10.

Формула изобретения 1 , Устройство для сопплдения системной и локал ной магистралей, содержащее операционный блок, адресный выход которого через внутреннюю магистраль подключен к первым адресным входам блоков сопряжения с системной и локальной магистралями и входу дешифратора, управляющие выходы операционного блока через внутреннюю магистраль соединены с управляющими входами блоков сопряжения с локально и системной магистралями, информационный вход-выход операционного бло

5

ка через внутреннюю магистраль соединен с первыми информационными входами выходами блоков сопряжения с системной и локальной магистралями, причем адресные выходы блоков сопряжения с системной и локальной магистралями являются адресными выходами устройства для подсоединения соответственно к системной и локальной магистралям, вторые информационные входы-выходы блоков сопряжения с системной и локальной магистралями являются информационными входами-вмходами устройства для подключения соответственно к системной и локальной магистралям, группа управляющих входов-выходов блока сопряжения с системной магистралью является группой управляющих входов-выходов устройства для подключения к системной магистрали, а управляющие выходы блока сопряжения с локальной магистралью являются управляющими выходами устройства для подключения к локальной магистрали, выходы тактовый, охидания и установки операционного блока соединены с одно- входами б тока сопряжения с системной магистралью, вход Ответ от системной мах нстрали операционного блока соединен с тактовым выходом мкжа сопряжения с сие темной магистралью, отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения одновременной независимой работы по двум магистралям и повышения производительности, в него введены блок групповой пересылки данных, блок управления доступом к магистралям, арбитр локальной магистрали, первый, второй и третий регистры, элемент И, выход которого подключен к входам Ответ от локапьной магистрали опе- , рационного блока и блока групповой пересылки данных, вход Ответ от сис емной магистрали которого соединен с одноименным выходом блока сопряжения с системной магистралью, входы Подтверждение прямого доступа блоков сопряжения с системной и локальной магистралями и блока управления доступом к магистралям соединены с первым стробирующим выходом блока групповой пересыпки данных, второй стробирующий выход которого соединен с входом Запрос доступа к магистрали операционного блока, стробирующий выход которого соединен с входом

0

5

0

0

5

1 16/2450

Разрешение доступа к магистрали

с с г н п в р р н д м ч с ж с ма эл до со в ар со да ло к эл О кл вы ра вы З ло Си по З ли вы вт ни

блока групповой пересыпки данных, тактовый вход которого соединен с тактовыми входами арбитра локальной магистрали блока управления доступом к магистралям и с тактовым выходом операционного блока, адресный вход- выход блока групповой пересылки данных через внутреннюю магистраль соединен с адресным входом блока управления доступом к магистралям и с входом дешифратора, информационный вход-выход блока управления доступом к магистралям через внутреннюю магистраль соединен с информационными входами первого, второго и третьего регистров, информационным входом-выходом блока групповой пересылки данных у информационным входом-выходом операционного блока, управляющие выходы блока групповой пересылки данных через внутреннюю магистраль соединены с входами записи-чтения первого, второго и третьего регистров, управляющими входами блока управления доступом к магистралям и управляющими выходами операционного блока, первый, второй и третий стробирующие выходы блока управления доступом к магистралям являются соответственно выхоами Захват, Программный перезапуск, Управление устройства для подключения к локальной магистрали, причем второй стробирующий выход блока управления доступом к магистралям подключен к входу Программный перезапуск операционного блока, вход Подтверждение захвата блока управления доступом к магистралям является одноименным входом устройства для подключения к локальной магистрали, четвертый и пятый стробирующие выходы блока управления доступом к магистралям соединены соответственно с входами групповой и внутриблочной пересылки данных блока сопряжения с окальной магистралью и арбитра локальной магистрали, входы Установка блока управления доступом к магистралям, арбитра локальной магистрали соединены с выходом Установка операционного блока, первый, второй, третий, четвертый и пятый выходы дешифратора соединены соответственно с синхровходами первого, второго и третьего регистров, блока групповой пересылки данных и блока управления доступом к магистралям, шестой и

18

0

5

0

5

0

5

0

5

0

5

седьмой стробирующие выходы которого соединены соответственно с входом Разрешение доступа к системной магистрали блока сопряжения с системной магистралью и входом Запрос прямого обмена данными блока групповой пересылки данных, выход второго регистра и адресный выход блока управления доступом к магистралям соединены с вторым и третьим адресными входами блока сопряжения с локальной магистралью, выход третьего регистра через внутреннюю магистраль соединен с первым адресным входом блока сопряжения с локальной магистралью, первый стробирующий выход арбитра локальной магистрали соединен с первым входом элемента И и с входом Разрешение доступа к локальной магистрали блока сопряжения с локальной магистралью, второй и третий стробирующие выходы арбитра локальной магистрали являются соответственно первым и вторым выходами устройства Разрешение доступа к локальной магистрали для подключения к локальной магистрали, второй вход элемента И является входом устройства Ответ локальной магистрали для подключения к локальной магистрали, первый и второй управляющие входы арбитра локальной магистрали являются первыми и вторым входами устройства Запрос доступа для подключения к локальной магистрали, восьмой стро- Сирующий выход блока управления доступом к магистралям соединен с входом Запрос доступа к локальной магистрали арбитра локальной магистрали, выход первого регистра соединен с вторым адресным входом блока сопряжения с системной магистралью

2с Устройство по По 1, -о т л и - чающееся тем, что блок групповой пересылки данных содержит первый, второй, третий и четвертый элементы ИЛИ-НЕ, дешифратор, триггер запроса доступа к магистрали, первый, и второй элементы ИЛИ, счетчик младших разрядов адреса, счетчик длины массива, триггер режима работы, первый, второй, третий, четвертый, пя- тый, шестой, седьмой, восьмой и девятый элементы И, магистральный усилитель, счетчик управления, элемент НЕ и элемент И-НЕ, причем первые входы первого, второго и третьего элементов ИЛИ-НЕ объединены и подключены к входу Выдача блока, информационный

19

вход дешифратора и выход магистрального усилителя являются адресным входом-выходом блока, стробирующий вход дешифратора соединен с синхро- входом блока, синхровход триггера запроса доступа к магистрали подключен к входу запроса прямого доступа блока, а вход сброса подключен к выходу счетчика длины массива, первый и второй входы первого элемента ИЛИ соединены соответственно с входами Ответ локальной и системной магистралей блока, информационные входы счетчика младших разрядов адреса, счетчика длины массива и триггера режима работы объединены и подключены к информационному входу блока, первый вход первого элемента И соединен с входом блока Разрешение доступа к магист ал i, второй вход первого элемента И соединен с выходом триггера запроса доступа к магистрали, информационные входи магистрального усилителя соединены с выходами счетчика младших разрядов адреса, счетный вход счетчика управления ясляется тактовим входом Слока, выходы второго, третьего, четвертого и пятого Г чьс-т нтов I , с управляющими вы одаг-и блока, первые входы шестого элемента И и четвертое элемента ИЛИ-ИЕ Сие, :инени со счетным входом счетчика управления, первый в; код дешифратора соединен с вторым -ходом перво: о элемента ШШ-НЕ, выход ното- рогч/ г одключеь к ьход записи счетчик ri младших разрядов адреса, второй выход дешифратора соединен с вторым входам второго элемрнта ИЛИ-НЕ, выход которого подключен к входу записи счетчика длины массива, третий выход дешифратора соединен с вторым входом третьего элемента ИЛИ-НЕ, выход которого подключен к счетному вхо. трьг- гепа р«жчг работы, прямой 1;ыход которого соединен с первыми входами второго и третьего элементов И, а инверсный выход соединен с первыми входами етвертого и пятого элементов И, вторпе входы второго, Tpt-тьего, четвертого и пятого элементов И объединр -н и соединены с выходом элемента И-НЕ, третьи входы третьего к четвертого элементов И объедгнены и соединены с выходом первого элемента ИЛИ, выхец нулевого разряда счегчика управления соединен с вторыми вхоплми шестого элемента И, четвертого эле16/2460zu

мента ИЛИ-НЕ и первым входом седьмого элемента И, выход первого разряда счетчика управления соединен с третьими входами шестого элемента И, четвертого элемента ИЛИ-НЕ и вторым входом седьмого элемента И, выход шестого элемента И соединен с первым входом восьмог.о элемента И и через эпемент НЕ с первым входом девятого элемента И. выход четвертого элемента ИЛИ-НЕ и выход седьмого элемента И соединены соответственно с первым и вторым входами второго элемента ИЛИ, выход которого соединен с первым входом элемента И-НЕ, выход первого элемента И соединен с входом сброса счетчика управления и вторыми входами восьмого и девятого элемен10

15

20

25

30

35

40

45

50

5

тов И и элемента И--Ш1, выход восьмого элемента И соединен со счетными входами счетчика младших разрядов адреса и счетчика длины массива, выход девятого элемента И соединен с управляющим входом магистрального усилите чя и с первым стробирующим выходом блока, выход триггера запроса доступа к магистрали соединен с вторым стробирующим выходов, блока

Зс Устройство по По1, отличающееся тем, что блок управления доступом к магистралям содержит первый, второй, третий и четвертый элементы ИЛИ-НЕ, дешифратор, переключатель режимов работа - отладка, первый, гторой и третий регистры, од- новибратор, первый, второй и третий элементы И, счетчик, первый и второй элементы И-НЕ, триггер, первый и второй элементы НЕ, элемент индикации готовности, элемент индикации отказа, первый, второй и третий элементы ИЛИ, причем первые входы первого и второго элементов ИЛИ-НЕ соединены с входом Выдача блока, первый вход третьего элемента ИЛИ-НЕ соединен с входом Прием блока, адресный и управляющий входы дешифратора соединены соответственно с адресным и синхровхода- ми блока, входы данных первого и второго регистров, счетчика соединены с выходом третьего регистра и являются информационным входом-выходом блока, вход одновибратора соединен с первым выходом второго регистра, а выход подключен к перьому входу первого эле- MGHTci И-Hii, второй вход которого подключен к второму выходу второго ре- гист)5, выход первого элемента И-НЕ

0

5

0

5

0

5

0

5

тов И и элемента И--Ш1, выход восьмого элемента И соединен со счетными входами счетчика младших разрядов адреса и счетчика длины массива, выход девятого элемента И соединен с управляющим входом магистрального усилите чя и с первым стробирующим выходом блока, выход триггера запроса доступа к магистрали соединен с вторым стробирующим выходов, блока

Зс Устройство по По1, отличающееся тем, что блок управления доступом к магистралям содержит первый, второй, третий и четвертый элементы ИЛИ-НЕ, дешифратор, переключатель режимов работа - отладка, первый, гторой и третий регистры, од- новибратор, первый, второй и третий элементы И, счетчик, первый и второй элементы И-НЕ, триггер, первый и второй элементы НЕ, элемент индикации готовности, элемент индикации отказа, первый, второй и третий элементы ИЛИ, причем первые входы первого и второго элементов ИЛИ-НЕ соединены с входом Выдача блока, первый вход третьего элемента ИЛИ-НЕ соединен с входом Прием блока, адресный и управляющий входы дешифратора соединены соответственно с адресным и синхровхода- ми блока, входы данных первого и второго регистров, счетчика соединены с выходом третьего регистра и являются информационным входом-выходом блока, вход одновибратора соединен с первым выходом второго регистра, а выход подключен к перьому входу первого эле- MGHTci И-Hii, второй вход которого подключен к второму выходу второго ре- гист)5, выход первого элемента И-НЕ

подключен к входу элемента индикации готовности и к первому входу данных третьего регистра, а через первый элемент НЕ к входу элемента индикации отказа, первый вход первого элемента И соединен с третьим выходом второго регистра, а второй вход подключен к тактовому входу блока, выход первого элемента И подключен к счетному входу счетчика, счетный вход триггера соединен с четвертым выходом второго регистра, а вход сброса триггера соединен с входом установки блока, выход триггера соединен с вторым входом третьего регистра, входы второго элемента И-НЕ подключены к первому выходу первого регистра и соединены с адресным выходом блока, а выход второго элемента И-НЕ подключен к пер- вому входу второго элемента И и через второй элемент НЕ к первому входу третьего элемента И, при этом вторые входы второго и третьего элементов И подключены к входу блока Подтвержде- ние прямого доступа, а их выходы подключены соответственно к первым входам первого и второго элементов ИЛИ, вторые входы которых соединены с первым входом третьего элемента ИЛИ и подключены к пятому выходу второго регистра, второй вход третьего элемента ИЛИ подключен к шестому выходу второго регистра, первый вход четвертого элемента ИЛИ соеди- нен с входом Выдача блока, выходы дешифратора соединены соответственно с вторыми входами первого, второго, третьего и четвертого элементов ИЛИ- НЕ, а выходы каждого из них подключе- ны соответственно к входам записи первого, второго и третьего регистров и входу записи счетчика, при этом выход переполнения счетчика соединен с третьим входом данных третьего регистра, четвертый вход данных которого соединен с входом блока Подтверждение захвата, а

пятый вход данных подключен к выходу переключателя режимов работа - отладка, первый, второй и третий выходы лервого регистра соединены соответственно с первым, вторым и третьим стробирующими выходами блока, пятый и шестой выходы второго регистра соединены соответственно с четвертым и пятым стробирующими выходами блока, выходы второго, третьего и первого элементов ИЛИ соединены соответственно с шестым и седьмым стробирую- 1 {ими выходами блока, причем шестой выход второго регистра соединен с вторым входом третьего элемента ИЛИ,

I

4 о Устройство по п.1, отличающееся тем, что арбитр локальной магистрали содержит первый и второй регистры, приоритетный шифратор, элемент НЕ, причем первый, второй, третий информационные, стро- бирующий и установочный входы первого регистра соединены соответственно с первым, вторым и третьим входами запроса доступа к магистрали, тактовым входом и входом установки блока, первая группа входов приоритетного шифратора соединена с выходами первого регистра, первый и второй входы приоритетного шифратора соединены с входами групповой и внутриблочнон пересылки данных блока, первый, второй и третий входы данных второго регистра соединены с соответствуишдеми выходами приоритетного шифратора, а выходы второго регистра соединены с второй группой входов приоритетного шифратора и с первым, вторым и третьим стробирующими выходами сигналов разрешения доступа к магистрали блока, при этом установочные входы регистров объединены и подключены к установочному входу блока, а стробирующий вход первого регистра через элемент НЕ соединен со стробирующим входом второго регистра

y cf tj&OtSC/Tf&O CЈ /7/3/t r rft/&л

Ж Х/У,

W./

(l

I

fc S ft .

э§ Ј

о чэ

JO O JQ

А А А

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство межмодульной связи для системы коммутации сообщений | 1986 |

|

SU1388883A1 |

| Устройство для сопряжения цифровых вычислительных машин | 1990 |

|

SU1783531A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1987 |

|

SU1451768A1 |

| Мультиплексное устройство для обмена информацией | 1983 |

|

SU1157546A1 |

| Устройство для сопряжения ЭВМ с магистралью | 1988 |

|

SU1508227A1 |

| Устройство управления доступом к памяти для обмена массивами данных в многопроцессорной системе | 1989 |

|

SU1633418A1 |

| Устройство для сопряжения ЭВМ в вычислительной системе с децентрализованным арбитром магистрали | 1984 |

|

SU1291997A1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| Микропроцессорная система с встроенным контролем | 1986 |

|

SU1417651A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С ВНЕШНИМИ ОБЪЕКТАМИ | 1993 |

|

RU2018944C1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в цифровых системах управления, в частности, при построении программируемых контроллеров. Целью изобретения является расширение функциональных возможностей за счет обеспечения одновременной независимой работы по двум магистралям и повышение производительности. Устройство содержит операционный блок, блок групповой пересылки данных, блок управления доступом к магистралям, арбитр локальной магистрали, блок сопряжения с системной магистралью, блок сопряжения с локальной магистралью, дешифратор, адресные регистры, элемент И. 3 з.п. ф-лы, 7 ил.

7 А 7 /

fo OJ

Г Са СЧ1 Г«-

g т-, cvi t)

IJ- фф

iirjiii.i

8

ca r rp у i | A A/KA J Г

Г4- CQ 0

«a9s g s gg

7 /

fo OJgC

i

VO

«

Г«-

«D

I

Ы

-

f

о

Шина упрадления 13

Адресные шины

$

,J 3

Qc-H

U

bh i ыъа

G

Редаыор ОьН)ркове1 { ая

Сос.авитель А.Засорин

Техред . ( прдюкод Корректор М.Демчик

АО...А7 Ј

&

I

№...J)tf

209

2Ю.

211

Фиг. 1

| УСТРОЙСТВО для ОХЛАЖДЕНИЯ ТВОРОГА | 0 |

|

SU189638A1 |

| Шахматные часы | 1933 |

|

SU35454A1 |

Авторы

Даты

1991-08-23—Публикация

1988-11-01—Подача