/ Вход 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения частоты | 1985 |

|

SU1292162A1 |

| Широтно-импульсный модулятор | 1989 |

|

SU1677857A1 |

| Устройство для управления инвертором | 1987 |

|

SU1617584A1 |

| РАДИОИЗОТОПНЫЙ ТОЛЩИНОМЕР ПОКРЫТИЙ | 1990 |

|

SU1729188A1 |

| Устройство для деления в системе остаточных классов | 1983 |

|

SU1141400A1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2446454C1 |

| Устройство для управления трехфазным мостовым инвертором | 1977 |

|

SU666627A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Способ преобразования переменного напряжения в код и устройство для его осуществления | 1986 |

|

SU1436275A1 |

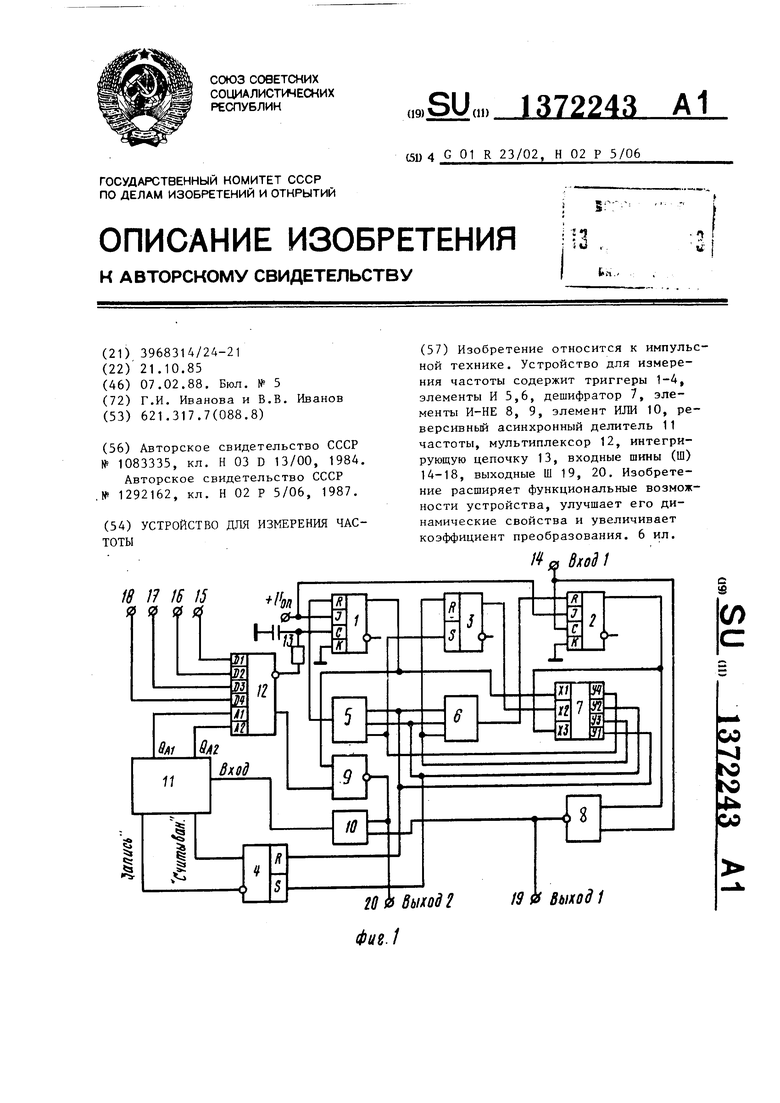

Изобретение относится к импульсной технике. Устройство для измерения частоты содержит триггеры 1-4, элементы И 5,6, дешифратор 7, элементы И-НЕ 8, 9, элемент ИЛИ 10, реверсивный асинхронный делитель 11 частоты, мультиплексор 12, интегрирующую цепочку 13, входные шины (Ш) 14-18, выходные Ш 19, 20. Изобретение расширяет функциональные возможности устройства, улучшает его динамические свойства и увеличивает коэффициент преобразования. 6 ил.

00

ю ю

Фиг.1

Изобретение относится к импульсной технике и может быть использовано в системе автоматического управления.

Цель изобретения - расширение функциональных возможностей устройства, улучшение динамических свойств и увеличение коэффициента преобразования .

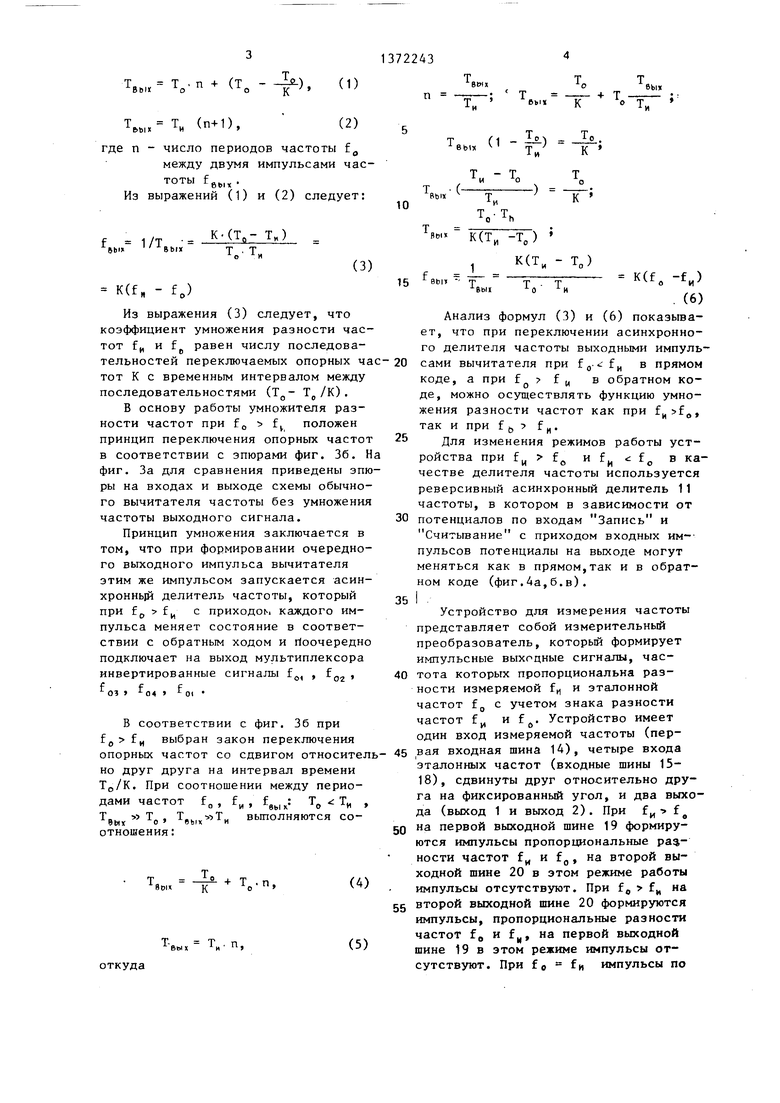

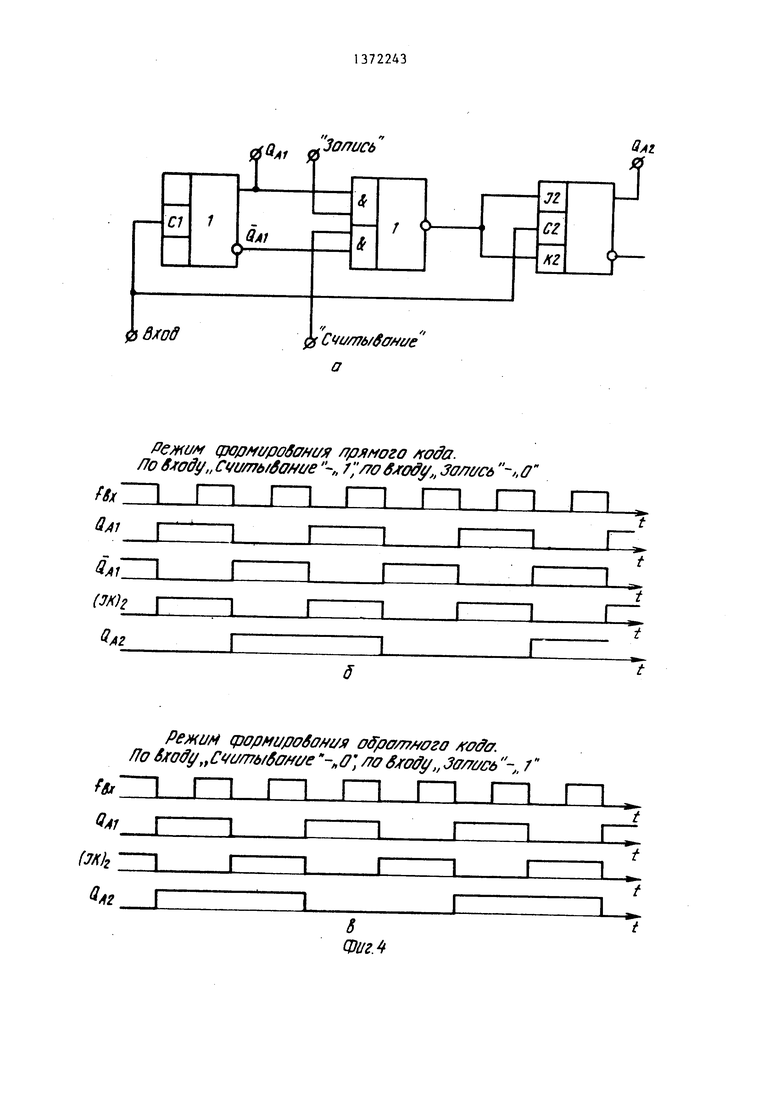

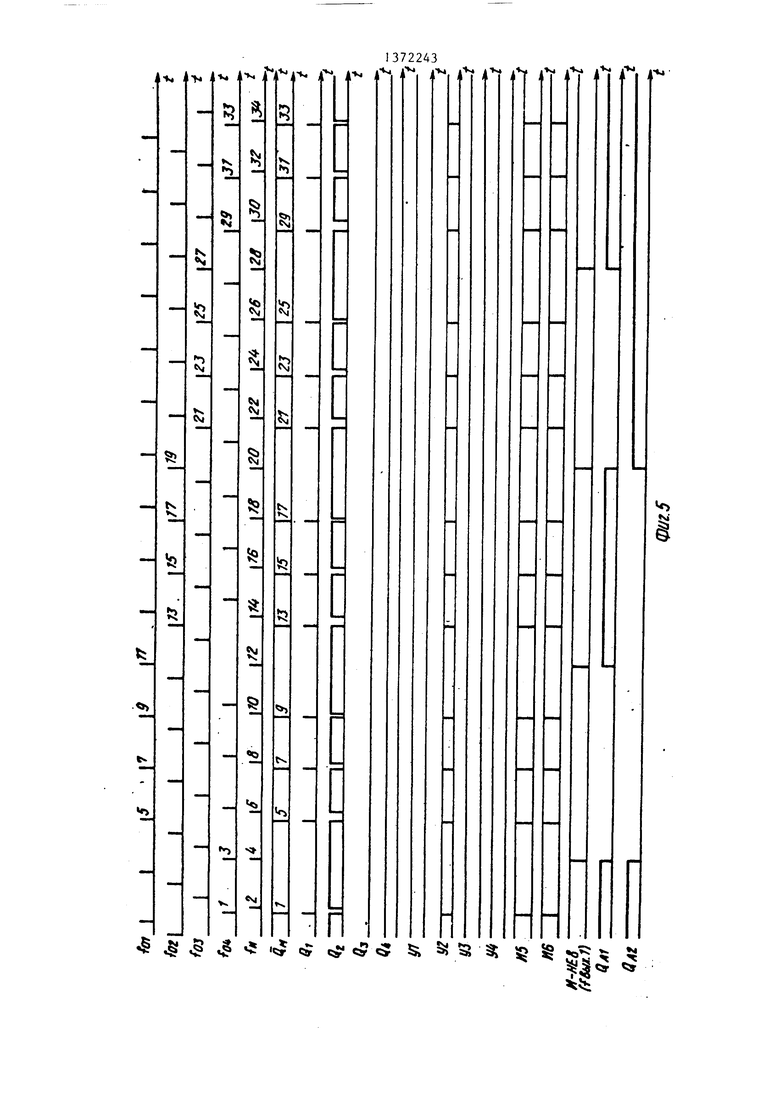

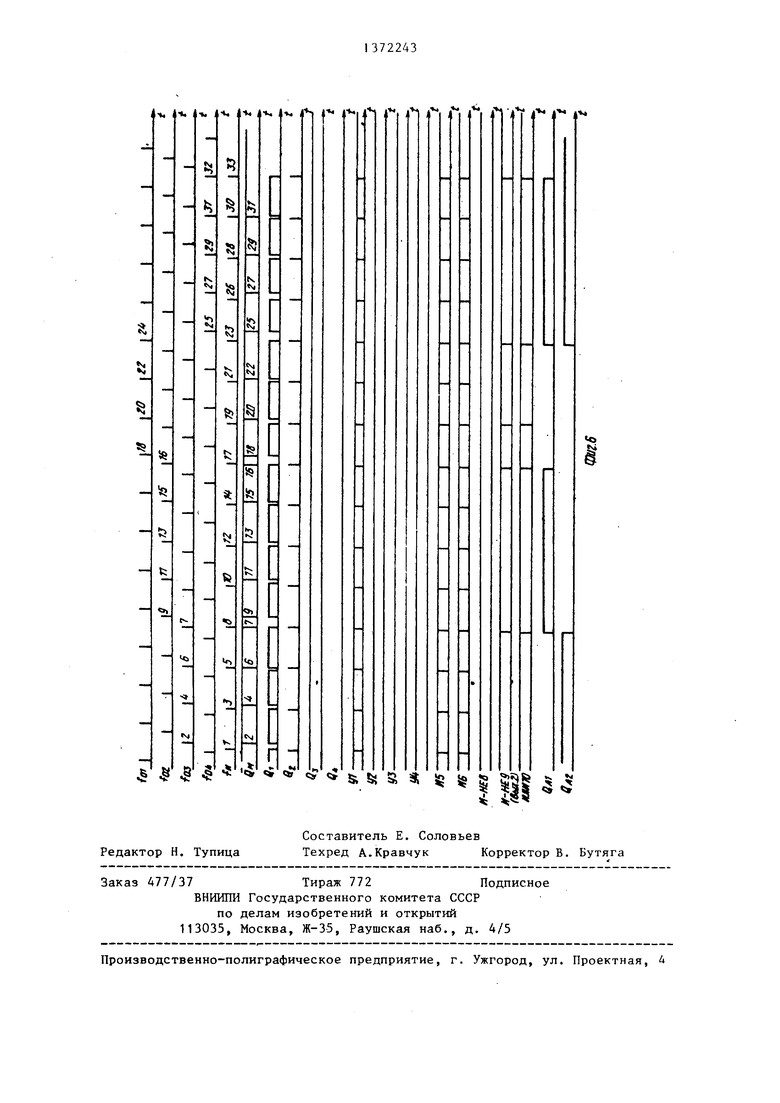

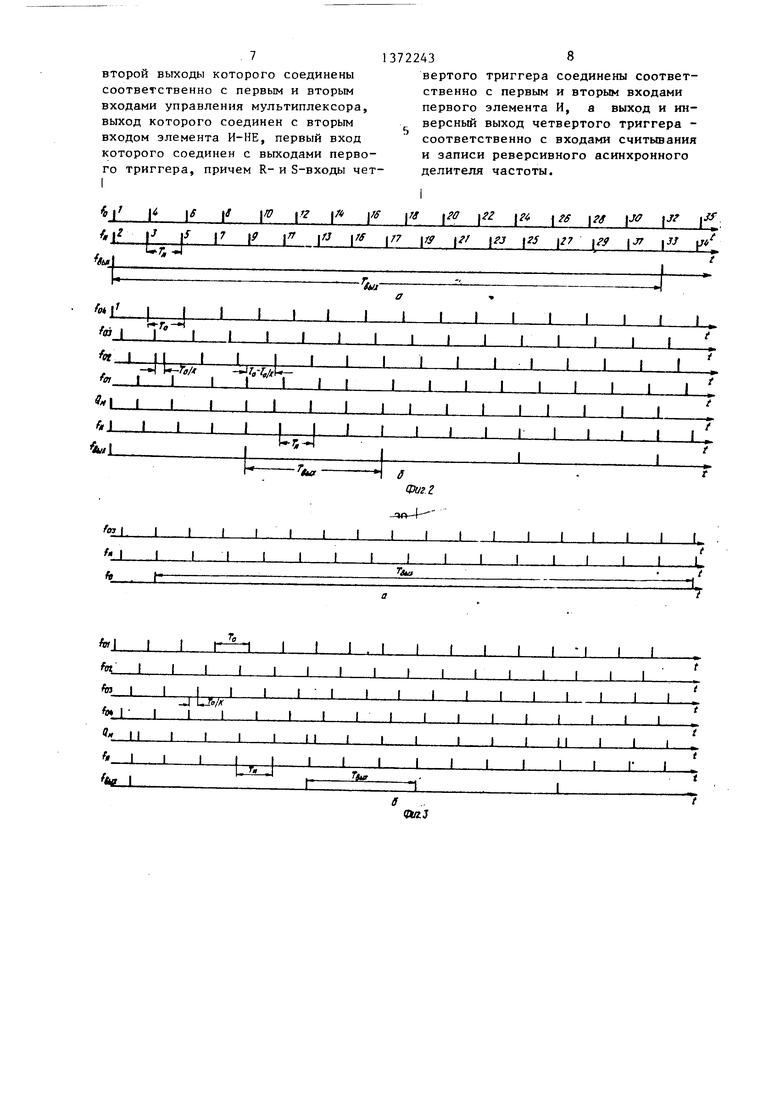

На фиг. 1 показана принципиальная схема предлагаемого устройства; на фиг.2 - эпюры напряжений, поясняющие принцип умножения разности частот при f, f ; на фиг. 3 - то же, при fo ЕИ нз фиг.А - принципиальная схема и эпюры напряжения реверсивного асинхронного делителя частоты; на фиг. 5 - эпюры напряжения устройства при fj, ЕО ; на фиг.6 - то же при f Q f .

.ного делителя 11 частоты, входы Запись и Считывание которого соединены соответственно с инверсным и прямым выходами четвертого триггера 4.

Первый и второй выходы реверсивного асинхронного делителя 11 частоты соединены соответственно с первым

1Q и вторым входами управления мультиплексора 12, инверсный выход которого через интегрирующую цепочку 13 соединен со счетным входом первого триггера 1. Прямой выход мультиплек15 сора 12 и выход триггера 1 соединены с соответствующими входами второго элемента И-НЕ 9, выход которого соединен с вторым входом элемента ИЛИ 10 и является второй выходной

20 шиной 20 устройства.

Информационные входы мультиплексора 12 соединены соответственно с входными шинами 15-18.

1-входы первого 1 и второго 2

Устройство содержит триггеры 1-А, первый 5 и второй 6 элементы И, дешифратор 7, первый 8 и второй 9 элементы И-НЕ, элемент ИЛИ 10, реверсив- 25 триггеров соединены с потенциалом ный асинхронный делитель 11 частоты, логического 1, а К-входы - с потен- мультиплексор 12, интегрирующую це- циалом логического О, почку 13, первую входную шину 14, вто- Принцип работы устройства при вторую 15, третью 16, четвертую 17

30

и пятую 18 вхцдные шины, первую 19 и вторую 20 выходные шины.

Выходы триггеров 1-3 соединены с соответствующими входами дешифра - тора 7, первый и второй выходы котоf f поясняется эпюрами фиг.2б. На фиг. 2а для сравнения приведены эпюры на входах и выходе схемы обычного вычитателя частоты без умножения разности выходных частот. На информационные входы мультиплексора

рого соединены, соответственно,с пер- (фиг.1) подаются четыре последова- вым и вторым входами первого 5 и вто- тельности импульсов f, -Едд, сдвинутые друг относительно друга на интервал времени . При fy, f,, на

40

рого 6 элементов И. Первый выход дешифратора 7 соединен одновременно с R-входом четвертого триггера 4, второй выход - с S-входом четвертого триггера 4. Третий выход дешифратора 7 соединен с третьим входом второго элемента И 6 и R-входом третьего триггера 3. Четвертый выход дешифратора 7 соединен с третьим входом первого элемента И 5 и S-входом третьего триггера 3.

Выходы первого 5 и второго 6 элементов соединены соответственно с R-входами первого 1 и второго 2 триг- gg геров. Счетный вход второго триггера 2 являющийся первой входной шиной 14, и его выход соединены с со- ответс твующими входами первого элемента И-НЕ 8, выход которого соединен с первым входом элемента ИЛИ 10, эыход которого является первой выходной шиной 19 устройства и соединен с входом реверсивного асннхрон О f

выходе схемы формируются импульсы разностной -частоты.

Принцип умножения заключается в том, что при формировании очередного входного импульса этим же импульсом запускается асинхронный де- 45 литель частоты, который с приходом каждого выходного импульса вычитателя меняет свои состояния в соответствии с прямым кодом и,управляя этими импульсами работой мультиплексора, подключает на выход мультиплексора инвертированные сигналы

01 01 0 04 01

При выбранном законе, переключения опорных частот и соотношениях 55 между периодами частот (фиг.2) f,(T), f,(T,), fB,,,(T,J:T,T,,

Твы,Т,, ношения:

Те.

Bbii

выполняются COOT.ного делителя 11 частоты, входы Запись и Считывание которого соединены соответственно с инверсным и прямым выходами четвертого триггера 4.

Первый и второй выходы реверсивного асинхронного делителя 11 частоты соединены соответственно с первым

и вторым входами управления мультиплексора 12, инверсный выход которого через интегрирующую цепочку 13 соединен со счетным входом первого триггера 1. Прямой выход мультиплексора 12 и выход триггера 1 соединены с соответствующими входами второго элемента И-НЕ 9, выход которого соединен с вторым входом элемента ИЛИ 10 и является второй выходной

шиной 20 устройства.

Информационные входы мультиплексора 12 соединены соответственно с входными шинами 15-18.

1-входы первого 1 и второго 2

триггеров соединены с потенциалом логического 1, а К-входы - с потен- циалом логического О, Принцип работы устройства при

триггеров соединены с потенциалом логического 1, а К-входы - с потен циалом логического О, Принцип работы устройства при

f f поясняется эпюрами фиг.2б. На фиг. 2а для сравнения приведены эпюры на входах и выходе схемы обычного вычитателя частоты без умножения разности выходных частот. На информационные входы мультиплексора

(фиг.1) подаются четыре последова- тельности импульсов f, -Едд, сдвинутые друг относительно друга на интервал времени . При fy, f,, на

0

g

О f

выходе схемы формируются импульсы разностной -частоты.

Принцип умножения заключается в том, что при формировании очередного входного импульса этим же импульсом запускается асинхронный де- 5 литель частоты, который с приходом каждого выходного импульса вычитателя меняет свои состояния в соответствии с прямым кодом и,управляя этими импульсами работой мультиплексора, подключает на выход мультиплексора инвертированные сигналы

01 01 0 04 01

При выбранном законе, переключения опорных частот и соотношениях 5 между периодами частот (фиг.2) f,(T), f,(T,), fB,,,(T,J:T,T,,

Твы,Т,, ношения:

Те.

Bbii

выполняются COOTTB.. Т,.п + (Т„ - ), (1)

Т.ых (1).)

где п - число периодов частоты f

между двумя импульсами частоты f g, . Из выражений (1) и (2) следует:

V 1/Т,ь,.

К-(TO- Tj

т.. т„

K(f, - fJ

Из выражения (3) следует, что коэффициент умножения разности частот f, и fp равен числу последовательностей переключаемых опорных чатот К с временным интервалом между последовательностями ( Т,/К) .

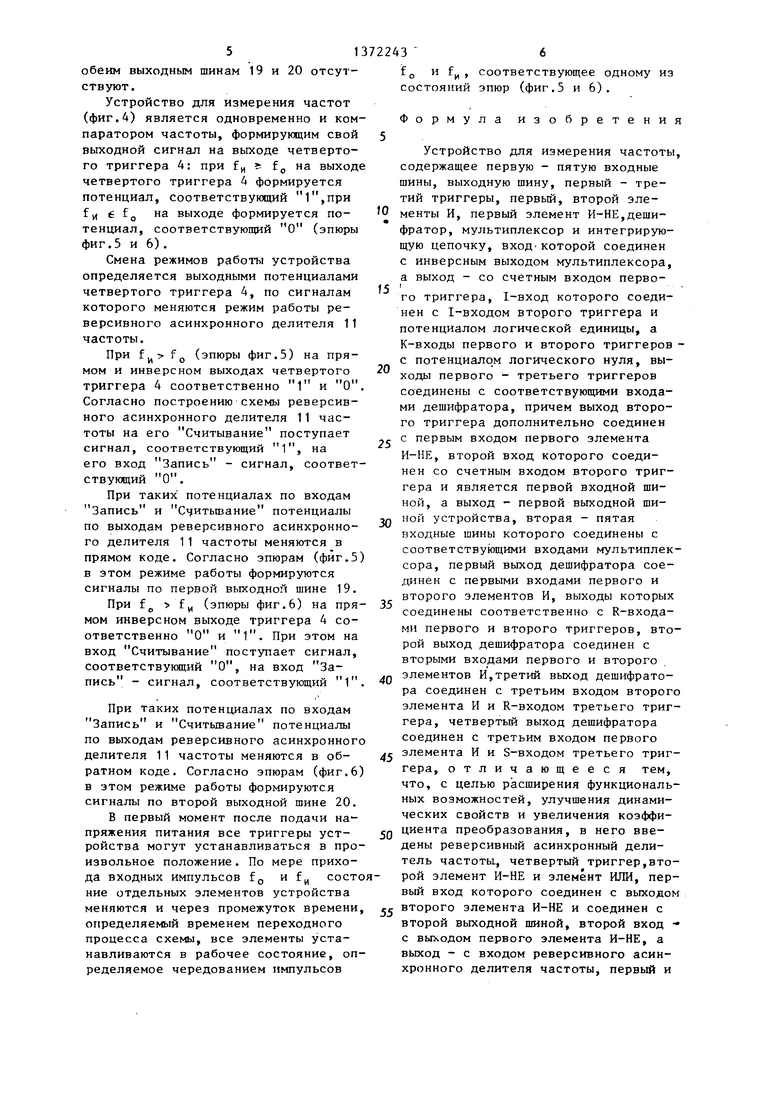

В основу работы умножителя разности частот при fo f положен принцип переключения опорных частот в соответствии с эпюрами фиг. 36. Н фиг. За для сравнения приведены эпюры на входах и выходе схемы обычного вычитателя частоты без умножения частоты выходного сигнала.

Принцип умножения заключается в том, что при формировании очередного выходного импульса вычитателя этим же импульсом запускается асин- хроннь1й делитель частоты, который при fp f с приходоь. каждого импульса меняет состояние в соответствии с обратным ходом и г1оочередно подключает на выход мультиплексора инвертированные сигналы f, , f ,

- Of f 04 01

В соответствии с фиг. 36 при fд fи выбран закон переключения опорных частот со сдвигом относително друг друга на интервал времени TO/К. При соотношении между периодами частот „, f, f,: Т„ Т , . Тв„,«Т, выполняются соотношения:

век

+ Т

(4)

Т-.

Т„.п,

(5)

откуда

10

К(Т -Т,)

с

а

ьК(Т, - Т)

Г

15 вьи т

Т Т 0 И

- K(f, -f,) . (6)

Анализ формул (3) и (6) показывает, что при переключении асинхронного делителя частоты выходными импуль- 20 сами вычитателя при f. f в прямом коде, а при f - { в обратном коде, можно осуществлять функцию умножения разности частот как при , так и при ft, f и

25 Для изменения режимов работы устройства при f, f и f : fp В качестве делителя частоты используется реверсивный асинхронный делитель 11 частоты, в котором в зависимости от

30 потенциалов по входам Запись и

Считывание с приходом входных им- пульсов потенциалы на выходе могут меняться как в прямом,так и в обратном коде (фиг.4а,б.в).

35 I

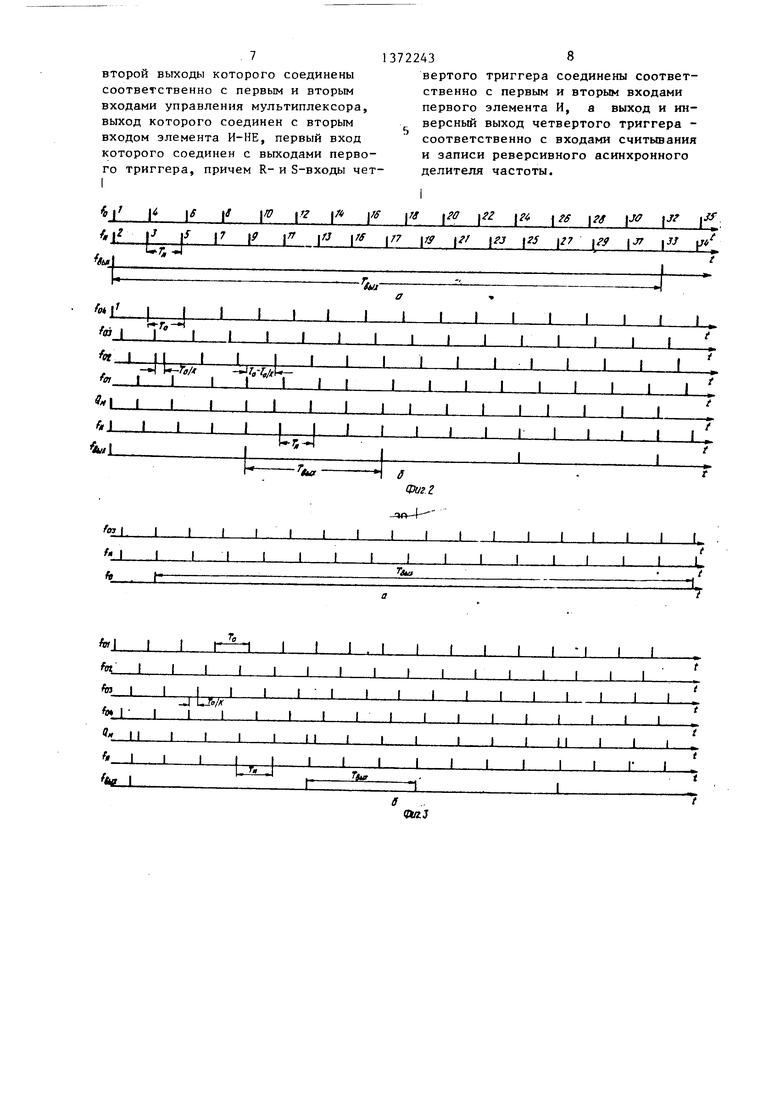

Устройство для измерения частоты

представляет собой измерительный преобразователь, который формирует импульсные выходные сигналы, час40 тота которых пропорциональна разности измеряемой f и эталонной частот fg с учетом знака разности частот fj, и f. Устройство имеет один вход измеряемой частоты (пер45 вая входная шина 14), четыре входа эталонных частот (входные шины ISIS), сдвинуты друг относительно друга на фиксированный угол, и два выхода (выход 1 и выход 2). При f j, f

5Q на первой выходной шине 19 формируются импульсы пропорциональные ности частот f , и f , на второй выходной шине 20 в этом режиме работы импульсы отсутствуют. При f, ц на

55 второй выходной шине 20 формируются импульсы, пропорциональные разности частот fe и f , на первой выходной шине 19 в этом режиме импульсы отсутствуют. При fo fn импульсы по

и -. Lg на выход А формируется

обеим выходным шинам 19 и 20 отсутствуют.

Устройство для измерения частот (фиг,4) является одновременно и компаратором частоты, формирующим свой выходной сигнал на выходе четвертого триггера 4; при „ f четвертого триггера потенциал, соответствующий 1,при f t fo на выходе формируется потенциал, соответствующий О (эпюры фиг.5 и 6).

Смена режимов работы устройства определяется выходными потенциалами четвертого триггера 4, по сигналам которого меняются режим работы реверсивного асинхронного делителя 11 частоты.

При (эпюры фиг.5) на прямом и инверсном выходах четвертого триггера 4 соответственно 1 и О Согласно построению схемы реверсивного асинхронного делителя 11 частоты на его Считывание поступает сигнал, соответствующий 1, на его вход Запись - сигнал, соответствующий О.

При таких потенциалах по входам Запись и С итьшание потенциалы по выходам реверсивного асинхронного делителя 11 частоты меняются в прямом коде. Согласно эпюрам (фиг.5 в этом режиме работы формируются сигналы по первой выходной шине 19.

При f fn (эпюры фиг.6) на пря мом инверсном выходе триггера 4 соответственно О и 1. При этом на вход Считывание поступает сигнал, соответствующий О, на вход Запись - сигнал, соответствующий 1

При таких потенциалах по входам Запись и Считьшание потенциалы по выходам реверсивного асинхронного делителя 11 частоты меняются в обратном коде. Согласно эпюрам (фиг.6) в этом режиме работы формируются сигналы по второй выходной шине 20.

В первый момент после подачи пряжения питания все триггеры устройства могут устанавливаться в произвольное положение. По мере прихода входных импульсов fj, и f, состоние отдельных элементов устройства меняются и через промежуток времени, определяемый временем переходного процесса схемы, все элементы устанавливаются в рабочее состояние, определяемое чередованием импульсов

5

0

5

5

fо и f, соответствующее одному из состояний эпюр (фиг.5 и 6).

Формула изобретения

Устройство для измерения частоты, содержащее первую - пятую входные шины, выходную шину, первый - третий триггеры, первый, второй элементы И, первый элемент И-НЕ,дешифратор, мультиплексор и интегрирующую цепочку, ВХОД которой соединен с инверсным выходом мультиплексора, а выход - со счетным входом первого триггера, 1-вход которого соединен с 1-входом второго триггера и потенциалом логической единицы, а К-входы первого и второго триггеров - с потенциалом логического нуля, выходы первого - третьего триггеров соединены с соответствующими входами дешифратора, причем выход второго триггера дополнительно соединен с первым входом первого элемента И-НЕ, второй вход которого соединен со счетным входом второго триггера и является первой входной шиной, а выход - первой выходной шиной устройства, вторая - пятая входные шины которого соединены с соответствующими входами мультиплексора, первый выход дешифратора соединен с первыми входами первого и второго элементов И, выходы которых соединены соответственно с R-входа- ми первого и второго триггеров, второй выход дешифратора соединен с вторыми входами первого и второго элементов И,третий выход дешифратора соединен с третьим входом второго элемента И и R-входом третьего триггера, четвертый выход дешифратора соединен с третьим входом первого элемента И и S-входом третьего триггера, отличающееся тем, что, с целью расширения функциональных возможностей, улучшения динамических свойств и увеличения коэффициента преобразования, в него введены реверсивный асинхронный делитель частоты, четвертый триггер,второй элемент И-НЕ и элемент ИЛИ, первый вход которого соединен с выходом ег второго элемента И-НЕ и соединен с второй выходной шиной, второй вход - с выходом первого элемента И-НЕ, а выход - с входом реверсивного асинхронного делителя частоты, первый и

0

0

5

0

второй вьгходы которого соединены соответственно с первым и вторым входами управления мультиплексора, выход которого соединен с вторым входом элемента И-НЕ, первый вход которого соединен с выходами первого триггера, причем R-и S-входы чет- I

f С |/« |-У )// гг г гб гв Jff {« |SS

722438

вертого триггера соединены соответственно с первым и вторым входами первого элемента И, а выход и инверсный выход четвертого триггера - соответственно с входами считьшания и записи реверсивного асинхронного делителя частоты.

I

5

SS

t I t 1 Vi

M

(ч

S3

t:

N

fe

IQ

J9

-M

| Устройство для сравнения частот | 1982 |

|

SU1083335A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Авторское свидетельство СССР ,№ 1292162, кл | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1988-02-07—Публикация

1985-10-21—Подача