(54) ДИСКРИМИНАТОР ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения частот | 1982 |

|

SU1083335A1 |

| Устройство для измерения частоты | 1985 |

|

SU1372243A1 |

| Устройство для измерения частоты | 1985 |

|

SU1292162A1 |

| Дискриминатор импульсов | 1978 |

|

SU764098A1 |

| Широтно-импульсный модулятор | 1989 |

|

SU1677857A1 |

| Устройство для управления ведущим шаговым двигателем | 1981 |

|

SU999022A1 |

| Емкостно-электронный преобразователь перемещения | 1989 |

|

SU1721434A1 |

| Умножитель частоты следования импульсов | 1984 |

|

SU1210215A1 |

| Устройство для определения углового положения вала | 1987 |

|

SU1439739A1 |

| Следящий измеритель частоты | 1985 |

|

SU1298675A1 |

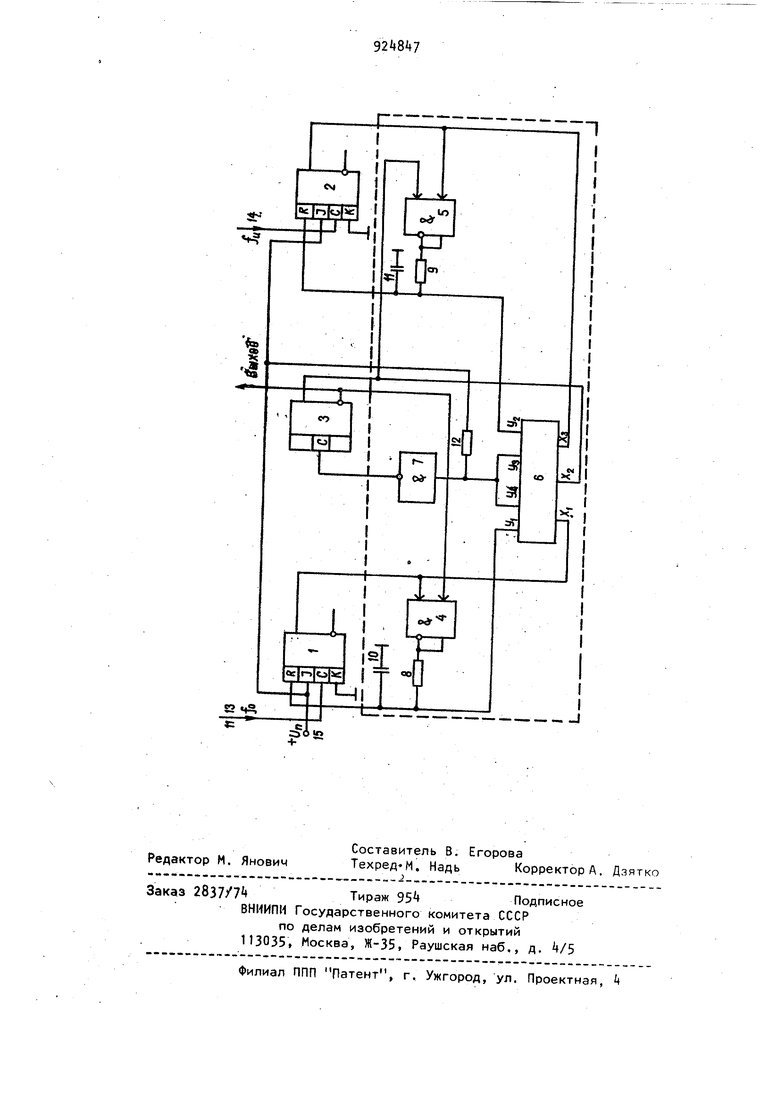

Изобретение относится к импульсной технике. Известен дискриминатор импульсо, содержащий два RS-триггера, первые входы которых соединены со входными шинами и первыми входами трехвходовы элементов И, вторые входы которых подключены к выходам триггеров, а третьи входы соединены со входными шинами, элемент НЕ, включенный межд входнойшиной и входом одного из триг геров 1. Данный дискриминатор обладает недостаточной точностью. Наиболее близким по технической сущности к предлагаемому является дискриминатор, содержащий два RS-три гера, S-вход первого из которых и R-вход второго соединены со входными шинами, а R-вход первого и S-вхо второго соединены с выходами третьего триггера со счетным входом, элемент НЕ, два интегрирующих элемента, элемент 2 И-ИЛИ-НЕ, один вход каждог элемента И соединен через интегрирующий элемент с .выходом RS-триггера, а другой вход подключен к одному из выходов третьего триггера, счетный вход которого через элемент НЕ сое-„ динен с выходом элемента 2 И-ИЛИ-НЕ 2. Недостатком данного дискриминатора является недостаточная надежность. Цель изобретения - повышение надежности. Поставленная цель достигается тем, что в дискриминатор импульсов, содержащий три триггера, счетные входы двух из которых подключены к входным шинам, а счетный вход третьего триггера соединен с выходом элемента НЕ, два элемента И-НЕ, первый вход каждого из которых подключен к выходу третьего триггера, и два интегрирующих RC-элемента, введены резистор и дешифратор, первый вход которого соединен с выходом первого триг гера и вторым входом первого элемента И-НЕ, выход которого соединрн через первый интегрирующий RC-элемент со вторым входом первого триггера и с первым выходом дешифратора, второй вход дешифратора со единен с одним из выходов третьего триггера, третий вход дешифратора . соединен с выходом второго тригге- ра и вторым входом втсрого элемента И-НЕ, выход которого через второй интегрирующий ИС-эпемент подклю-чем к второму зхо/; у второго триггера и второму выходу дешифратора, и четвертый выходы которого соединены с входом элемента НЕ и через резистор с шиной опорного напряжения. На чертеже приведена электрическая схема дискримиуатора. Дискриминатор содержит 1К-три -геры 1 и 2, триггер 3, элементы И-НЕ и S, дешифратор 6, элемент НЕ 7, интегрирующие цепи из резисторов 8 и 9 и конденсаторов 10 и 11 и резистор 12. Входные сигналы пода ны на входные шины 13 и 1, а на шину 15 подано опорное напряжение Работа дешифратора в зависимости от потенциалов напряжений, поступающих входы, поясняется табли П. р И м е .4 а н И е обозначены входы дешиф дексами У - его выходы Дискриминатор импул следующим образом.

Предположим, что в начальном состоянии триггеры находятся в состоя9

дывает триггер 1 в состояние Q,- 0. Потенциал на выходе элемента 5 равен 4 НИИ Q О, Qj О, Q(2 1, при этом на выходе элементрв и 5 единичный сигнал, а на выходе элемента 7 - левой, где буквами Q - обозначены состояния триггеров. С приходом первого импульса fg триггер. 1 опрокидывается в состоянии (1 1. На входах дешифратора при этом Х 1 , Х/2. О, Х(3 1. Согласно табл., на выходе Уг) формируется потенциал, равный О, триггер2 опрокидывается в состояние Qn О, после че го выход закрывается, его потенциал становится равным 1. ПотенцйаЛ на выходе элемента k равен 0. После окончания переходного процесса на выходе конденсатора 10 потенциал становится равным О, триггер 1 возвращается в состояние 0. 0. Таким образом, после окончания переходного процесса от первого импульса f,Q Q., О, Оз О, 0. Второй импульс fo переключает триггер 1 в состояние Q 1, По входам дешифратора Х 1, X(j О, Хт) 0. .Согласно табл. по выходу Уд формируется потенциал, равный 0. на выходе элемента 7 - потенциал, равный 1 . На выходе элемента 4 потенДиал равен 0. После окончания переходного процесса триггер J возвращается в состояние Q О, выход У4 закрывается, на выходе элемента 7 потенциал опоокидывается в О, триггер 3 опрокидывается в состояние Qj- 1. Таким образом, после окончания переходного процесса от второго импульса f о Q-i О,- От 1, Qrj 0. Как следует из анализа переходных процессов, длительность состояния , , , при котором открывается выход y-jtj дешифратора , равна времени переходных процессов триггера 1, элемента . Эта длительность .должна быть достаточной- для отпирания дешифратора 6, срабатывания элемента 7 и протекания переходных процессов. в триггере 3. Третий импульс fp перекидывает триггер 1 в состояние Q К Импульс f переключает триггер 2 в состояние Qn Ь По входам дешифратора. 1, Xrjr Ь Х 1, на выходе У дешифратора формируется потенциал, равный О, который опроки50. После окончания переходного процесса триггер 2 возвращается в состояние . Последующий импульс fo возвращает триггер 1 в состояние Q О, Если между двумя соседними импуль сами fp приходят два импульса частотой fц, то первый импульс fy переключает триггер t в состояние 0, О, второй импульс f переключает триггер 3 в состояние Цл О, При последующем чередовании импульсов fo и fу, триггеры 1 и 2 остаются в прежнем состоянии, а триггер 3 от импульсов fo переходит в со стояние Q з 1 от импульсов fj -в состояние (1-) 0. Если между двумя импульсами fg повторно приходят два импульса частотой f, то второй импульс fv( пе-рек лючает триггер 2 в состояние О о t. При последующем чередовании импульСОВ fp и f триггеры 1 и 3 остаются в прежнем состоянии, триггер 2 от импульса fg переходит в состояние (q О, от импульса fy - в состояние Если затем частота импульсов f понизится и между двумя соседними гимпульсами частотой fц придут два импульса частотой fQ, то второй импульс fo переключит триггер 3 в сост яние 0.1, 1. При последующем чередо нии, импульсов f о и триггеры 1 и 2 остаются в прежнем состоянии, а триггер 3 от импульсов f переходит состояние QT, 1 , от импульсов f, - в состояние 0.0. Анализ описания работы делителя позволяет сделать следующие выводы по технико-экономической эффективнос ти : отсутствие ложных узких импуль7сов на выходе схемы во всех режимах работы; отсутствие сбоев при совпадении во времени импульсов fp и fyj без применения специальных схем разделения импульсов. Формула изобретения Дискриминатор импульсов, содержащий три триггера, счетные входы двух из которых :подключены к входным шинам, . а счетный вход третьего триггера соединен с выходом элемента НЕ, два элемента И-НЕ, первый вход каждого из которых подключен к выходу третьего триггера , и два интегрирующих RC-элемента, отличающийся тем, что, с целью повышения надежности,в него введены резистор и дешифратор, первый вход которого соединен с выходом первого триггера и вторым входом Нервого элемента И-НЕ, выход которого соединен через первый интегрирующий RC-элемент с вторым входом первого триггера и с первым выходом дешифратора, второй вход дешифратора соединен с одним из выходов третьего триггера, третий вход дешифратора соединен с выходом второготриггера и вторым входов второго элемента И-НЕ, выход которого через второй интегрирующий RC-элемент подключен к BtopOMy входу второго триггера и второму выходу дешифратора, третий и четвертый выходы которого соединены с входом элемента НЕ и через резистор с шиной опорного напряжения. Источники информациИ( принятые во внимание при экспертизе 1.Авторское свидетельство СССР N 696598, кл. Н 03 К 5/19, 15.0(.77. 2.Авторское свидетельство СССР N , кл. Н 03 D 13/00, 30.10.78.

Авторы

Даты

1982-04-30—Публикация

1980-10-24—Подача