1

21)4313865/24-07

(22)08.10.87

(45)30.12.90. Бюл. №48

(72) Г.П.Иванова и В.В.Иьанов

(53)621.314.27(088.8)

(56)Авторское свидетельство СССР № 542323, кл. Н 02 М 7/48, 1974.

5) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ИНВЕРТОРОМ

(57)Изобретение относится к преобразовательной технике и может быть использовано для управления ключевыми элементами инвертора с синусоидально модулированным выходным напряжением. Цель изобретения- упрощение устройства. Устройство состоит из делителя частоты, счетчика, блока формирования паузы между импульсами заполнения, который содержит дешифратор, мультиплексор, формирователь реверсивного кода и RS-триггер, и блока формирования паузы между импульсами заполнения, содержащего второй мультиплексор, адресные входы которого соединены с входными шинами управления. 3 ил., 4 табл.

| название | год | авторы | номер документа |

|---|---|---|---|

| Широтно-импульсный модулятор | 1989 |

|

SU1677857A1 |

| Устройство для определения углового положения вала | 1987 |

|

SU1439739A1 |

| Устройство для измерения частоты | 1985 |

|

SU1292162A1 |

| Цифровой коррелятор | 1989 |

|

SU1711181A1 |

| Кольцевой делитель частоты | 1979 |

|

SU784006A1 |

| Устройство для регулирования скорости электродвигателя | 1984 |

|

SU1267375A1 |

| Устройство для регистрации сейсмической информации | 1984 |

|

SU1196841A1 |

| Устройство для измерения частоты | 1985 |

|

SU1372243A1 |

| Многоканальное программное задающее устройство | 1986 |

|

SU1383297A1 |

| Устройство для измерения частоты гармонического сигнала | 1987 |

|

SU1525607A1 |

Изобретение относится к преобразовательной технике и может быть использовано для управления ключевыми элементами инвертора с синусоидально-модулированным выходным напряжением. Цель изобретения - упрощение устройства. Устройство состоит из делителя частоты счетчика, блока формирования паузы между импульсами заполнения, который содержит дешифратор, мультиплексор, формирователь реверсивного кода и RS-триггер и блока формирования паузы между импульсами заполнения, содержащего второй мультиплексор, адресные входы которого соединены с входными шинами управления. 3 ил., 4 табл.

Изобретение относится к преобразовательной техншсе и может быть использовано для управления ключевыми элементами инвертора с синусоидально модулированным выходным напряжением.

Цель изобретения - упрощение схемы устройства.

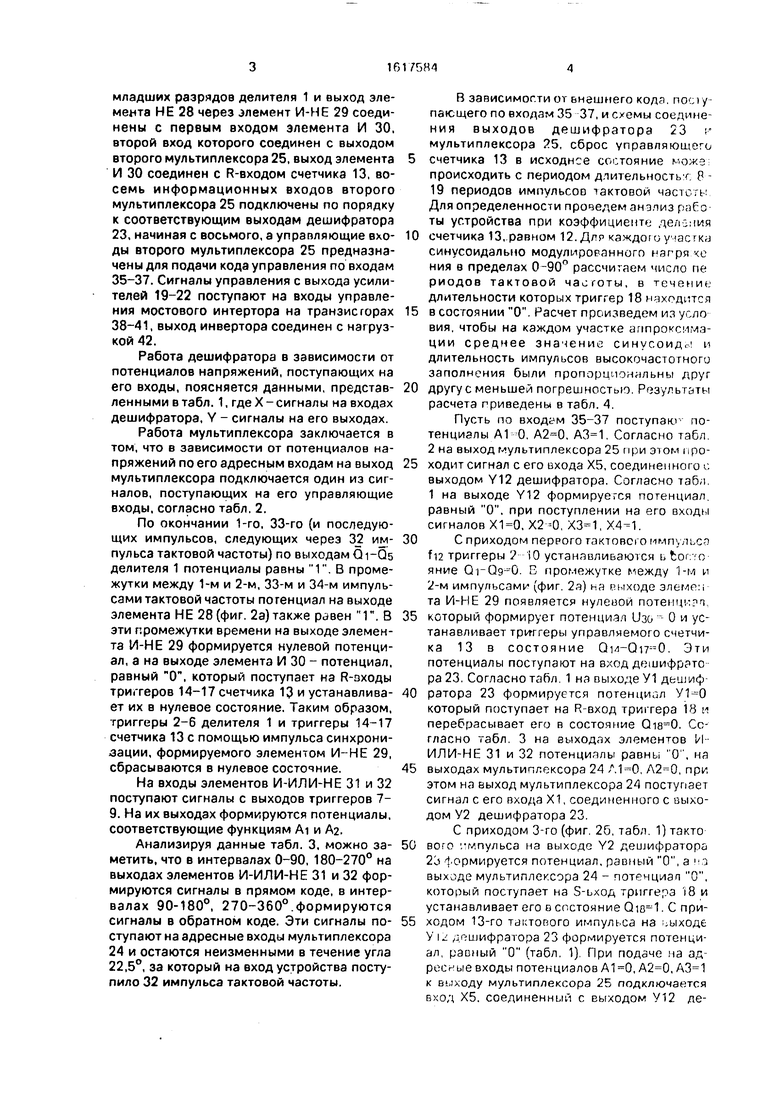

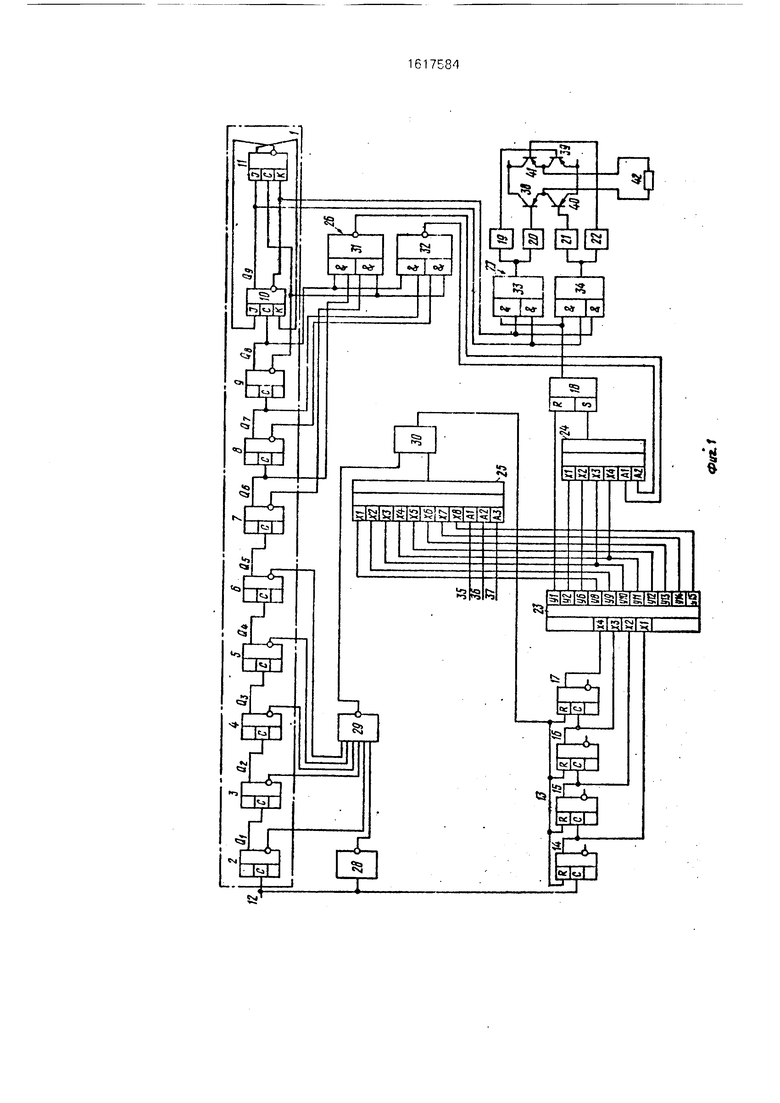

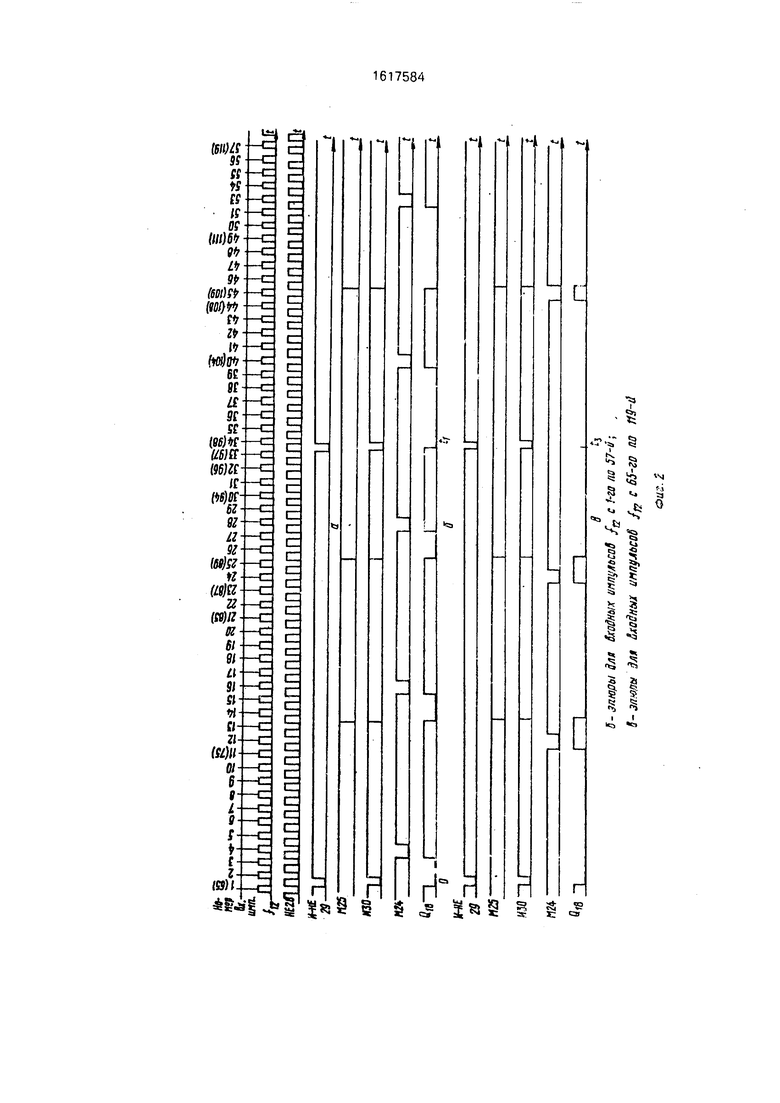

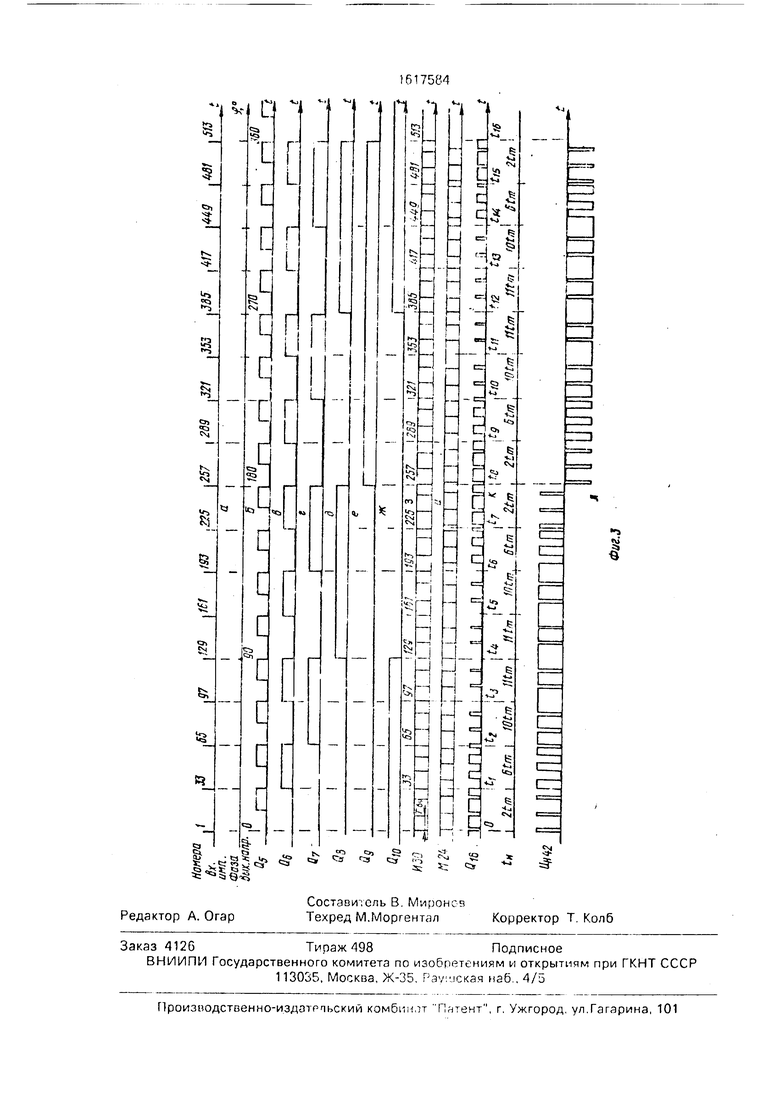

На фиг. 1 приведена принципиальная схема устройства; на фиг., 2 и 3 - временные диаграммы его работы.

Устройство (фиг. 1) содержит делитель 1 частоты на триггерах 2-11, при этом восемь младших разрядов на триггерах 2-9 пред- С1авпяют последовательный счетчик , два старших разряда на триггерах 10 и 11 включены по схеме регистра с перекрестными связями, вход 12 делителя 1 предназначен для подачи тактового сигнала, четырехразрядный счетчик 13 на триггерах 14-17, RS- триггео 18, у силители 19-22, выходы которых являются выходами устройства, дешифратор 23, два мультиплексора 24 и 25, два формирователя 26 и 27 кодов, элемент НЕ 28, элемент И-НЕ 29 и элемент И 30. Входы дешифратора 23 соединены с выходами триггеров счетчика 13, нулевой выход дешифратора 23 соединен с R-входом триггера 18, второй, шестой, десятый и одиннадцатый выходы дешифратора 23 соединены с инфомационными входами первого мультиплексора 24, входы первого формирователя

26на элементах И-ИЛИ-НЕ 31 и 32 соединены с выходами Об, О и Оз шестого, седьмого и восьмого делителя 1, этот формирователь кодов реализует функции:

AI Об -Об V бб -Us:

А2 07 -QeVU -Qe.

Выходы первого формирователя 26 соединены с управляющими входами первого мультиплексора 24, выход которого соединен с S-входом триггера 18, Q-выход триггера 18 и выход старшего разряда Од соединен с входами второго формирователя

27на элементах 33 и 34 типа И-ИЛИ-И, р.еализующе го функции:

Аз О -Оэ V Од; А О -Оэ V Qg, выходы второго формирователя 27 соединены с входами усилителей 19-22, входы счетчика 13 и элемента НЕ 28 соединены с входом делителя 1, инверсные выходы пяти

с

ел сх

младших разрядов делителя 1 и выход элемента НЕ 28 через элемент И-НЕ 29 соединены с первым входом элемента И 30, второй вход которого соединен с выходом второго мультиплексора 25, выход элемента И 30 соединен с R-входом счетчика 13, восемь информационных входов второго мультиплексора 25 подключены по порядку к соответствующим выходам дешифратора 23, начиная с восьмого, а управляющие вхо- ды второго мультиплексора 25 предназначены для подачи кода управления по входам 35-37. Сигналы управления с выхода усилителей 19-22 поступают на входы управления мостового интертора на транзисторах 38-41, выход инвертора соединен с нагрузкой 42,

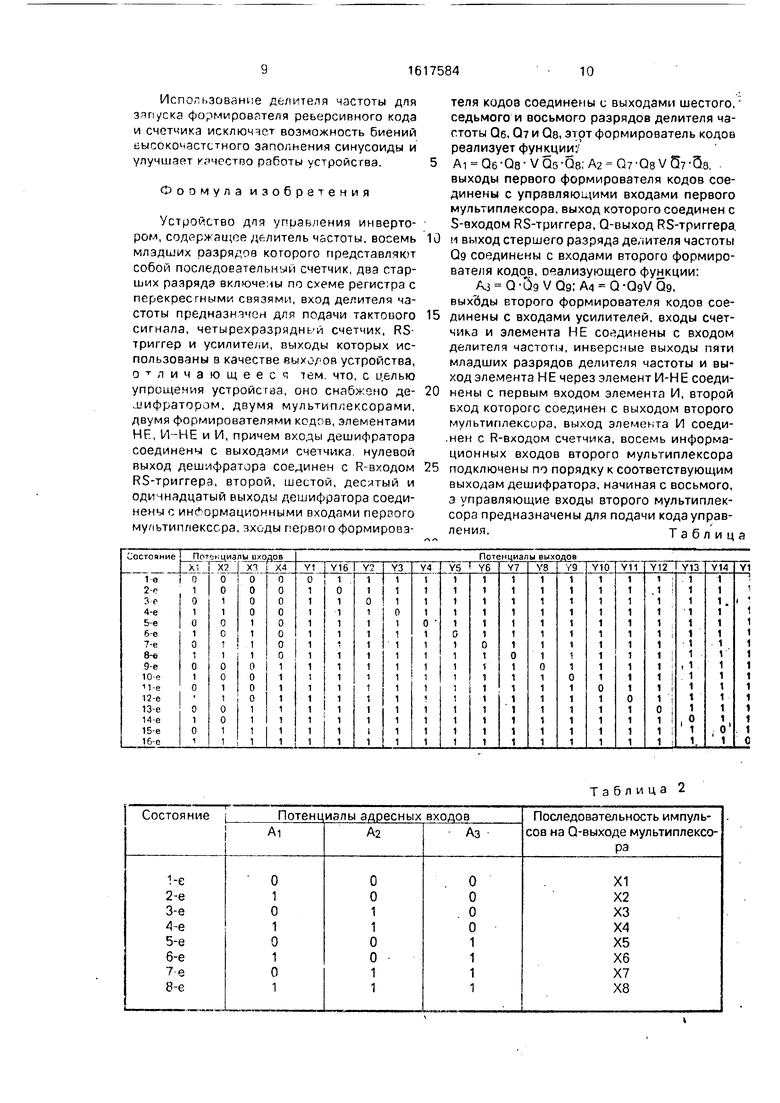

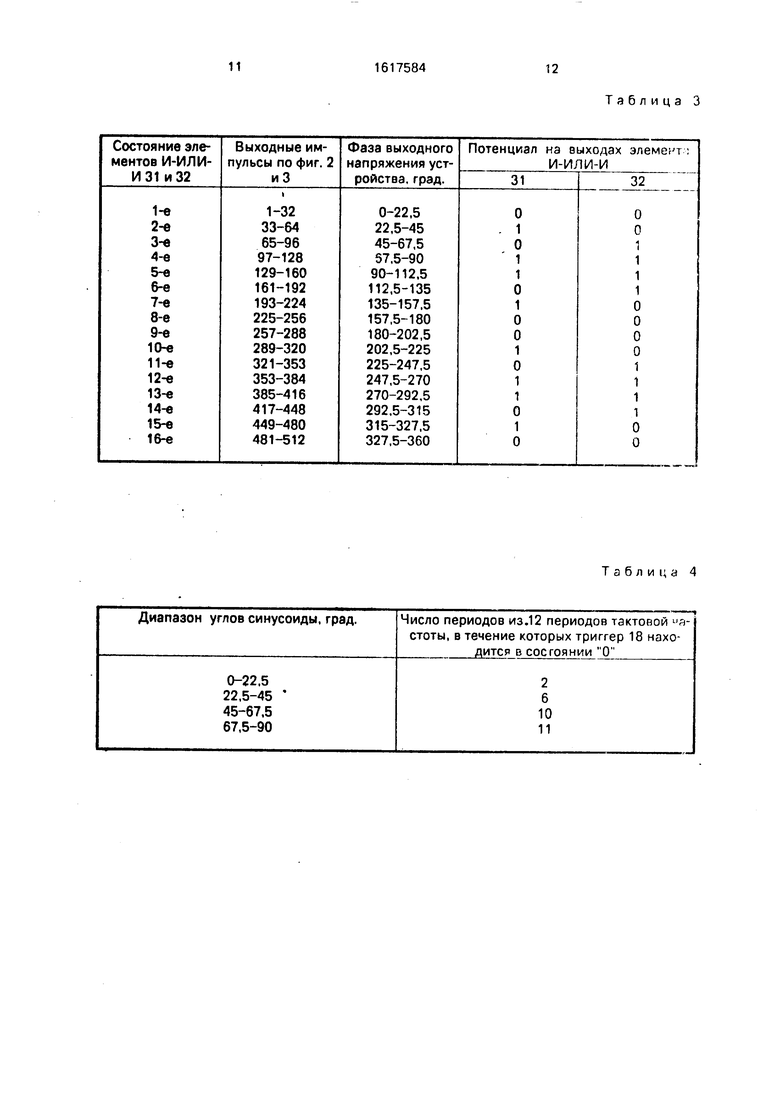

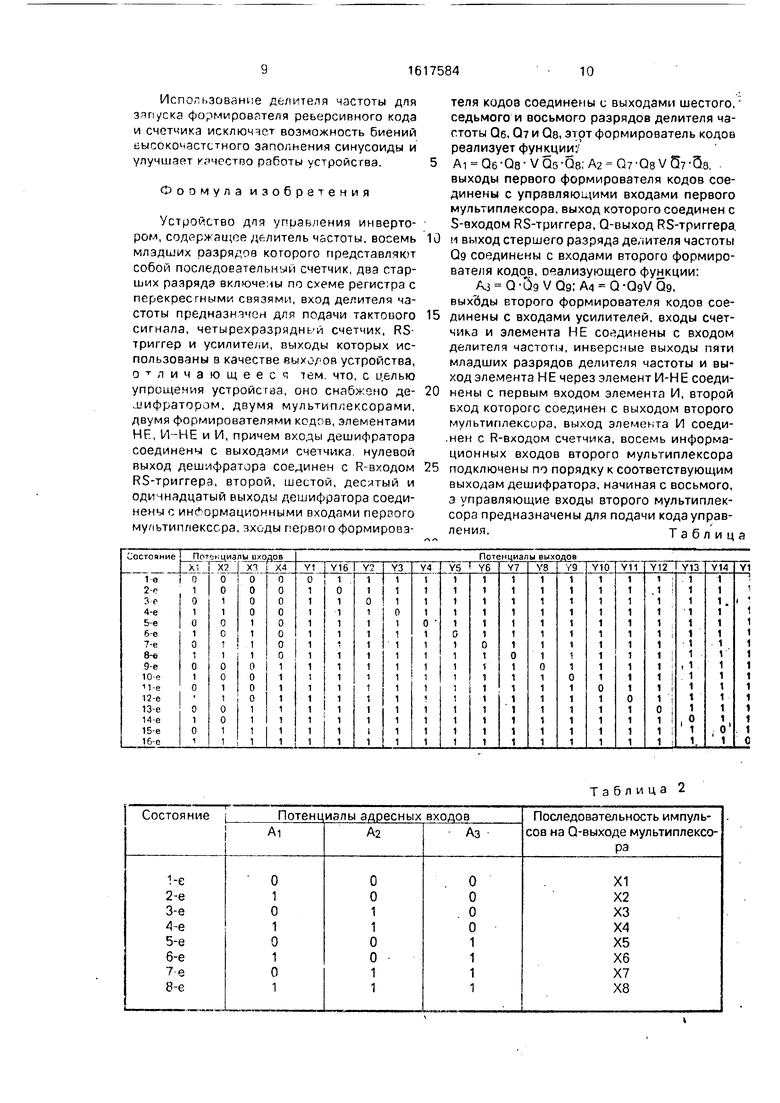

Работа дешифратора в зависимости от потенциалов напряжений, поступающих на его входы, поясняется данными, представ- ленными в табл, 1, где X - сигналы на входах дешифратора, Y - сигналы на его выходах.

Работа мультиплексора заключается в том, что в зависимости от потенциалов напряжений по его адресным входам на выход мультиплексора подключается один из сигналов, поступающих на его управляющие входы, согласно табл, 2,

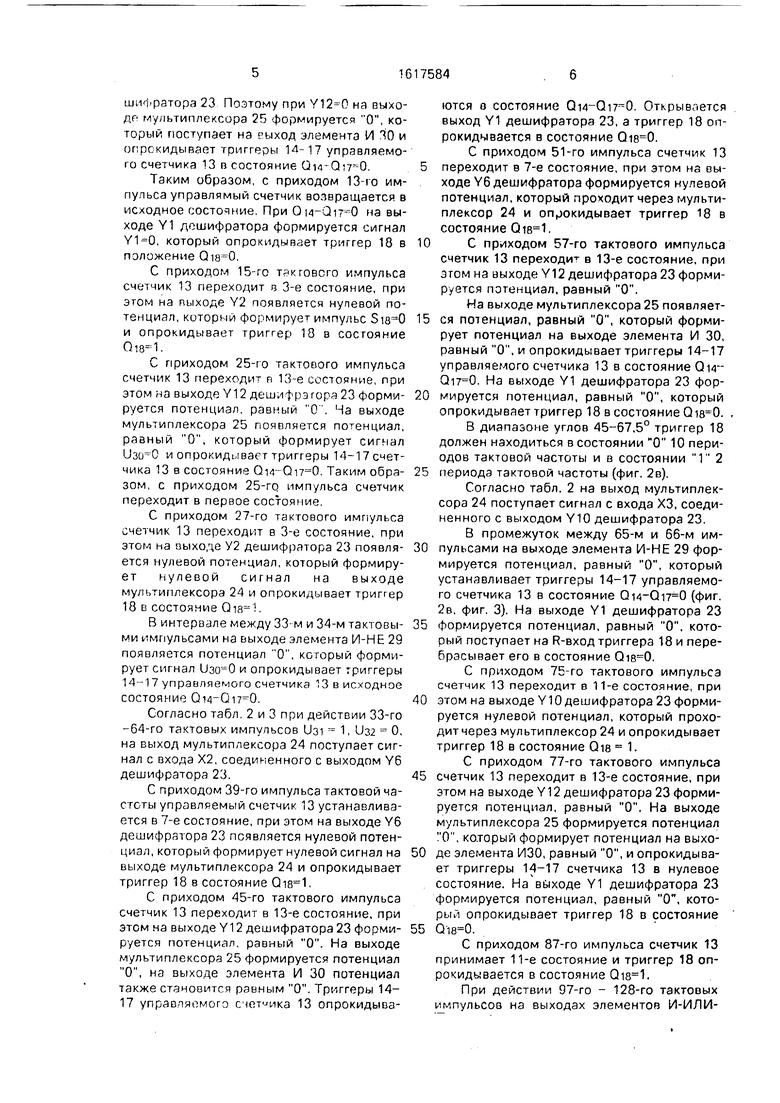

По окончании 1-го, 33-го (и последующих импульсов, следующих через 32 им- пульса тактовой частоты) по выходам Qi-Qs делителя 1 потенциалы равны 1. В промежутки между 1-м и 2-м, 33-м и 34-м импульсами тактовой частоты потенциал на выходе элемента НЕ 28 (фиг. 2а) также равен 1. В эти промежутки времени на выходе элемента И-НЕ 29 формируется нулевой потенциал, а на выходе элемента И 30 - потенциал, равный О, который поступасгт на R-зходы триггеров 14-17 счетчика 13 и устанавлива- ет их в нулевое состояние. Таким образом, триггеры 2-6 делителя 1 и триггеры 14-17 счетчика 13 с помощью импульса синхрони- ;3ации, формируемого элементом И-НЕ 29, сбрасываются в нулевое состояние.

На входы элементов И-ИЛИ-НЕ 31 и 32 поступают сигналы с выходов триггеров 7- 9. На их выходах формируются потенциалы, соответствующие функциям Ai и А2.

Анализируя данные табл. 3, можно за- метить, что в интервалах 0-90, 180-270° на выходах элементов И-ИЛИ-НЕ 31 и 32 формируются сигналы в прямом коде, в интервалах 90-180°, 270-360°.формируются сигналы в обратном коде. Эти сигналы по- ступают на адресные входы мультиплексора 24 и остаются неизменными в течение угла 22,5°, за который на вход устройства поступило 32 импульса тактовой частоты.

В зависимости от внешнего кода, пооу пающего по входам 35 37, и схемы соедпне- ния выходов дешифратора 23 г мультиплексора 25, сброс управляющего счетчика 13 в исходное состояние можэ; происходить с периодом длительность: -; 8 - 19 периодов импульсов тактовой частоты Для определенности проведем аиэ.пиз pnfo ты устройства при коэффициенте дел-зпия счетчика 13,,равном 12. Длр каждого участка синусоидально модулироранногп нагря чс ния в пределах 0-90° рассчитаем число пе риодов тактовой частоты, в течение длительности которых триггер 18 находится в состоянии О. Расчет произведем из уело ВИЯ. чтобы на каждом участке аппроксимации среднее значение синусоиду и длительность импульсов высокочастотного заполнения были пропорциональны друг другу с меньшей погрешностью. Р ззультаты расчета приведены в табл. 4.

Пусть по входам 35-37 поступаю потенциалы А1-0. . . Согласно табл. 2 на выход мультиплексора 25 при этом проходит сигнал с его входа Х5, соединенного с. выходом Y12 дешифратора. Согласно таб-i, 1 на выходе Y12 формируется потенциал. равный О, при поступлении на его входы сигналов , Х2 0. , Х4-1.

С приходом первого тактового импульсо fi2 триггеры 210 устанавливаются ь tor/fo яние Qi-Q9- 0. Е промежутке между 1-м и 2-м импульсами (фиг. 2я) на выходе элеме: та И-НЕ 29 появляется нулевой noTenuvvn который формирует потенциал изо - - О и устанавливает тр1 ггеры управляемого счетчика 13 в состояние Qi/i-Qi7 0. Эти потенциалы поступают на вход дешифрато ра23. Согласно табл. 1 на выходе У1 дешифратора 23 формируется потенциал который поступает на R-вход триггера 18 i перебрасывает его в состояние . Согласно табл. 3 на выходах элементов И- ИЛИ-ИЕ 31 и 32 потенциалы равны О, на выходах мультиплексора 24 . , при этом на выход мультиплексора 24 поступает сигнал с его входа XI, соединенного с выходом У2 дешифратора 23.

С приходом 3-го (фиг. 26, табл. 1) такто вого . мпульса на выходе Y2 дeuJифpaтopй 2о формируется потенциал, равный О, а мо выходе мультиплексора 24 - лотечциап О, который поступает на S-ьход триггера 18 и устанавливает его в состояние . С приходом 13-го тактового импульса на - ыходе У 1 дешифратора 23 формируется потенциал, равный О (табл. 1), При подаче на адресные входы потенциалов , , к мультиплексора 2Б подключается вход Х5. соединенный с выходом У12 деши 1|ратора 23 Поэтому при на выходе мультиплексора 25 формируется О, который поступает на еыход элемента И ЛО и опрокидывает триггеры управляемого счетчика 13 в состояние Qi4-Qi7 0.

Таким образом, с приходом 13-го импульса управлямый счетчик возвращается в исходное состояние. При Ои-й17 0 на выходе Y1 дешифратора формируется сигнал , который опрокидывает триггер 18 в положение .

С приходом 15-го тэкгового импульса счетчик 13 переходит в 3-е состояние, при этом на пыходе Y2 появляется нулевой потенциал, который формирует импульс и опрокидывает триггер 18 в состояние

.

С приходом 25-го тактового импульса счетчик 13 переходит п 13-е состояние, при этом на выходе Y12 дешифрэгора 23 формируется потенциал, равный О, Ча выходе мультиплексора 25 появляется потенциал, равный О, который формирует сигнал и опрокидывает триггеры 14-17 счетчика 13 в состояние Qi4-Qi7 0, Таким образом, с приходом 25-го импульса счетчик переходит в первое состояние,

С приходом 27-го тактового импульса счетчик 13 переходит в 3-е состояние, при этом на выходе У2 дешифратора 23 появляется нулевой потенциал, который формирует нулевой сигнал на выходе мультиплексора 24 и опрокидывает триггер 18 в состояние .

В интервале между 33-м и 34-м тактовыми импульсами на выходе элемента И-НЕ 29 появляется потенциал О, который формирует сигнал и опрокидывает триггеры 14-17 управляемого счетчика 13 в исходное состояние .

Согласно табл. 2 и 3 при действии 33-го -64-го тактовых импульсов Uai 1, U32 О, на выход мультиплексора 24 поступает сигнал с входа Х2, соединенного с выходом Y6 дешифратора 23.

С приходом 39-го импульса тактовой частоты управляемый счетчик 13 устанавливается в 7-е состояние, при этом на выходе Y6 дешифратора 23 появляется нулевой потенциал, который формирует нулевой сигнал на выходе мультиплексора 24 и опрокидывает триггер 18 в состояние .

С приходом 45-го тактового импульса счетчик 13 переходит в 13-е состояние, при этом на выходе Y12 дешифратора 23 формируется потенциал, равный О. На выходе мультиплексора 25 формируется потенциал О, на выходе элемента И 30 потенциал также становится равным О. Триггеры 14- 17 управляемого счет пжа 13 опрокидываются а состояние Qi4-Qi7 0. Открывается выход Y1 дешифратора 23, а триггер 18 опрокидывается в состояние ,

С приходом 51-го импульса счетчик 13 5 переходит в 7-е состояние, при этом на выходе Y6 дешифратора формируется нулевой потенциал, который проходит через мультиплексор 24 и опрокидывает триггер 18 в состояние .

10 С приходом 57-го тактового импульса счетчик 13 переходит в 13-е состояние, при этом на выходе Y12 дешифратора 23 формируется потенциал, равный О,

Wa выходе мультиплексора 25 появляет- 15 ся по1енциал, равный О, который формирует потенциал на выходе элемента И 30, равный О, и опрокидывает триггеры 14-17 управляемого счетчика 13 в состояние Qi/j- . На выходе Y1 дешифратора 23 фор- 0 мируется потенциал, равный О, который опрокидывает триггер 18 в состояние . В диапазоне углов 45-67,5° триггер 18 должен находиться в состоянии О 10 периодов тактовой частоты и в состоянии 1 2 5 периода тактовой частоты (фиг, 2в).

Согласно табл, 2 на выход мультиплексора 24 поступает сигнал с входа ХЗ, соединенного с выходом Y10 дешифратора 23.

В промежуток между 65-м и 66-м им- 0 пульсами на выходе элемента И-НЕ 29 формируется потенциал, равный О, который устанавливает триггеры 14-17 управляемого счетчика 13 в состояние Qi4-Qi7 0 (фиг. 2в, фиг. 3). На выходе Y1 дешифратора 23 5 формируется потенциал, равный О, который поступает на R-вход триггера 18 и перебрасывает его в состояние ,

С приходом 75-го тактового импульса счетчик 13 переходит в 11-е состояние, при 0 этом на выходе Y10 дешифратора 23 формируется нулевой потенциал, который проходит через мультиплексор 24 и опрокидывает триггер 18 в состояние Qi8 1.

С приходом 77-го тактового импульса 5 счетчик 13 переходит в 13-е состояние, при этом на выходе Y12 дешифратора 23 формируется потенциал, равный О, На выходе мультиплексора 25 формируется потенциал О, который формирует потенциал на выхо- 0 де элемента ИЗО, равный О, и опрокидывает триггеры 14-17 счетчика 13 в нулевое состояние. На вс 1ходе Y1 дешифратора 23 формируется потенциал, равный О, который опрокидывает триггер 18 в состояние 5 .

С приходом 87-го импульса счетчик 13 принимает 11-е состояние и триггер 18 опрокидывается в состояние .

При действии 97-го - 128-го тактовых импульсов на выходах элементов И-ИЛИНЕ 31 и 32 согласно табл. 4 потенциалы равны Г. Согласно табл. 2 на выходе мультиплексора 24 формируется сигнал, равный сигналу с входа Х4, соединенного с выходом Y11 дешифратора 23.

В промежуток между 97-м и 98-м импульсами тактовой частоты (фиг. 2в) на выходе элемента И-НЕ 29 формируется потенциал, равный О, который устанавли- ваеттриггеры 14-17 счетчика 13 всостояние Qi4-Qi7 0. На выходе Y1 дешифратора 23 формируется потенциал , который поступает на R-вход триггера 18 и подтверждает состояние Qi8 0.

С приходом 108-го тактового импульса счетчик 13 переходит в 12-е состояние, при этом на выходе Y11 дешифратора 23 формируется нулевой потенциал, который сбрасывает триггер 18.

С приходом 109-го импульса счетчик 13 переходит в 13-е состояние, при этом на выходе Y13 дешифратора 23 формируется потенциал, равный О, на выходе элемента И 30 потенциал становится также равным О. Триггеры 14-17 управляемого счетчика 13 опрокидываются в состояние Qi4-Qi7 0. На выходе Y1 дешифратора 23 , .

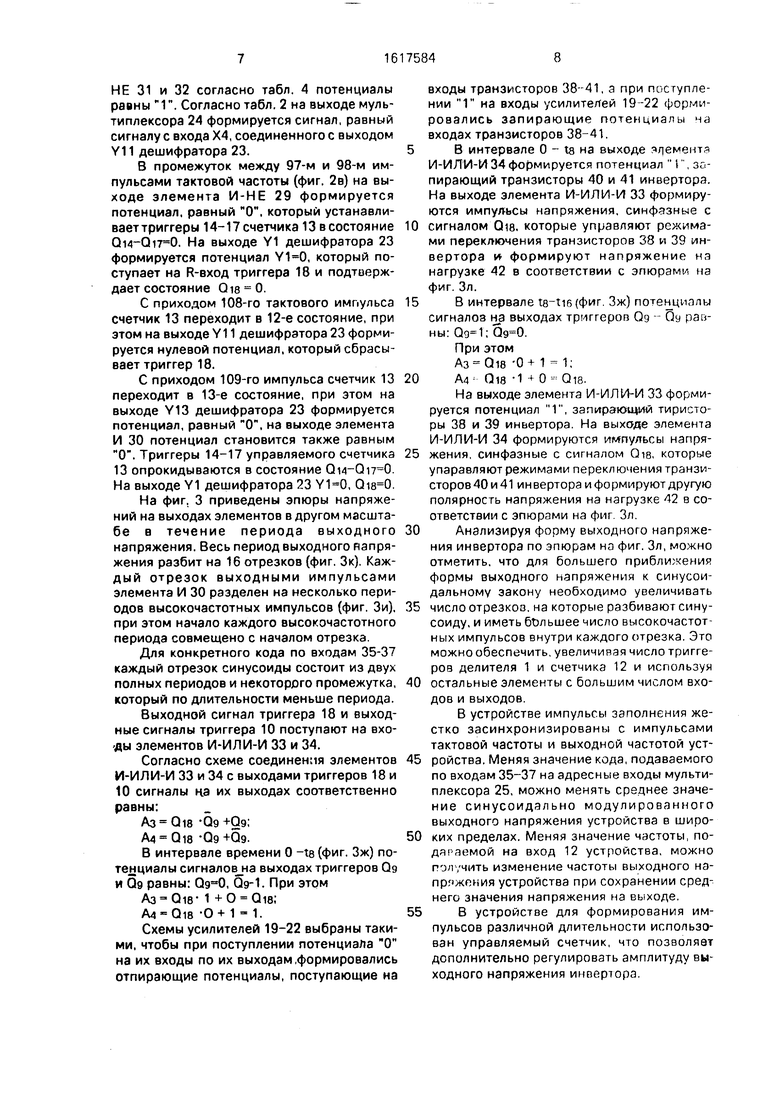

На фиг. 3 приведены эпюры напряжений на выходах элементов в другом масштабе в течение периода выходного напряжения. Весь период выходного вапря- жения раэбит на 16 отрезков (фиг. Зк). Каждый отрезок выходными импульсами элемента И 30 разделен на несколько периодов высокочастотных импульсов (фиг. Зи), при этом начало каждого высокочастотного периода совмещено с началом отрезка.

Для конкретного кода по входам 35-37 каждый отрезок синусоиды состоит из двух полных периодов и некоторого промежутка, который по длительности меньше периода.

Выходной сигнал триггера 18 и выходные сигналы триггера 10 поступают на вхо- ды элементов И-ИЛИ-И 33 и 34.

Согласно схеме соединения элементов И-ИЛИ-И 33 и 34 с выходами триггеров 18 и 10 сигналы на их выходах соответственно равны:

A3 Qi8 -Qg-t-Qg;

A4 Qi8 -Qg+Qg.

В интервале времени О -ta (фиг. Зж) по- те 1циалы сигналов на выходах триггеров Qg и Qg равны: , Qg-1. При этом

A3 Qi8- 1 +0 018;

A4 Ol8 -0+1 1.

Схемы усилителей 19-22 выбраны такими, чтобы при поступлении потенциала О на их входы по их выходам .формировались отпирающие потенциалы, поступающие на

ходы транзисторов 38-41, а при поступлении 1 на входы усилите/тай 19-22 формировались запирающие потенциалы на входах транзисторов 38-41.

В интервале О - te на выходе я/1ементэ

И-ИЛ И-И 34 формируется потенциал t, запирающий транзисторы 40 и 41 инвертора. На выходе элемента И-ИЛИ-И 33 формируются импудьсы напряжения, синфазные с

сигналом Qi8, которые управляют режимами переключения транзисторов 38 и 39 инвертора 1 формируют напряжение на нагрузке 42 в соответствии с эпюрами на фиг. 3л.

В интервале Т8-Х1б{фиг. Зж) потен циалы

сигналов на выходах триггеров Qg -- Q9 равны: . При этом Аз 018 -0+ 1 1;

А4- Oi8 -1 +0 Qi8.

На выходе элемента И-ИЛИ-И 33 формируется потенциал 1, запирающий тиристоры 38 и 39 инвертора. На выходе элемента И-ИЛИ-И 34 формируются импульсы напряжения, синфазные с сигналом QIB, которые упаравляют режимами переключения транзисторов 40и41 инвертора иформируют другую полярность напряжения на нагрузке 42 в соответствии с эпюрами на фиг. 3л.

Анализируя форму выходного напряжения инвертора по эпюрам на фиг. 3л, можно отметить, что для большего приближения формы выходного напряжения к синусоидальному закону необходимо увеличивать

число отрезков, на которые разбивают синусоиду, и иметь бЪльшее число высокочастотных импульсов внутри каждого отрезка. Это можно обеспечить, увеличивая число триггеров делителя 1 и счетчика 12 и используя

остальные элементы с большим числом входов и выходов.

В устройстве импульсы заполнения жестко засинхронизированы с импульсами тактовой частоты и выходной частотой устройства. Меняя значение кода, подаваемого по входам 35-37 на адресные входы мультиплексора 25, можно менять среднее значение синусоидально модулированного выходного напряжения устройства в широких пределах. Меняя значение частоты, по- дапаемой на вход 12 устройства, можно гол /чить изменение частоты выходного напряжения устройства при сохранении среднего значения напряжения на выходе.

В устройстве для формирования импульсов различной длительности использован управляемый счетчик, что позволяет дополнительно регулировать амплитуду выходного напряжения инвертора.

Использование делителя частоты для запуска формирователя реверсивного кода и счетчика исключает возможность биений еысокочастстного заполнения синусоиды и улучшает к, 1чест(зо работы устройства.

Фоомула изобретения

Устройство дня управления инверто- ром, содержащее делитель частоты, восемь младших разрядов которого представляют собой последовательный счетчик, два старших разряда включены по схеме регистра с перекрестными связями, вход делителя частоты предназначен для подачи тактового сигнала, четырехразрядный счетчик, RS- триггер и усилители, выходы которых использованы в качестве выходов устройства, о личающееся тем, что, с целью упроа1ения устройства, оно снабжено де- .иифратором, двумя мультиплексорами, двумя формирователями кодов, элементами НЕ, И-НЕ и А, причем входы дешифратора соединены с выходами счетчика, нулевой выход дешифратора соединен с R-входом RS-триггера, второй, шестой, десятый и одиннадцатый выходы дешифратора соединены с информационными входами первого мультиплексора, зходы первого формирователя кодов соединены с выходами шестого, седьмого и восьмого разрядов делителя ча- г.тоты Об, Qv и Qe, этот формирователь кодов реализует функции;/

AI Об -Qs V Qs -QB; А2 Q -Qs V S -За, выходы первого формирователя кодов соединены с управляющими входами первого мультиплексора, выход которого соединен с 8-0ходом RS-триггера, Q-выход RS-триггера, и выход стершего разряда делителя частоты Оэ соединены с входами второго формирователя кодов, оеализующего функции:

/V3 Q -Sg V Qg; А4 Q -QgV Qg, выходы второго формирователя кодов соединены с входами усилителей, входы счетчика и элемента НЕ соединены с входом делителя частоты, инверсные выходы пяти младших разрядов делителя частоты и выход элемента НЕ через элемент И-НЕ соединены с первым входом элемента И, второй вход которого соединен с выходом второго мультиплексора, выход элемента И соеди- .нен с R-входом счетчика, восемь информационных входов второго мультиплексора подключены по порядку к соответствующим выходам дешифратора, начиная с восьмого, а управляющие входы второго мультиплексора предназначены для подачи кода управ- ленил,Табл иц

Таблица

Диапазон углов синусоиды, град.

0-22.5 22.5-45 45-67.5 67,5-90

Таблица 3

Таблица 4

Число периодов из.12 периодов тактовой ястоты, в течение которых триггер 18 нахо- дитср в состоянии О

2 6 10 11

Авторы

Даты

1990-12-30—Публикация

1987-10-08—Подача