1шина данных

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство на цилиндрических магнитных доменах | 1987 |

|

SU1451768A1 |

| Запоминающее устройство | 1987 |

|

SU1495849A1 |

| Запоминающее устройство с произвольной выборкой | 1988 |

|

SU1548790A1 |

| Имитатор для тестирования компонентов моноканальной локальной вычислительной сети | 1987 |

|

SU1446621A1 |

| Устройство для обмена информацией | 1985 |

|

SU1334151A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Устройство для контроля доменной памяти | 1988 |

|

SU1501160A1 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ЭЛЕКТРОННЫХ СРЕДСТВ АВТОМАТИЗАЦИИ | 2005 |

|

RU2279718C1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1688229A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ БУФЕРНОЙ ПАМЯТЬЮ | 1990 |

|

RU2010317C1 |

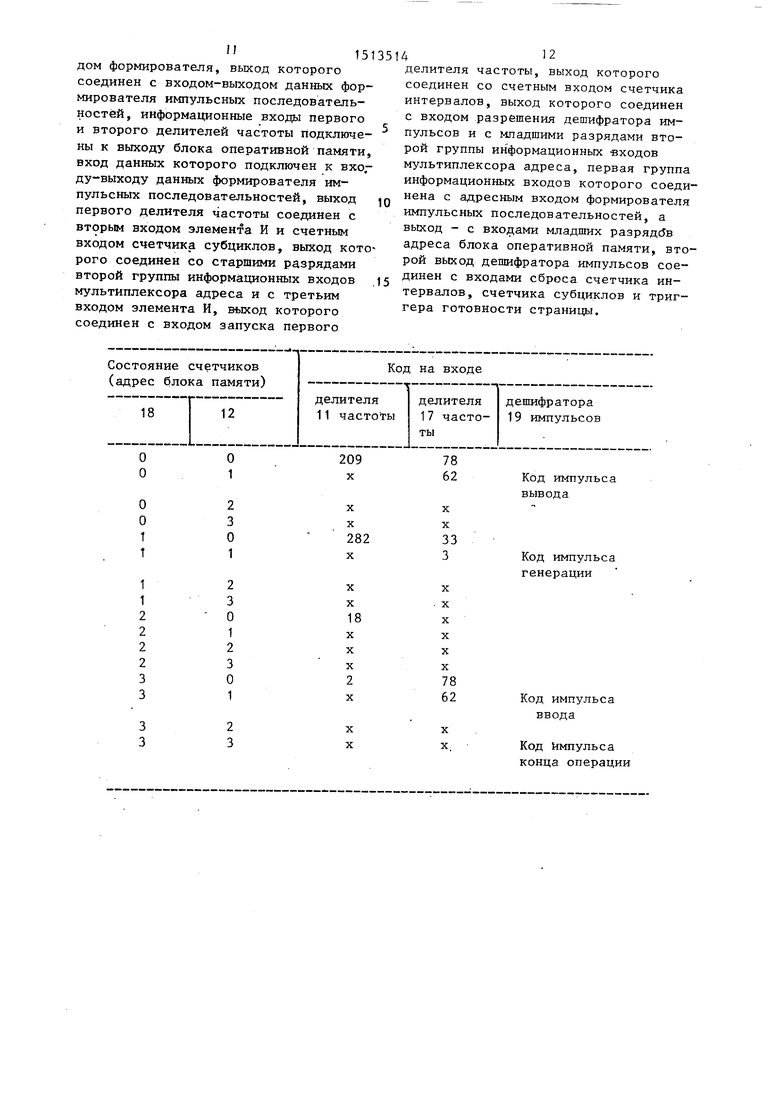

Изобретение относится к вычислительной технике и может быть использовано при разработке запоминающих устройств на цилиндрических магнитных доменах. Цель изобретения - расширение области применения формирователя импульсных последовательностей путем контроля запоминающих модулей различных типов. Устройство содержит дешифратор 4 адреса, регистр 5 режима работы, генератор 6, триггер 7 разрешения поля, счетчик 8 фаз поля, блок 9 адресации страницы, триггер 10 готовности страницы, делитель 11 частоты, счетчик 12 субциклов, формирователь 13, элемент И 14, мультиплексор 15 адресов, блок 16 оперативной памяти, делитель 17 частоты, счетчик 18 интервалов и дешифратор 19 импульсов с соответствующими функциональными связями. 3 ил.

ел

00 СП

фиг.1

3151

Изобретение относится к вычислительной технике и может быть использовано при разработке запоминающих устройств на цилиндрических магнитных доменах (ЦМД).

Цель изобретения - распшрение области применения формирователя импульсных последовательностей путем контроля запоминающих модулей различных типов.

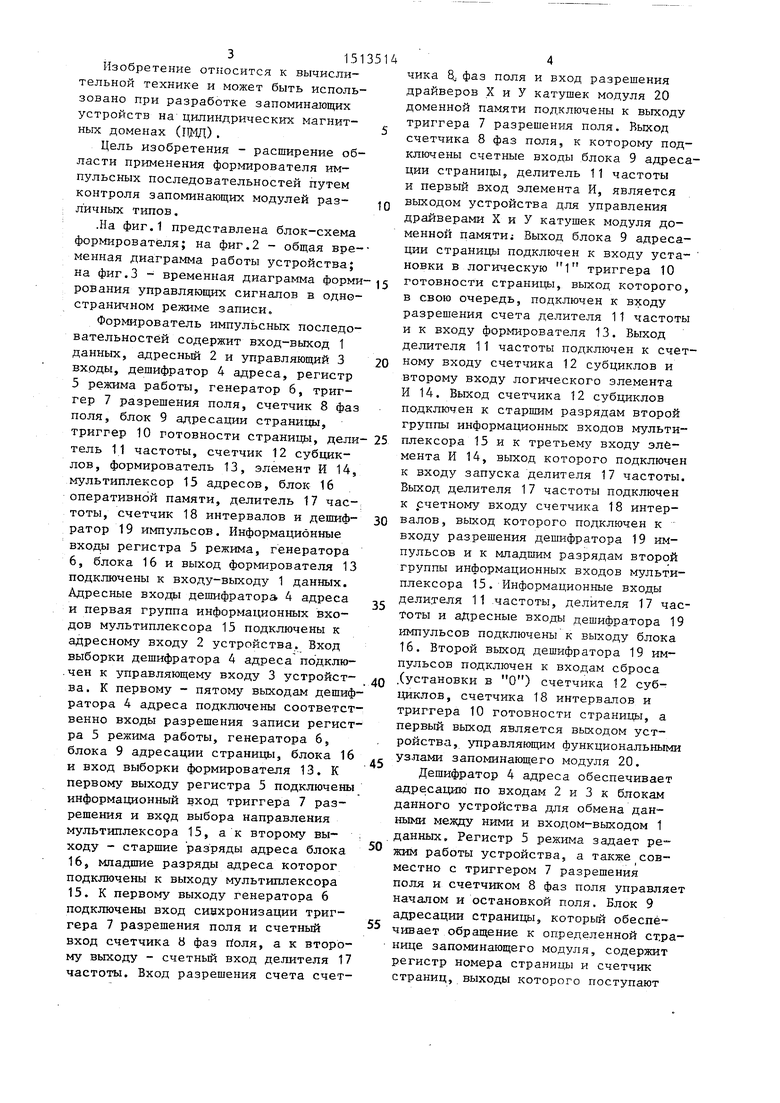

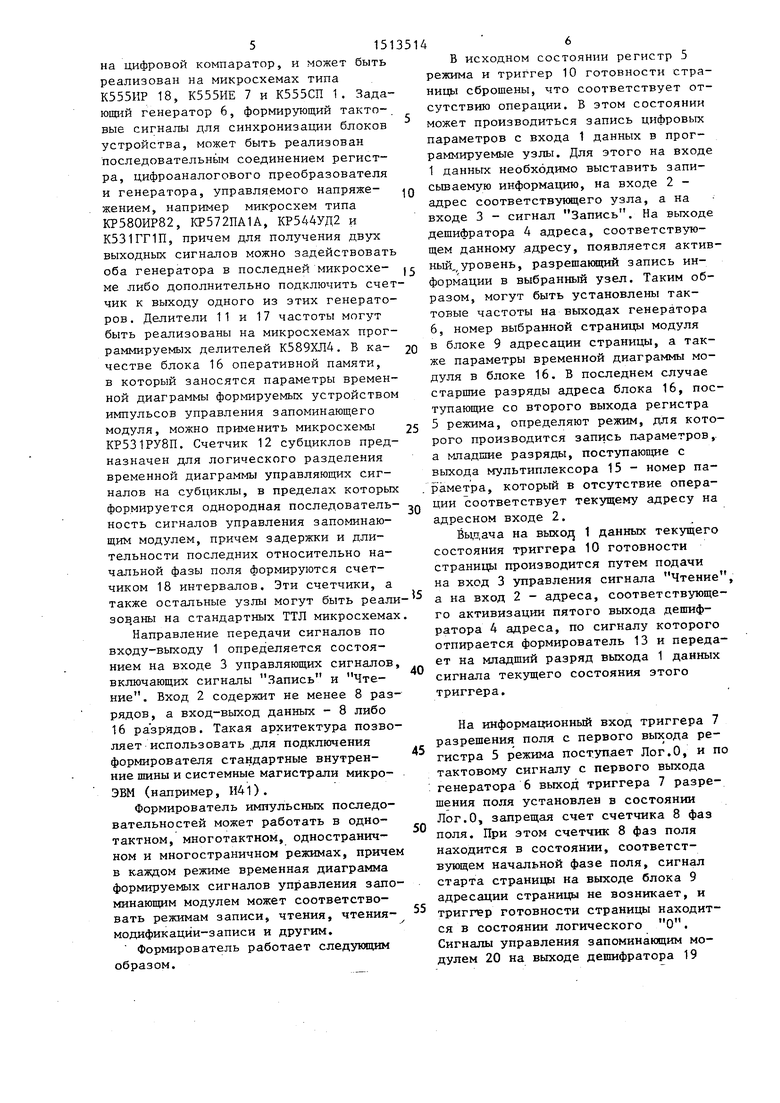

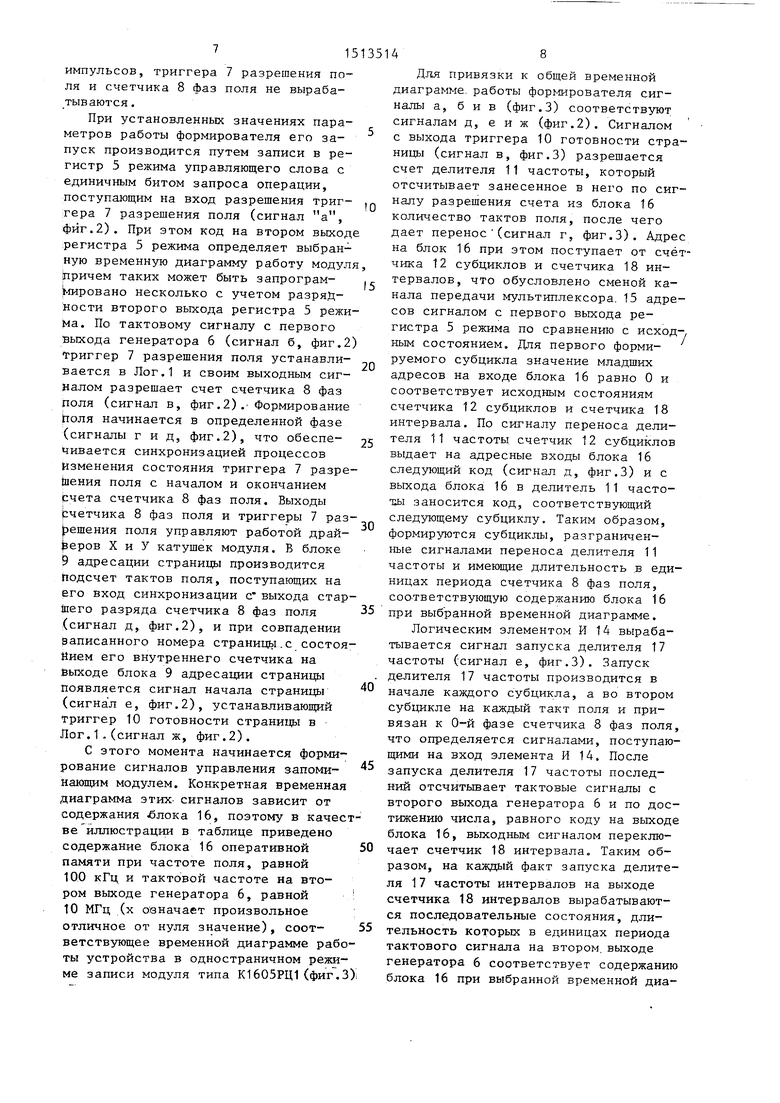

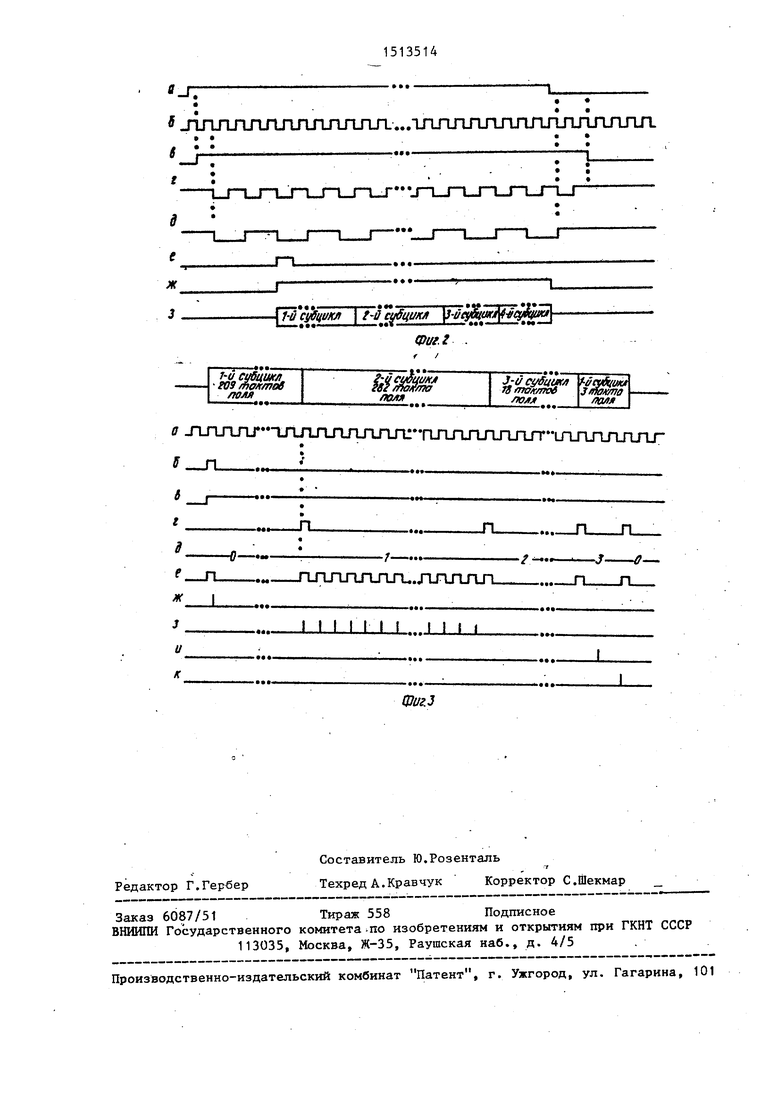

.На фиг.1 представлена блок-схема формирователя; на фиг.2 - общая временная диаграмма работы устройства; на фиг.З - временная диаграмма форми рования управляющих сигналов в одно- страничном режиме записи.

Формирователь импульсных последовательностей содержит вход-выход 1 данных, адресный 2 и управляющий 3 входы, дешифратор 4 адреса, регистр 5 режима работы, генератор б, триггер 7 разрешения поля, счетчик 8 фаз поля, блок 9 адресации страницы, триггер 10 готовности страницы, дели тель 11 частоты, счетчик 12 субциклов, формирователь 13, элемент И 14, мультиплексор 15 адресов, блок 16 оперативной памяти, делитель 17 частоты, счетчик 18 интервалов и дешифратор 19 импульсов. Информационные вход,ы регистра 3 режима, генератора 6, блока 16 и выход формирователя 13 подключены к входу-выходу 1 данных. Адресные входы дешифратора 4 адреса и первая группа информационных входов мультиплексора 15 подключены к адресному входу 2 устройства. Вход выборки дешифратора 4 адреса подклю- .чен к управляющему входу 3 устройства. К первому - пятому выходам дешифратора 4 адреса подключены соответственно входы разрешения записи регистра 5 режима работы, генератора 6, блока 9 адресации страницы, блока 16 и вход выборки формирователя 13. К первому выходу регистра 5 подключены информационный вход триггера 7 разрешения и вхдд выбора направления мультиплексора 15, а к второму вы- ходу - старшие разряды адреса блока 16, младшие разряды адреса которог подключены к выходу мультиплексора 15. К первому выходу генератора 6 подключены вход синхронизации триггера 7 разрешения поля и счетный вход счетчика В фаз Поля, а к второму выходу - счетный вход делителя 17 частоты. Вход разрешения счета счет

0

5

0 25

30

35

40

45

50

55

чика 8,- фаз поля и вход разрешения драйверов X и У катушек модуля 20 доменной памяти подключены к выходу триггера 7 разрешения поля. Выход счетчика 8 фаз поля, к которому подключены счетные входы блока 9 адресации страницы, делитель 11 частоты и первый вход элемента И, является выходом устройства для управления драйверами X и У катушек модуля доменной памяти; Выход блока 9 адресации страницы подключен к входу уста- новки в логическую 1 триггера 10 готовности страни11;ы, выход которого, в свою очередь, подключен к входу разрешения счета делителя 11 частоты и к входу формирователя 13. Выход делителя 11 частоты подключен к счетному входу счетчика 12 субциклов и второму входу логического элемента И 14. Выход счетчика 12 субциклов подключен к старшим разрядам второй группы информационных входов мультиплексора 15 и к третьему входу элемента И 14, выход которого подключен к входу запуска делителя 17 частоты. Выход делителя 17 частоты подключен к счетному входу счетчика 18 интервалов , выход которого подключен к входу разрешения дешифратора 19 импульсов и к младшим разрядам второй группы информационных входов мультиплексора 15. Информационные входы делителя 11 .частоты, делителя 17 частоты и адресные входы дешифратора 19 импульсов подключены к выходу блока 16. Второй выход дешифратора 19 импульсов подключен к входам сброса .(установки в О) счетчика 12 субциклов, счетчика 18 интервалов и триггера 10 готовности страницы, а первый выход является выходом устройства, управляющим функциональными узлами запоминающего модуля 20.

Дешифратор 4 адреса обеспечивает адресаьрсо по входам 2 и 3 к блокам данного устройства для обмена данными между ними и входом-выходом 1 данных. Регистр 5 режима задает режим работы устройства, а также совместно с триггером 7 разрешения поля и счетчиком 8 фаз поля управляет началом и остановкой поля. Блок 9 адресации страницы, который обеспечивает обращение к определенной странице запоминающего модуля, содержит регистр номера страницы и счетчик страниц, выходы которого поступают

на цифровой компаратор, и может быть реализован на микросхемах типа К555ИР 18, К555ИЕ 7 и К555СП 1. Задающий генератор 6, формирующий тактовые сигналы для синхронизации блоков устройства, может быть реализован последователъньтм соединением регистра, цифроаналогового преобразователя и генератора, управляемого напряже- жением, например микросхем типа КР580ИР82, КР572ПА1А, КР544УД2 и К531ГГ1П, причем для получения двух выходных сигналов можно задействовать оба генератора в последней микросхеме либо дополнительно подключить счет чик к выходу одного из этих генераторов. Делители 11 и 17 частоты могут быть реализованы на микросхемах программируемых делителей К589ХЛ4. В качестве блока 16 оперативной памяти, в который заносятся параметры временной диаграммы формируемых устройством импульсов управления запоминающего модуля, можно применить микросхемы КР531РУ8П. Счетчик 12 субциклов предназначен для логического разделения временной диаграммы управляющих сигналов на субциклы, в пределах которых формируется однородная последовательность сигналов управления запоминающим модулем, причем задержки и длительности последних относительно начальной фазы поля формируются счетчиком 18 интервалов. Эти счетчики, а также остальные узлы могут быть реали зов.аны на стандартных ТТЛ микросхемах

Направление передачи сигналов по входу-выходу 1 определяется состоянием на входе 3 управляющих сигналов, включающих сигналы Запись и Чтение . Вход 2 содержит не менее 8 разрядов , а вход-выход данных - В либо 16 разрядов. Такая архитектура позволяет использовать для подключения формирователя стандартные внутренние шины и системные магистрали микро- ЭВМ (например, И41).

Формирователь импульсных последовательностей может работать в одно- тактном, многотактном, одностранич- ном и многостраничном режимах, причем в каждом режиме временная диаграмма формируемых сигналов управления запоминающим модулем может соответствовать режимам записи, чтения, чтения- модификацйи-записи к другим.

Формирователь работает следующим образом.

10

15

20

25

30

5

40

45

50

55

В исходном состоянии регистр 5 режима и триггер 10 готовности страницы сброшены, что соответствует отсутствию операции. В этом состоянии может производиться запись цифровых параметров с входа 1 данных в программируемые узлы. Для этого на входе 1 данных необходимо выставить записью аемую информацию, на входе 2 - адрес соответствукйцего узла, а на входе 3 - сигнал Запись. На выходе дешифратора 4 адреса, соответствующем данному .адресу, появляется активный,, уровень, разрешакяций запись информации в выбранный узел. Таким образом, могут быть установлены тактовые частоты на выходах генератора 6, номер выбранной страницы модуля в блоке 9 адресации страницы, а также параметры временной диаграммы модуля в блоке 16. В последнем случае старшие разряды адреса блока 16, поступающие со второго выхода регистра 5 реткима, определяют режим, для которого производится запись параметров,, а младшие разряды, поступаюпще с выхода мультиплексора 15 - номер параметра, который в отсутствие операции соответствует текущему адресу на адресном входе 2.

Вьщача на Bbixojj 1 данных текущего состояния триггера 10 готовности страницы производится путем подачи на вход 3 управления сигнала Чтение, а на вход 2 - адреса, соответствующего активизации пятого выхода дешифратора 4 адреса, по сигналу которого отпирается формирователь 13 и передает на младший разряд выхода 1 данных сигнала текущего состояния этого триггера.

На информационный вход триггера 7 разрешения поля с первого выхода регистра 5 режима поступ.ает Лог.О, и по тактовому сигналу с первого выхода генератора 6 выход триггера 7 разрешения поля установлен в состоянии Лог.О, запрещая счет счетчика 8 фаз поля. При этом счетчик 8 фаз поля находится в состоянии, соответствующем начальной фазе поля, сигнал старта страницы на выходе блока 9 адресации страницы не возникает, и тригпер готовности страницы находится в состоянии логического О. Сигналы управления запоминающим модулем 20 на выходе дешифратора 19

715

импульсов, триггера 7 разрешения поля и счетчика 8 фаз поля не вырабатываются.

При установленных значениях параметров работы формирователя его запуск производится путем записи в регистр 5 режима управляющего слова с единичным битом запроса операции, поступающим на вход разрешения триг- гера 7 разрешения поля (сигнал а, фиг.2). При этом код на втором выходе регистра 5 режима определяет выбранную временную диаграмму работу модуля причем таких может быть запрограм- Нировано несколько с учетом разрядности второго выхода регистра 5 режима. По тактовому сигналу с первого выхода генератора 6 (сигнал б, фиг.2) триггер 7 разрешения поля устанавливается в Лог.1 и своим выходным сигналом разрешает счет счетчика 8 фаз поля (сигнал в, фиг.2). Формирование Поля начинается в определенной фазе (сигналы гид, фиг.2), что обеспе- чивается синхронизацией процессов Изменения состояния триггера 7 разрешения поля с началом и окончанием счета счетчика 8 фаз поля. Выходы счетчика 8 фаз поля и триггеры 7 раз- ешения поля управляют работой драй- еров X и У катушек модуля. В блоке 9 адресации страницы производится Подсчет тактов поля, поступающих на его вход синхронизации с выхода старшего разряда счетчика В фаз поля (сигнал д, фиг.2), и при совпадении записанного номера страницьг.с состоянием его внутреннего счетчика на выходе блока 9 адресации страни15 1 Появляется сигнал начала страницы (сигнал е, фиг.2), устанавливающий Триггер 10 готовности страницы в Лог.1,(сигнал ж, фиг.2).

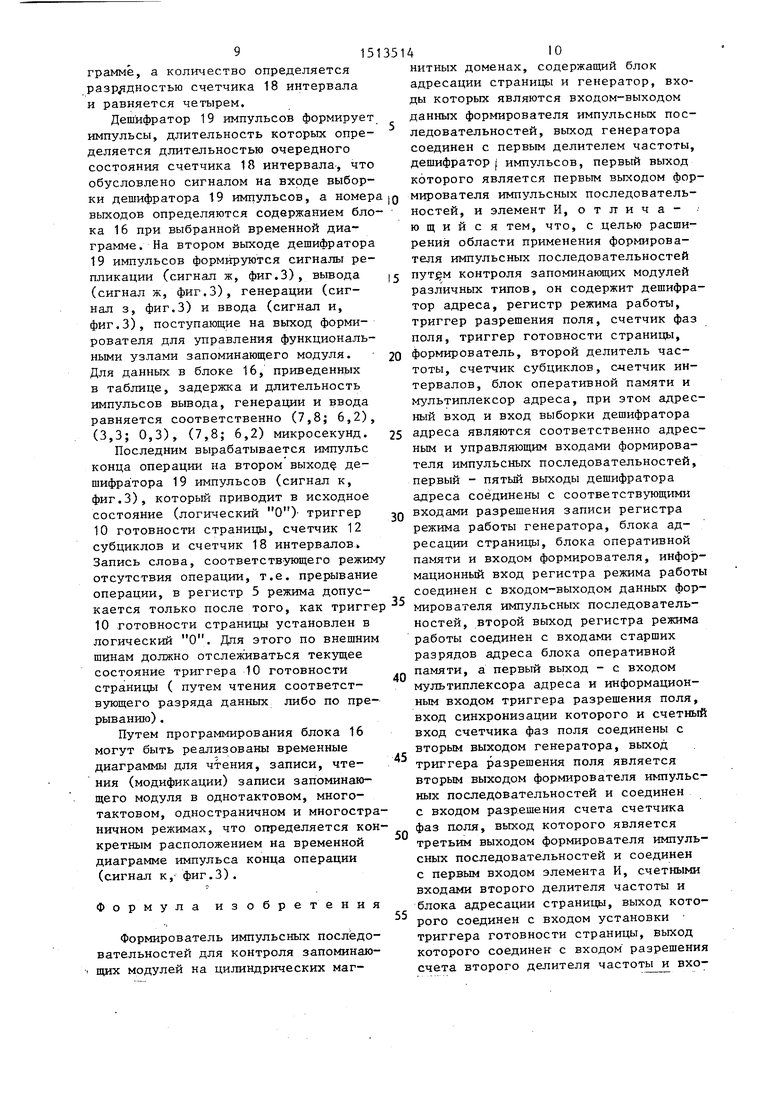

С этого момента начинается формирование сигналов управления запоми- йающим модулем. Конкретная временная диаграмма этих- сигналов зависит от содержания Йлока 16, поэтому в качесве иллюстрации в таблице приведено содержание блока 16 оперативной памяти при частоте поля, равной 100 кГц и тактовой частоте на втором выходе генератора 6, равной ТО МГц (х означает произвольное отличное от нуля значение), соот- ветствующее временной диаграмме работы устройства в одностраничном реям- ме записи модуля типа К1605РЦ1 (фиг.З

0

Q 5 5

5055

0

Для привязки к общей временной диаграмме, работы формирователя сигналы а, б и в (фиг.З) соответствуют сигналам д, е и ж (фиг.2). Сигналом с выхода триггера 10 готовности страницы (сигнал в, фиг.З) разрешается счет делителя 11 частоты, который отсчитывает занесенное в него по сигналу разрешения счета из блока 16 количество тактов поля, после чего дает перенос (сигнал г, фиг.З). Адрес на блок 16 при этом поступает от счётчика 12 субциклов и счетчика 18 интервалов, что обусловлено сменой канала передачи мультиплексора. 15 адресов сигналом с первого выхода регистра 5 режима по сравнению с исход-, ным состоянием. Для первого формируемого субцикла значение младших адресов на входе блока 16 равно О и соответствует исходным состояниям счетчика 12 субциклов и счетчика 18 интервала. По сигналу переноса делителя 11 частоты, счетчик 12 субциклов выдает на адресные входы блока 16 следующий код (сигнал д, фиг.З) и с выхода блока 16 в делитель 11 часто- Т1Ы заносится код, соответствз щий следующему субциклу. Таким образом, формируются субциклы, разграниченные сигналами переноса делителя 11 частоты и имеющие длительность в единицах периода счетчика 8 фаз поля, соатветствующую содержанию блока 16 при выбранной временной диаграмме.

Логическим элементом И 14 вырабатывается сигнал запуска делителя 17 частоты (сигнал е, фиг.З). Запуск делителя 17 частоты производится в начале каждого субцикла, а во втором субцикле на каждый такт поля и привязан к 0-й фазе счетчика 8 фаз поля, что определяется сигналами, поступающими на вход элемента И 14. После запуска делителя 17 частоты последний отсчитывает тактовые сигналы с второго выхода генератора 6 и по достижению числа, равного коду на выходе блока 16, выходным сигналом переключает счетчик 18 интервала. Таким образом, на каждый факт запуска делителя 17 частоты интервалов на выходе счетчика 18 интервалов вырабатываются последовательные состояния, длительность которых в единицах периода тактового сигнала на втором, выходе генератора 6 соответствует содержанию блока 16 при выбранной временной диа915

грамме, а количество определяется разр;1дностью счетчика 18 интервала и равняется четырем.

Дешифратор 19 импульсов формирует импульсы, длительность которых определяется длительностью очередного состояния счетчика 18 интервала-, что обусловлено сигналом на входе выборки дешифратора 19 импульсов, а номер выходов определяются содержанием блока 16 при выбранной временной диаграмме. На втором выходе дешифратора 19 импульсов формируются сигналы репликации (сигнал ж, фиг.З), вывода (сигнал ж, фиг.З), генерации (сигнал 3, фиг.З) и ввода (сигнал и, фиг.З), поступающие на выход формирователя для управления функциональными узлами запоминающего модуля. Для данных в блоке 16, приведеннзых в таблице, задержка и длительность импульсов вывода, генерации и ввода равняется соответственно (7,8; 6,2), (3,3; 0,3), (7,8; 6,2) микросекунд.

Последним вырабатывается импульс конца операции на втором выход де- шифра тора 19 импульсов (сигнал к, фиг.З), который приводит в исходное состояние (логический О)- триггер 10 готовности страницы, счетчик 12 субциклов и счетчик 18 интервалов Запись слова, соответствующего режиму отсутствия операции, т.е. прерывание операции, в регистр 5 режима допускается только после того, как триггер 10 готовности страницы установлен в логический О. Для этого по внешним шинам должно отслеясиваться текущее состояние триггера 10 готовности страницы ( путем чтения соответствующего разряда данных либо по прерыванию) .

Путем программирования блока 16 могут быть реализованы временные диаграммы для чтения, записи, чтения (модификации) записи запоминающего модуля в однотактовом, многотактовом, одностраничном и многостраничном режимах, что определяется конкретным расположением на временной диаграмме импульса конца операции (сигнал к,- фиг.З) .

Формула изобретения

Формирователь импульсных последовательностей для контроля запоминающих модулей на цилиндрических маг0

5

0

5

51410

нитных доменах, содержащий блок адресации страницы и генератор, входы которых являются входом-выходом данных формирователя импульсных последовательностей, выход генератора соединен с первым делителем частоты, дешифратору импульсов, первый выход которого является первым выходом формирователя импульсных последовательностей, и элемент И, отличающий с я тем, что, с целью расширения области применения формирователя импульсных последовательностей контроля запоминающих модулей различных типов, он содержит дешифратор адреса, регистр режима работы, триггер разрешения поля, счетчик фаз поля, триггер готовности страницы, формирователь, второй делитель частоты, счетчик субциклов, с-четчик интервалов, блок оперативной памяти и мультиплексор адреса, при этом адресный вход и вход выборки дешифратора адреса являются соответственно адресным и управляющим входами формирователя импульсных последовательностей, первый - пятый выходы дешифратора адреса соединены с соответствующими входами разрешения записи регистра режима работы генератора, блока адресации страницы, блока оперативной памяти и входом формирователя, информационный вход регистра режима работы соединен с входом-выходом данных формирователя импульсных последовательностей, второй выход регистра режима работы соединен с входами старших разрядов адреса блока оперативной памяти, а первый выход - с входом мультиплексора адреса и информационным входом триггера разрешения поля, вход синхронизации которого и счетный вход счетчика фаз поля соединены с вторым выходом генератора, выход триггера разрешения поля является вторым выходом формирователя ш-тульс- ных последовательностей и соединен с входом разрешения счета счетчика фаз поля, выход которого является третьим выходом формирователя импульсных последовательностей и соединен с первым входом элемента И, счетными входами второго делителя частоты и блока адресации страницы, выход которого соединен с входом установки триггера готовности страницы, выход которого соединен с входом разрешения счета второго делителя частоты и вхо0

5

0

5

0

5

П151

дом формирователя, выход которого соединен с входом-выходом данных формирователя импульсных последовательностей, информационные входы первого и второго делителей частоты подключены к выходу блока оперативной памяти, вход данных которого подключен к вхо.- ду-выходу данных формирователя импульсных последовательностей, выход первого делителя частоты соединен с вторым входом элемента И и счетным входом счетчика субциклов, выход кото рого соединен со старшими разрядами второй группы информационных входов мультиплексора адреса и с третьим входом элемента И, выход которого соединен с входом запуска первого

2 3 О 1

2 3 О 1 2 3 О 1

2 3

делителя частоты, выход которого соединен со счетным входом счетчика интервалов, выход которого соединен с входом разрешения дешифратора им- пульсов и с младшими разрядами второй группы ин формационных входов мультиплексора адреса, первая группа информационных входов которого соединена с адресным входом формирователя импульсных последовательностей, а выход - с входами младших разрядов адреса блока оперативной памяти, второй выход дешифратора импульсов соединен с входами сброса счетчика интервалов, счетчика субциклов и триггера готовности страницы.

вывода

X X

33 3

X X X X X X

78 62

X

X

Код импульса генерации

Код импульса ввода

Код импульса конца операции

JlJгrгллJггuгrlЛJъгъa...глJгпJaлJlл

.

-I

-J -,

г :

L

: :

a -гulJгnJ JiлJTAnлJгrrгшJггlЛJтл

ff

: :

| Устройство для контроля доменной памяти | 1982 |

|

SU1022216A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля блоков доменной памяти | 1982 |

|

SU1020862A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1989-10-07—Публикация

1987-03-09—Подача