Изобретение относится к измерительной технике и предназначено для использования в составе измерительных прибороЕ и систем в качестве преобразователя выходн.ых сигналов тахогенераторов переменного тока в кодЦель изобретения - повышение надежности и расширение функциональных возможностей устройства.

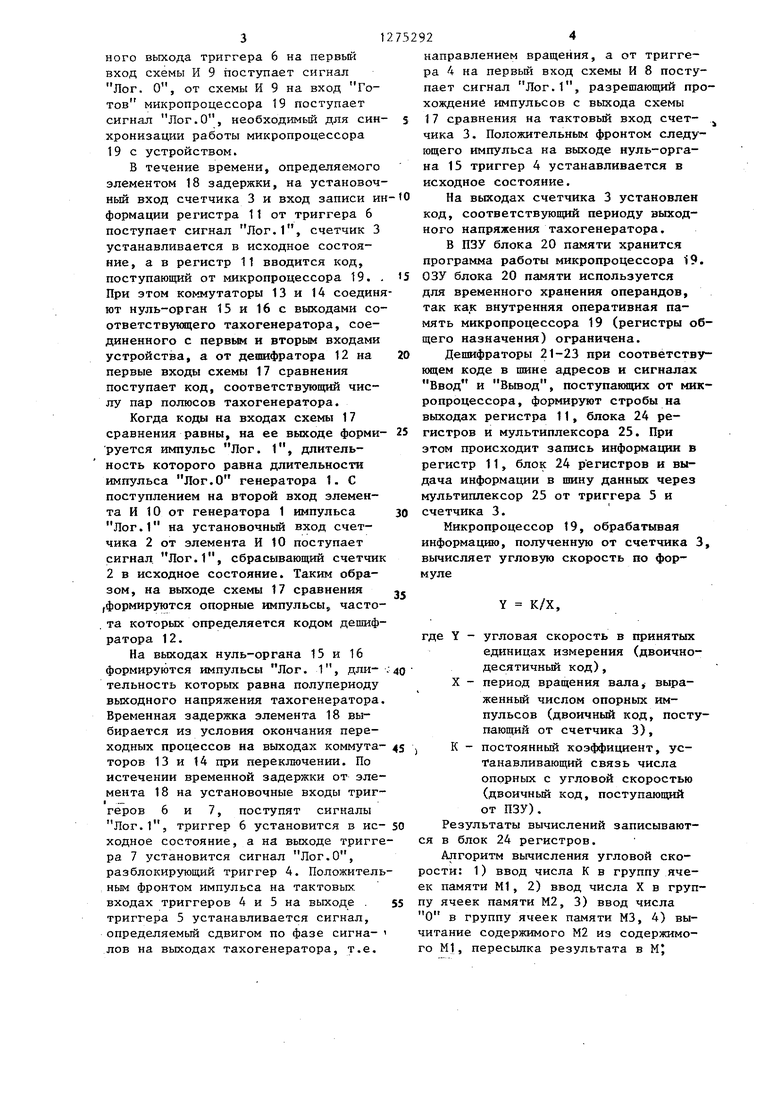

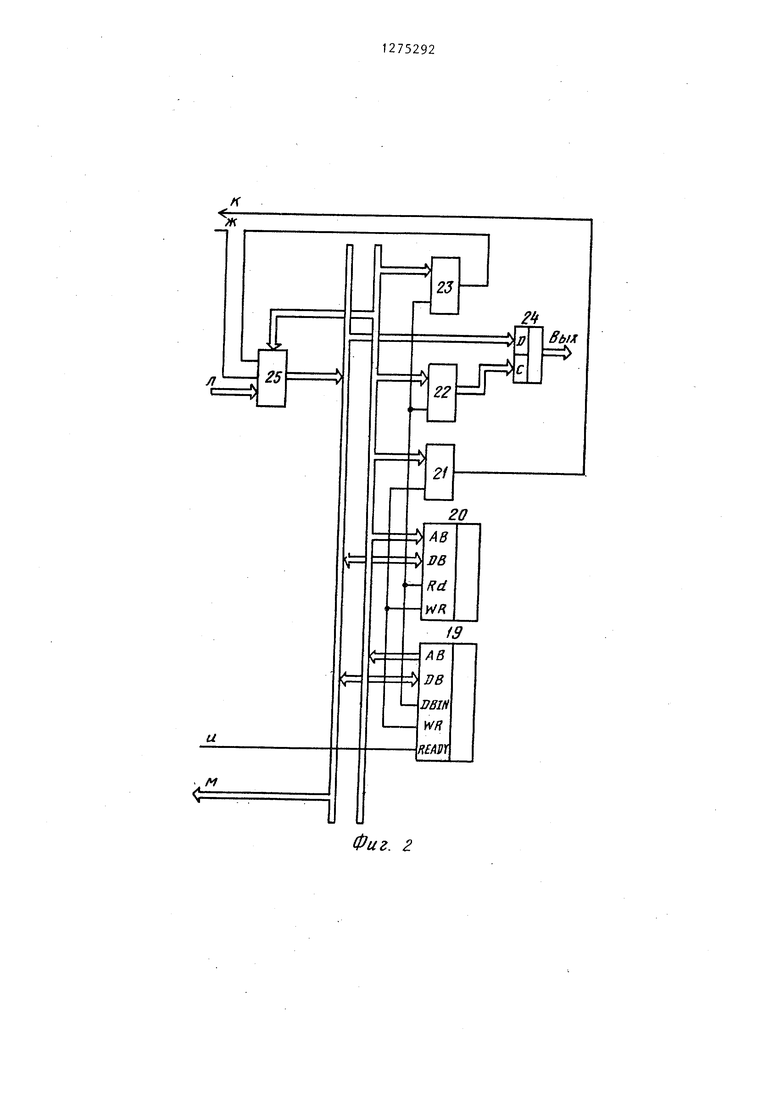

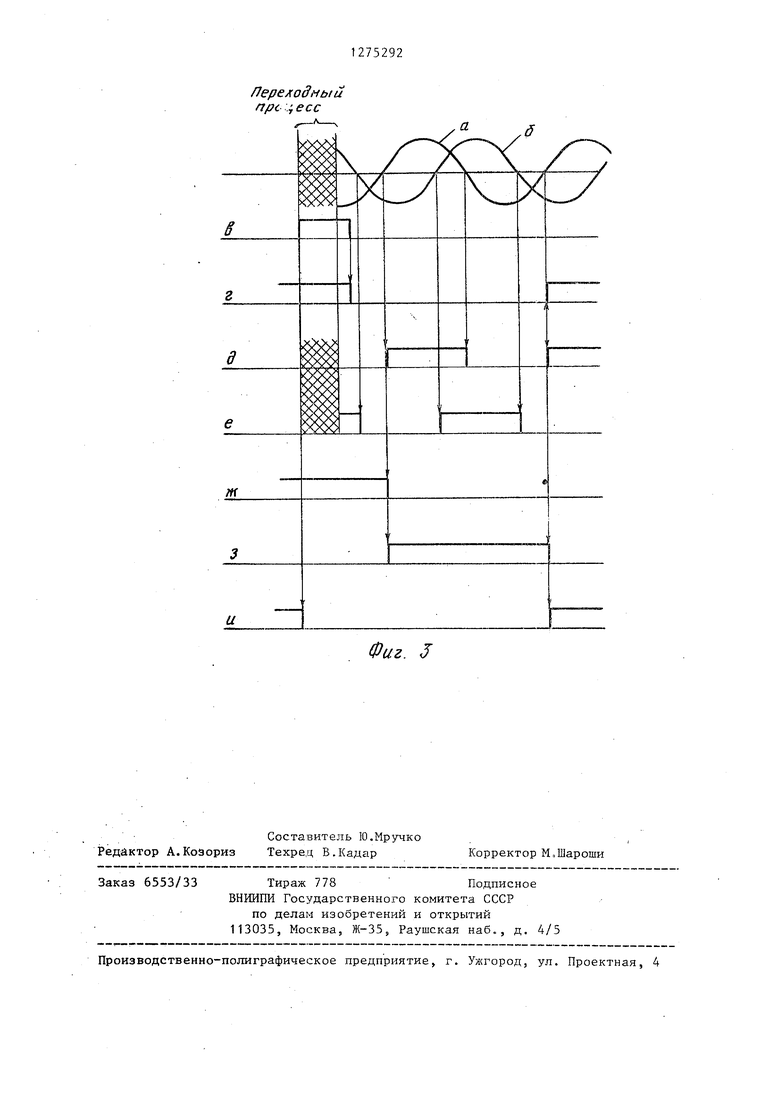

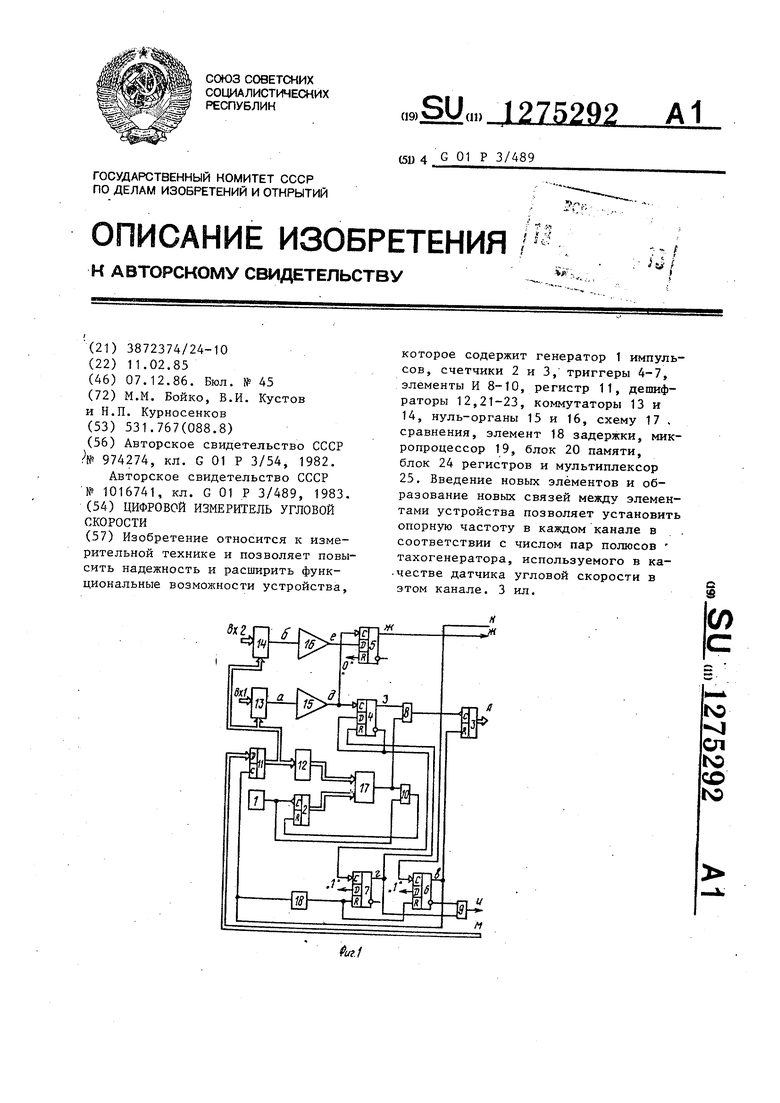

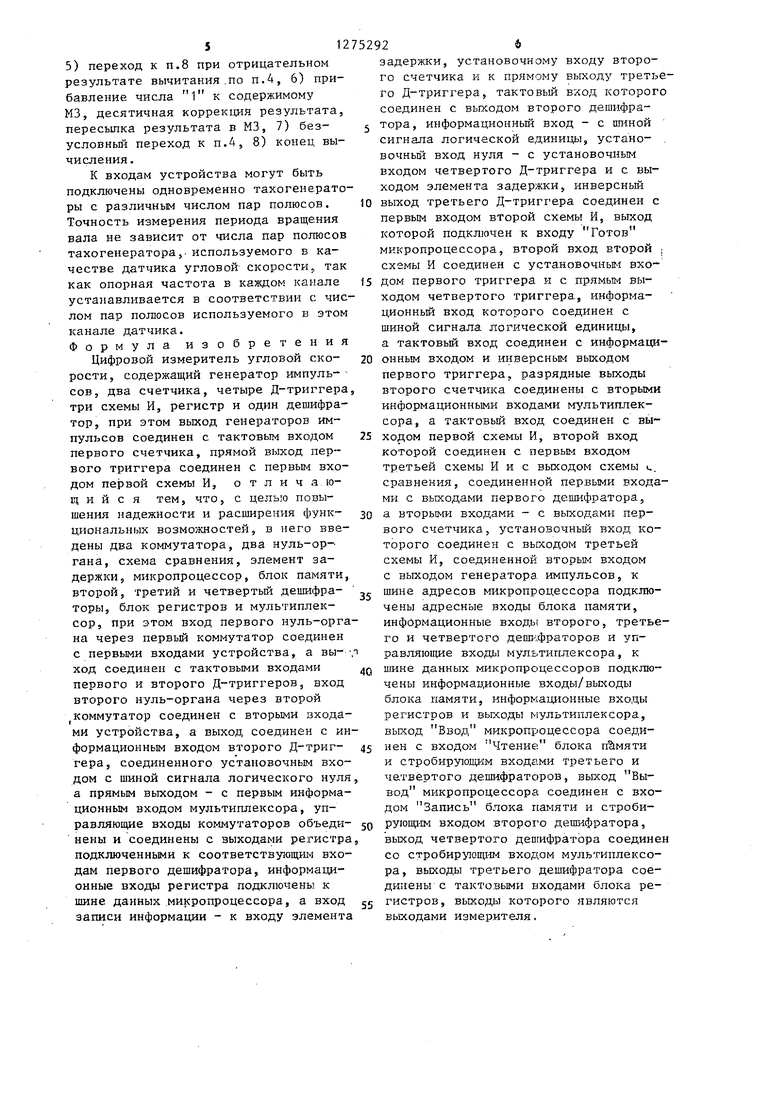

На фиг. 1 и 2 приведены схемы предлагаемого устройства; на фиг, 3времеиная диаграмма его работы.

1ифровой измеритель угловой скорости содержит генератор 1 импульсов, счетчики 2 и 3, триггеры 4-7, элементы И 8-10, регистр 11, дешифратор 12, коммутаторы 13 и 14, нульорганы 15 и 16s схему 17 сравнения, элемент 18 задержки, микропроцессор 19, блок 20 памяти, дешифраторы 2123., блок 24 регистров, мультиплексор 25, при этом генератор импульсов 1 соединен с тактовым входом счетчика 2, прямой выход триггера 4 соединен с первьм входом схемы И 8, вход нуль-органа 15 через .коммутато 13 соединен с первыми входами устройства, а выход - с тактовьми входами триггеров 4 и 5, вход иуль-оргапа 16 через коммутатор 14 соединен с вторыми входами устройства, а выход соединен с информационным входом триггера 5, соединенного устновочным входом с шиной сигнала Лог.О, а прямьп выходом - с информационным входом мультиплексора 25, управляющие входы коммутаторов 13 и 14 соединены с входами дешифратора 12 и подключены к выходам регистра 11, информационные входы которог соединены с юиной данных микропроцессоров, а вход записи информации соединен с входом элемента 18 задерлски, установочным входом счетчика 3 и подключен к прямому выходу триггера 6, тактовый вход которого соединен с выходом дешифратора 21, информационньм вход, соединен с ишно сигнала Лог,1, установочной вход соединен с установочным входом триггера 7 и подключен к выходу элемента 18 задержки, а инверсный выход соединен с первым входом схемы И 9, соединенной выходом с входом Готов .микропроцессора, а вторым входом соединенной с установочным входом триггера 4 и подключенной к выходу

триггера 7, информационный вход которого соединен с 1иной сигнала Лог.1, а тактовьй вход соединен с информационным входом и инверсным выходом триггера 4,, выходы счетчика 3 соединены с вторыми информационными входами мультиплексора 25, а тактовый вход соединен с выходом схемы И 8, второй вход которой соединен с

первым входом схемы И 10 -и подключен к выходу схемы 17 сравнения, соединенной первыми входами с выходами дешифратора 12, а вторыми входами с выходами счетчика 2, установочный

вход которого соединен с выходом схемы И 10, соединенной вторым входом с выходом генератора 1 импульсов., к шине адресов микропроцессора 19 подкл очены адресные входы блока 20

памяти, информационные входы дешифраторов 21-23 и з равляющие входы мультиплексора 25, к шине данных микропроцессора подключены информационные входы/выходы блока 20 памяти, информационные входы блока 24 регистров и выходы мультиплексора 25, выход Ввод микропроцессора соединен с входом Чтение блока 20 памяти и стробирующими входами дешифраторов 22 и 23, выход Вывод микропроцессора 19 соединен с входом Запись блока 20 памяти и стробирующим входом дешифратора 21, выход дешифратора 23 соединен со стробирующим входом мультиплексора, выходы дешифратора 22 соединены с тактовыми входами блока 24 регистров, выходы которого являются выходами устройства.

Устройство работает следующим

образом.

В исходном состоянии на тактовом входе триггера 6 устанавливается сигнал Лог,О. На первый вход схемы И 9 от триггера .6 поступает сигнал

Лог.1, на второй вход схемы И 9 и установочный вход триггера 4 от триггера 7 поступает сигнал Лог.1. На выходе элемента И 9 устанавливается сигнал Лог.1. От триггера 4

на первый вход схемы И 8 поступает сигнал Лог.О, на тактовом входе счетчика 3, связанном с выходом схемы И 8, - сигнал Лог.О.

С поступлением на тактовый вход

триггера 6 от микропроцессора 19 через дешифратор 21 сигнала Лог.1 на прямом выходе триггера 6 устанав- ливается сигнал Лог.1, от инверс3ного выхода триггера 6 на первый вход схемы И 9 поступает сигнал Лог. О, от схемы И 9 на вход Готов микропроцессора 19 поступает сигнал Лог.О, необходимый для син хронизации работы микропроцессора 19 с устройством. В течение времени, определяемого элементом 18 задержки, на установоч ный вход счетчика 3 и вход записи и формации регистра 11 от триггера 6 поступает сигнал Лог.1, счетчик 3 устанавливается в исходное состояние, а в регистр 11 вводится код. поступающий от микропроцессора 19. При этом коммутаторы 13 и 14 соедин ют нуль-орган 15 и 16 с выходами со ответствукицего тахогенератора, соединенного с первым и вторым входами устройства, а от дешифратора 12 на первые входы схемы 17 сравнения поступает код, соответствующий числу пар полюсов тахогенератора. Когда коды на входах схемы 17 сравнения равны, на ее выходе форми руется импульс Лог. 1, длительность которого равна длительности импульса Лог.О генератора 1. С поступлением на второй вход элемента И 10 от генератора 1 импульса Лог. Г на установочный вход счетчика 2 от элемента И 10 поступает сигнал. Лог.1, сбрасывающий счетчи 2 в исходное состояние. Таким образом, на выходе схемы 17 сравнения (формируются опорные импульсы, часто . та которых определяется кодом дешиф ратора 12. На выходах нуль-органа 15 и 16 формируются импульсы Лог. 1, длительность которых равна полупериоду выходного напряжения тахогенератора Временная задержка элемента 18 выбирается из условия окончания переходных процессов на выходах коммута торов 13 и 14 при переключении. По истечении временной задержки от эле мента 18 на установочные входы триг геров 6 и 7, поступят сигналы Лог.1, триггер 6 установится в ис ходное состояние, а на выходе тригг ра 7 установится сигнал Лог.О, разблокирующий триггер 4. Положител ным фронтом импульса на тактовых входах триггеров 4 и 5 на выходе . триггера 5 устанавливается сигнал, определяемый сдвигом по фазе сигналов на выходах тахогенератора, т.е. 2 направлением вращения, а от триггера 4 на первый вход схемы И 8 поступает сигнал Лог.1, разрешающий прохождение импульсов с выхода схемы 17 сравнения на тактовый вход счет- . чика 3. Положительным фронтом следующего импульса на выходе нуль-органа 15 триггер 4 устанавливается в исходное состояние. На выходах счетчика 3 установлен код, соответствующий периоду выходного напряжения тахогенератора. В ПЗУ блока 20 памяти хранится программа работы микропроцессора 19. ОЗУ блока 20 памяти используется для временного хранения операндов, так как внутренняя оперативная память микропроцессора 19 (регистры общего назначения) ограничена. Дешифраторы 21-23 при соответствующем коде в шине адресов и сигналах Ввод и Вьшод, поступакшрсх от микропроцессора, формируют стробы на выходах регистра 11, блока 24 регистров и мультиплексора 25. При этом происходит запись информации в регистр 11, блок 24 регистров и выдача информации в шину данных через мультиплексор 25 от триггера 5 и счетчика 3. Микропроцессор 19, обрабатывая информацию, полученную от счетчика 3, вычисляет угловую скорость по формулеY К/Х, где Y - угловая скорость в принятых единицах измерения (двоичнодесятичный код), X - период вращения вала выраженный числом опорных импульсов (двоичный код, поступающий от счетчика 3), К - постоянный коэффициент, устанавливающий связь числа опорных с угловой скоростью (двоичный код, поступающий от ПЗУ). Результаты вычислений записываютя в блок 24 регистров. Алгоритм вычисления угловой скоости: 1) ввод числа К в группу ячек памяти Ml, 2) ввод числа X в групу ячеек памяти М2, 3) ввод числа О в группу ячеек памяти МЗ, 4) выитание содержимого М2 из содержимоо Ml, пересьшка результата в MJ 5) переход к п.8 при отрицательном результате вычитания.по п.4, 6) прибавление числа 1 к содержимому МЗ, десятичная коррекция результата, пересылка результата в МЗ, 7) безусловньш переход к п.А, 8) конец вычисления. К входам устройства могут быть подключены одновременно тахогенерато ры с различным числом пар полюсов. Точность измерения периода вращения вала не зависит от числа пар погпосов тахогенератора,. используемого в качестве датчика угловой- скорости., так как опорная частота в каждом канале устанавливается в соответствии с чис лом пар полюсов используемого в этом канале датчика. Формула изобретения Цифровой измеритель угловой скорости, содержащий генератор импульсов, два счетчика, четыре Д-триггера три схемы И, регистр и один дешифратор, при этом выход генераторов импульсов соединен с тактовым входом первого счетчика, прямой выход первого триггера соединен с первым входом первой схемы И, о т л и ч а ющ и и с я тем, что, с целью повышения надежности и расширения функциональных возможностей, в него введены два коммутатора, два нуль-ор-гана, схема сравнения, элемент задержки, микропроцессор, блок памяти второй, третий и четвертый дешифраторы, блок регистров и мультиплексор, при этом вход первого нуль-орг на через первьй коммутатор соединен с первыми входами устройства, а вы ход соединен с тактовыми входами первого и второго Д-триггеров, вход второго нуль-органа через второй Iкоммутатор соединен с вторыми входа ми устройства, а выход соединен с ин формационным входом второго Д-триггера, соединенного установочным входом с шиной сигнала логического нуля а прямым выходом - с первым информационным входом мультиплексора, управляющие входы коммутаторов объеди- 50

нены и соединены с выходами регистра, подключенньми к соответствующим входам первого дешифратора, информационные входы регистра подключены к шине данных микропроцессора, а вход gg записи информации - к входу элемента

выход четвертого дешифратора соединен со стробир пощим входом мультиплексора , выходы третьего дешифратора соединены с такто.выми входами блока регистров, выходы которого являются вь5ходами измерителя, задержки, установочному входу второго счетчика и к прямому выходу третьего Д-триггера, тактовый вход которого соединен с выходом второго дешифратора, информационный вход - с шиной сигнала логической единицы, устано- . вочный вход нуля - с установочным входом четвертого Д-триггера и с выходом элемента задержки, инверсный выход третьего Д-триггера соединен с первым входом второй схемы И, выход которой подключен к входу Готов микропроцессора, второй вход второй . схемы И соединен с установочным входом первого триггера и с прямым выходом четвертого триггера, информационньй вход которого соединен с шиной сигнала логической единицы, а тактовьй вход соединен с информационным входом и инверсным выходом первого триггера 5 разрядные выходы второго счетчика соединены с вторыми информационными входами мультиплексора, а тактовьй вход соединен с выходом первой схемы И, второй вход которой соединен с первым входом третьей схемы И и с выходом схемы i.. сравнения, соединенной первыми входами с выходами первого дешифратора, а вторыми входами - с выходами первого счетчика, установочный вход которого соединен с вькодом третьей схемы И, соединенной вторым входом с выходом генератора, импульсов, к шине адресов микропроцессора подключены адресные входы блока памяти, информационные входы второго, третьего и четвертого депксфраторов и управляющие входы мультиплексора, к ишне данных микропроцессоров подключены информационные входы/выходы блока памяти, информационные входы регистров и выходы мультиплексора, выход Ввод г 1икропроцессора соединен с входом Чтение блока Пс1мяти и стробирующим входами третьего и четвёртого дешифраторов, выход Вывод микропроцессора соединен с входом Запись блока памяти и стробиРУопц входом второго дешифратора.

Фиг. г

Переходный прс .есс

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь последовательного кода в параллельный | 1984 |

|

SU1193655A1 |

| Устройство для формирования импульсов | 1987 |

|

SU1497724A1 |

| Устройство для формирования импульсов | 1985 |

|

SU1292168A1 |

| Устройство для контроля знаний обучаемых | 1987 |

|

SU1524082A1 |

| Устройство для входного контроля изделий | 1990 |

|

SU1746388A2 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1425683A1 |

| Устройство для контроля многоканальных импульсных последовательностей | 1989 |

|

SU1732332A1 |

| Программируемый контроллер | 1985 |

|

SU1509887A2 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Генератор псевдослучайной последовательности импульсов | 1985 |

|

SU1277362A1 |

Изобретение относится к измерительной технике и позволяет повысить надежность и расширить функциональные возможности устройства, которое содержит генератор 1 импульсов, счетчики 2 и 3, триггеры 4-7, элементы И 8-10, регистр 11, дешифраторы 12,21-23, коммутаторы 13 и 14, нуль-органы 15 и 16, схему 17 . сравнения, элемент 18 задержки, микропроцессор 19, блок 20 памяти, блок 24 регистров и мультиплексор 25. Введение новых элементов и образование новьш связей между элементами устройства позволяет установить опорную частоту в каждом канале в . . соответствии с числом пар полюсов тахогенератора, используемого в качестве датчика угловой скорости в этом канале. 3 ил. (Л ND 01 ЬО СО

Фиг. J

| Устройство для измерения скорости вращения | 1981 |

|

SU974274A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровой измеритель угловой скорости | 1982 |

|

SU1016741A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-12-07—Публикация

1985-02-11—Подача