Изобретение относится к ртмпульс- Еюй технике и предназначено для формирования сигналов управления программатором инетегральных сх-ем.

Цель изобретения - расширение функциональных возможностей устройства путем оптимизации времени программирования и обеспечения выдержки времени для охлаждения программируемой ИМС.

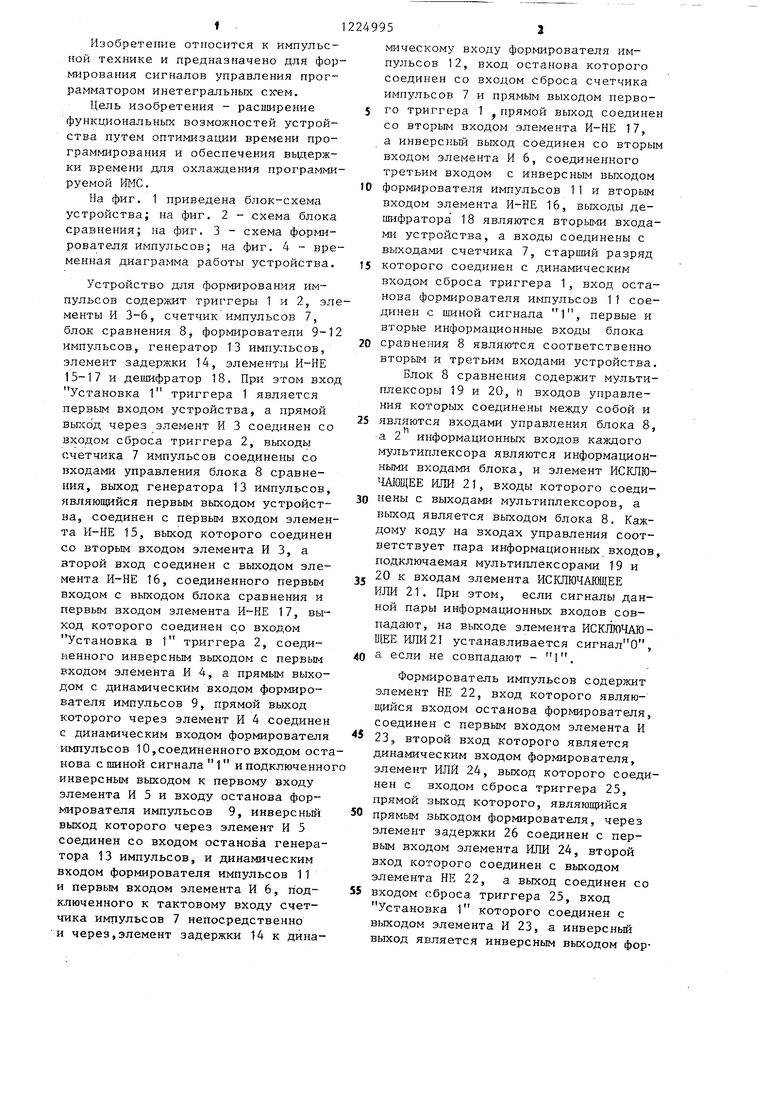

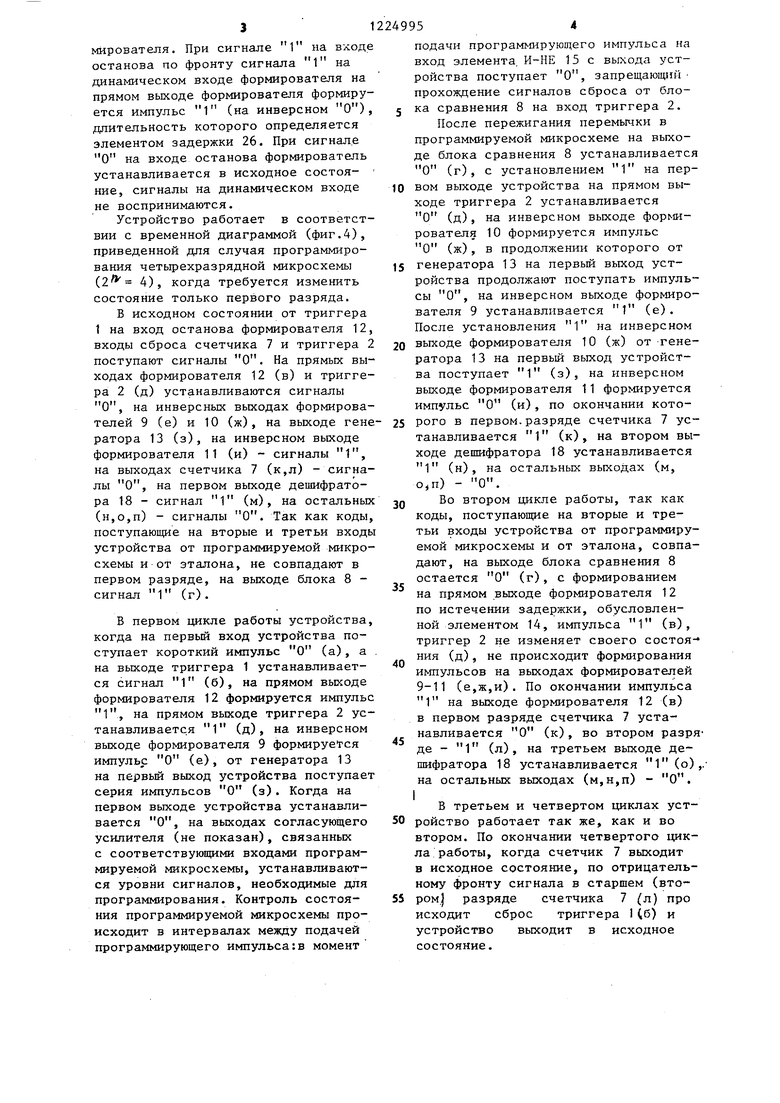

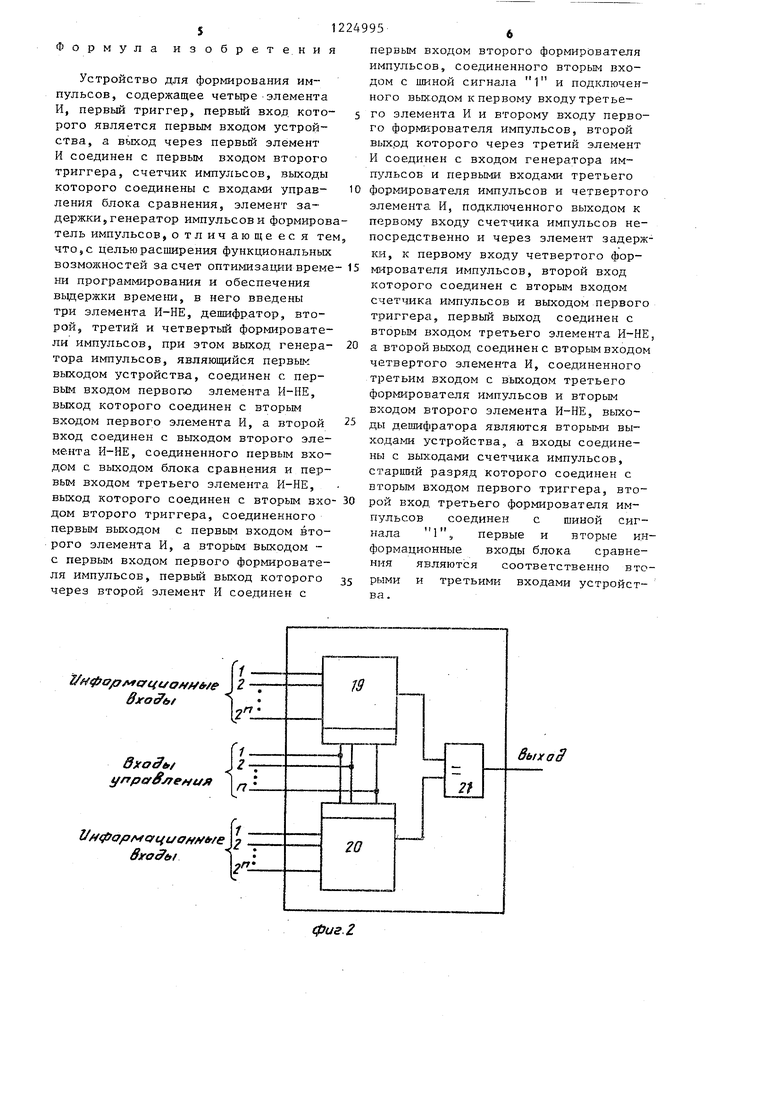

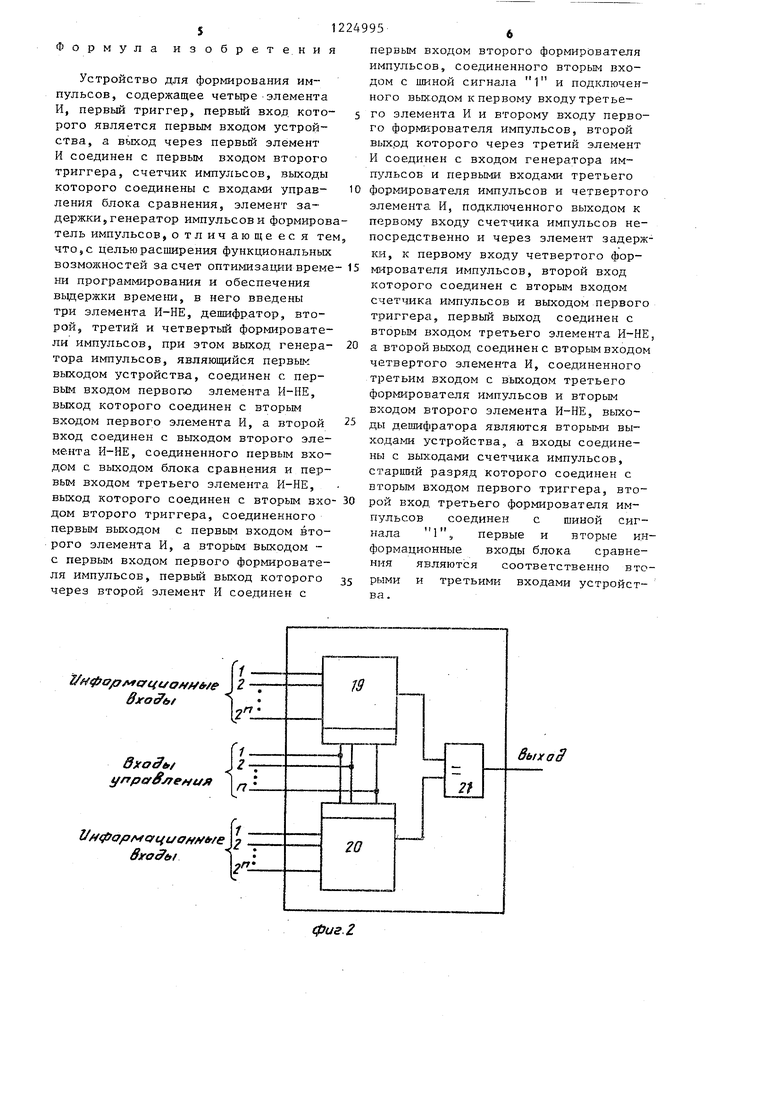

На фиг. 1 приведена блок-схема устройства; на фиг, 2 - схема блока сравнения; на фиг. 3 - схема формирователя импульсов; на фиг. 4 временная диаграмма работы устройства.

Устройство для формирования импульсов содержит триггеры 1 и 2, элементы И 3-6, счетчик импульсов 7, блок сравнения 8, формирователи 9-12 импульсов, генератор 13 импульсов, элемент задержки 14, элементы И-НЕ 15-17 и дешифратор 18. При этом вход Установка 1 триггера 1 является первым входом устройства, а прямой вькод через элемент И 3 соединен со входом сброса триггера 2, вькоды счетчика 7 импульсов соединены со входами управления блока 8 сравнения, выход генератора 13 импульсов, являющийся первым выходом устройства, соединен с первым входом элемента И-НЕ 15, выход которого соединен со вторым входом элемента И 3, а второй вход соединен с выходом элемента И-НЕ 16, соединенного первым входом с выходом блока сравнения и первым входом элемента И-НЕ 17, выход которого соединен со входом Установка в 1 триггера 2, соединенного инверсным выходом с первым входом элемента И 4, а прямым выходом с динамическим входом формирователя импульсов 9, прямой выход которого через элемент И 4 соединен с динамическим входом формирователя импульсов 10,соединенного входом останова с шиной сигнала и подключенного инверсным выходом к первому входу элемента И 5 и входу останова формирователя импульсов 9, инверсньй выход которого через элемент И 5 соединен со входом останова генератора 13 импульсов, и динамическим входом формирователя импульсов 11 и первым входом элемента И 6, подключенного к тактовому входу счетчика импульсов 7 непосредственно И через,элемент задержки 14 к дина12249952

мическому входу формирователя импульсов 12, вход останова которого соединен со входом сброса счетчика импульсов 7 и прямым выходом перво30

5 го триггера 1 прямой выход соединен со вторым входом элемента И-НЕ 17, а инверсный выход соединен со вторым входом элемента И 6, соединенного третьим входом с инверсным выходом

10 формирователя импульсов 11 и вторым входом элемента И-НЕ 16, выходы дешифратора 18 являются вторыми входами устройства, а входы соединены с выхода.ми счетчика 7, старший разряд

tS которого соединен с динамическим

входом сброса триггера 1 , вход, останова формирователя импульсов 11 соединен с шиной сигнала 1, первые и вторые информационные входы блока

20 сравнения 8 являются соответственно вторым и третьим входами устройства. Блок 8 сравнения содержит мультиплексоры 19 и 20, (1 входов управления которых соединены между собой и

25 являются входами управления блока 8, а 2 информационных входов каждого мультиплексора являются информационными входами блока, и элемент ИСКПЮ- 1АЮЩЕЕ ИЛИ 21, входы которого соединены с выходами мультиплексоров, а выход является выходом блока 8. Каждому коду на входах управления соответствует пара информационных входов подключаемая мультиплексорами 19 и 20 к входам элемента ИСЮТЮЧАЮЩЕЕ ИЛИ 21. При этом, если сигналы данной пары информационных входов совпадают, на выходе элемента ИСКЛЮЧАЮЩЕЕ Ш1И21 устанавливается сигнал 0, а если не совпадают - I.

Формирователь импульсов содержит элемент НЕ 22, вход которого являющийся входом останова формирователя, соединен с первым входом элемента И 23, второй вход которого является динамическим входом формирователя, элемент ИЛИ 24, выход которого соеди нен с входом сброса триггера 25, прямой выход которого, являющийся прямым выходом формирователя, через элемент задержки 26 соединен с первым входом элемента ИЛИ 24, второй вход которого соединен с выходом элемента НЕ 22, а выход соединен со 55 входом сброса триггера 25, вход Установка Г которого соединен с выходом элемента И 23, а инверсный выход является инверсным выходом фор

35

40

45

50

го триггера 1 прямой выход соединен со вторым входом элемента И-НЕ 17, а инверсный выход соединен со вторым входом элемента И 6, соединенного третьим входом с инверсным выходом

формирователя импульсов 11 и вторым входом элемента И-НЕ 16, выходы дешифратора 18 являются вторыми входами устройства, а входы соединены с выхода.ми счетчика 7, старший разряд

которого соединен с динамическим

входом сброса триггера 1 , вход, останова формирователя импульсов 11 соединен с шиной сигнала 1, первые и вторые информационные входы блока

сравнения 8 являются соответственно вторым и третьим входами устройства. Блок 8 сравнения содержит мультиплексоры 19 и 20, (1 входов управления которых соединены между собой и

являются входами управления блока 8, а 2 информационных входов каждого мультиплексора являются информационными входами блока, и элемент ИСКПЮ- 1АЮЩЕЕ ИЛИ 21, входы которого соединены с выходами мультиплексоров, а выход является выходом блока 8. Каждому коду на входах управления соответствует пара информационных входов, подключаемая мультиплексорами 19 и 20 к входам элемента ИСЮТЮЧАЮЩЕЕ ИЛИ 21. При этом, если сигналы данной пары информационных входов совпадают, на выходе элемента ИСКЛЮЧАЮЩЕЕ Ш1И21 устанавливается сигнал 0, а если не совпадают - I.

Формирователь импульсов содержит элемент НЕ 22, вход которого являющийся входом останова формирователя, соединен с первым входом элемента И 23, второй вход которого является динамическим входом формирователя, элемент ИЛИ 24, выход которого соединен с входом сброса триггера 25, прямой выход которого, являющийся прямым выходом формирователя, через элемент задержки 26 соединен с первым входом элемента ИЛИ 24, второй вход которого соединен с выходом элемента НЕ 22, а выход соединен со входом сброса триггера 25, вход Установка Г которого соединен с выходом элемента И 23, а инверсный выход является инверсным выходом фор

3

мирователя. При сигнале 1 на вход останова по фронту сигнала 1 на динамическом входе формирователя на прямом выходе формирователя формируется импульс 1 (на инверсном О) длительность которого определяется элементом задержки 26, При сигнале О на входе останова формирователь устанавливается в исходное состоя- ние, сигналы на динамическом входе не воспринимаются.

Устройство работает в соответствии с временной диаграммой (фиг.4), приведенной для случая программирования четьфехразрядной микросхемы ( 4), когда требуется изменить состояние только первого разряда.

В исходном состоянии от триггера 1 на вход останова формирователя 12 входы сброса счетчика 7 и триггера поступают сигналы О. На прямых выходах формирователя 12 (в) и триггера 2 (д) устанавливаются сигналы О, на инверсных выходах формирователей 9 (е) и 10 (ж), на выходе ген ратора 13 (з), на инверсном выходе формирователя 11 (и) - сигналы 1, на выходах счетчика 7 (к,л) - сигналы О, на первом выходе дешифратора 18 - сигнал 1 (м), на остальны (н,о,п) - сигналы О. Так как коды поступающие на вторые и третьи вход устройства от программируемой микро

первом разряде, на выходе блока 8 - сигнал 1 (г).

В первом цикле работы устройства, когда на первый вход устройства поступает короткий импульс О (а), а на выходе триггера 1 устанавливается сигнал 1 (б), на прямом выходе формирователя 12 формируется импульс 1, на прямом выходе триггера 2 ус- танавливаетс.я 1 (д), на инверсном выходе формирователя 9 формируе гся импульс О (е), от генератора 13 на первьй выход устройства поступает серия импульсов О (з). Когда на первом выходе устройства устанавливается О, на выходах согласующего усилителя (не показан), связанных с соответствующими входами программируемой микросхемы, устанавливаются уровни сигналов, необходимые для программирования. Контроль состояния программируемой микросхемы происходит в интервалах между подачей программирующего импульса:в момент

5

is

20 25

30

5

0

5

0

5

подачи пpoгpaм fflpyющeгo импульса на вход элемента. И-НЕ 15 с выхода устройства поступает О, запрещающп прохождение сигналов сброса от блока сравнения 8 на вход триггера 2.

После пережигания перемычки в программируемой микросхеме на выходе блока сравнения 8 устанавливается О (г), с установлением 1 на первом выходе устройства на прямом выходе триггера 2 устанавливается О (д), на инверсном выходе формирователя 10 формируется импульс О (ж), в продолжении которого от генератора 13 на первьй выход устройства продолжают поступать импульсы О, на инверсном выходе формирователя 9 устанавливается 1 (е). После установления 1 на инверсном выходе формирователя 10 (ж) от генератора 13 на первый выход устройства поступает 1 (з), на инверсном выходе формирователя 11 формируется импульс О (и), по окончании которого в первом.разряде счетчика 7 устанавливается 1 (к), на втором выходе дешифратора 18 устанавливается 1 (н), на остальных выходах (м, о,п) - О.

Во втором цикле работы, так как коды, поступающие на вторые и третьи входы устройства от программируемой микросхемы и от эталона, совпадают, на выходе блока сравнения 8 остается О (г), с формированием на прямом выходе формирователя 12 по истечении задержки, обусловленной элементом 14, импульса 1 (в), триггер 2 не изменяет своего состоя- ния (д), не происходит формирования импульсов на выходах формирователей 911 (е,ж,и). По окончании импульса 1 на выходе формирователя 12 (в) в первом разряде счетчика 7 устанавливается О (к), во втором разряде - 1 (л), на третьем выходе де- пшфратора 18 устанавливается 1(о),.- на остальных выходах (м,н,п) - О.

В третьем и четвертом циклах устройство работает так же, как и во втором. По окончании четвертого цикла работы, когда счетчик 7 выходит в исходное состояние, по отрицательному фронту сигнала в старшем (втором) разряде счетчика 7 (л) про исходит сброс триггера 1(б) и устройство выходит в исходное состояние.

I

Формула изобретения

Устройство для формирования импульсов, содержащее четыре элемента И, первый триггер, первьй вход которого является первым входом устройства, а выход через первый элемент И соединен с первым входом второго триггера, счетчик импульсов, выходы которого соединены с входами управления блока сравнения, элемент задержки,, генератор импульсов и формировтель импульсов, отличающееся те что 9 с целью расширения функциональных возможностей за счет оптимизации време ни программирования и обеспечения выдержки времени, в него введены три элемента И-НЕ, дешифратор, второй, третий и четвертьй формирователи импульсов, при этом выход генератора импульсов, являющийся первым выходом устройства, соединен с первым входом первогю элемента И-НЕ, выход которого соединен с вторым входом первого элемента И, а второй вход соединен с выходом второго элемента И-НЕ, соединенного первым входом с выходом блока сравнения и первым входом третьего элемента И-НЕ, выход которого соединен с вторым вхо дом второго триггера, соединенного первым выходом с первым входом второго элемента И, а вторым выходом - с первым входом первого формирователя импульсов, первьм выход которого через второй элемент И соединен с

/

2/f 00/yMty t/Offf /€ J 2 т djfod t,/I

z tJL

Bieoffi /1 - -

улрсе /гения | J

форм«уцио/ / 1гге 2

dirofft,,

-iфиг. 2

5

первым входом второго формирователя импульсов, соединенного вторым входом с шиной сигнала 1 и подключенного ВЫХ.ОДОМ к первому входу третье5 го элемента И и второму входу первого формирователя импульсов, второй вьгхрд которого через третий элемент И соединен с входом генератора импульсов и первыми входами третьего

0 формирователя импульсов и четвертого элемента И, подключенного выходом к первому входу счетчика импульсов непосредственно и через элемент задержки, к первому входу четвертого формирователя импульсов, второй вход которого соединен с вторым входом счетчика импульсов и выходом первого триггера, первый выход соединен с вторым входом третьего элемента И-НЕ, а второй выход соединен с вторым входом четвертого элемента И, соединенного третьим входом с выходом третьего формирователя импульсов и вторым входом второго элемента И-НЕ, выходы дешифратора являются вторыми выходами устройства, а входы соединены с выходами счетчика импульсов, старший разряд которого соединен с вторым входом первого триггера, второй вход третьего формирователя импульсов соединен с шиной сигнала 1, первые и вторые информационные входы блока сравнения являются соответственно вторыми и третьими входами устройства.

0

5

выход

2

20

й -If

a3i

в

/r

3

и

H

J7 M.

/ ff /7

Составитель Г.Брынский

Редактор И.Сегляник Техред о.Сопке

Заказ 1964/58 Тираж 816Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

фиг.Ъ

n n

JUL

фиг.4

Корректор С.Черни

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования импульсов | 1985 |

|

SU1292168A1 |

| Устройство для формирования импульсов | 1987 |

|

SU1497724A1 |

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

| Логический анализатор | 1989 |

|

SU1730627A1 |

| Многоканальная система измерения и регистрации | 1988 |

|

SU1707546A1 |

| Цифровой измеритель угловой скорости | 1985 |

|

SU1275292A1 |

| Устройство для программного управления | 1983 |

|

SU1160367A1 |

| Устройство для контроля и идентификации пользователя | 1991 |

|

SU1833902A1 |

| Устройство для отладки микроЭВМ | 1989 |

|

SU1677708A1 |

| Устройство для кусочно-линейной аппроксимации | 1990 |

|

SU1837272A1 |

Изобретение предназначено для формирования сигналов управления , программатором интегральных схем. Цель изобретения - расширение функ- циональньк возможностей. Устройство содержит триггеры 1 и 2, элементы И 3-6, счетчик импульсов 7, блок 8 сравнения, формирователи 9-12 импульсов, генератор 13 импульсов, элемент 14 задержки, элементы И-НЕ 15,16 и 17 и дешифратор 18. Введение в устройство трех элементов И-НЕ, де1р1ф- ратора, формирователей 10, 11 и 12 импульсов и образование новых связей между элементами устройства позволило оптимизировать время программирования и обеспечить вьщержку времени для охлаждения программируемой ин - тегральной схемы. В описании приведены схемы блока сравнения, формирователя импульсов и временная диаграм- с ма работы устройства. 4 ил. S (Л /2 0 бннА( ND |rs9 4; О :о ел

| Формирователь импульсов | 1980 |

|

SU928624A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для формирования импульсов | 1982 |

|

SU1064443A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-04-15—Публикация

1984-07-06—Подача