38 В.П.Максимов

i.8)

1

(21)i 35CI95 /2 j-09

(22)28.12.87

(() 15.10.89. Бюл. К (72) В.Л.Знаковский, и В.Я.Левантовский (53) 621.373. (Qi

(36)Авторское свидетельство СССР

S 12938 41, кл. И 03 L 7/18 ,09.10.8i.

Заявка Великобритании t 2026268, кл. Н 3 А, 30.01.80.

( ЗМ ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТЫ

(37)Изобретение относится к радиотехнике. Цель изобретения - повышение спектральной чистоты выходных колебаний. Устройство содержит управляемый генератор 1, делитель 2 частоты с переменным коэф. деления, импульсно-фа- зовый детектор 3, фильтр k нижних частот, опорный генератор 3, накопители 6,7 элемент 8 задержки, сумматор Э кодов, преобразователь 10 длительности импульса в напряжение, ЦАП 11, элемент 12 дифференцирования. В устр-во введен блок 13 задания начальных кодов. При включении или переключении частоты блок 13 в соответствии с поступающим на его первый вход значением кода дробной части коэф. деления М формирует код начальных состояний накопителей 6, 7 и в течение одного периода тактовой частоты выдает сформированные коды на выходы. Критерием выбора значения начальных состояний является достижение минимума дисперсий отклонения мгновенных значений фазы от линейно изменяющегося среднего, поскольку линейный закон изменения фаз обуславливает отсутствие помех в выходном сигнале. 2 ил.

с

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фазовый детектор | 1980 |

|

SU892654A1 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| Цифровой фазовый детектор | 1982 |

|

SU1064421A1 |

| Способ цифрового фазового детектирования импульсных последовательностей на неравных частотах и устройство для его осуществления | 1979 |

|

SU879738A1 |

| Синтезатор частот | 1986 |

|

SU1394434A1 |

| Цифровой синтезатор частот | 1986 |

|

SU1483632A1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 2008 |

|

RU2379830C1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ДРОБНЫМ ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 1992 |

|

RU2041563C1 |

| Цифровой фазовый детектор | 1980 |

|

SU898588A1 |

| Синтезатор частот | 1988 |

|

SU1656680A1 |

Изобретение относится к радиотехнике. Цель изобретения - повышение спектральной чистоты выходных колебаний. Устройство содержит управляемый генератор 1, делитель 2 частоты с переменным коэффициентом деления, импульсно-фазовый детектор 3, фильтр 4 нижних частот, опорный генератор 5, накопители 6, 7, элемент 8 задержки, сумматор 9 кодов, преобразователь 10 длительности импульса в напряжение, ЦАП 11, элемент 12 дифференцирования. В устройство введен блок 13 задания начальных кодов. При включении или переключении частоты блок 13 в соответствии с поступающим на его первый вход значением кода дробной части коэффициент деления М формирует код начальных состояний накопителей 6, 7 и в течение одного периода тактовой частоты выдает сформированные коды на выходы. Критерием выбора значения начальных состояний является достижение минимума дисперсий, отклонения мгновенных значений фазы от линейно изменяющегося среднего, поскольку линейный закон изменения фаз обуславливает отсутствие помех в выходном сигнале. 2 ил.

л М

IffffX.

ел

ел

со

СГ)

4

сригА

Изобретение относится к радиотехнике и может быть использовано в радиотехнических устройствах различного назначения, в том числе в качестве гетеродина радиоприемных устройств.

Целью изобретения является повышение спектральной чистоты выходных колебаний .

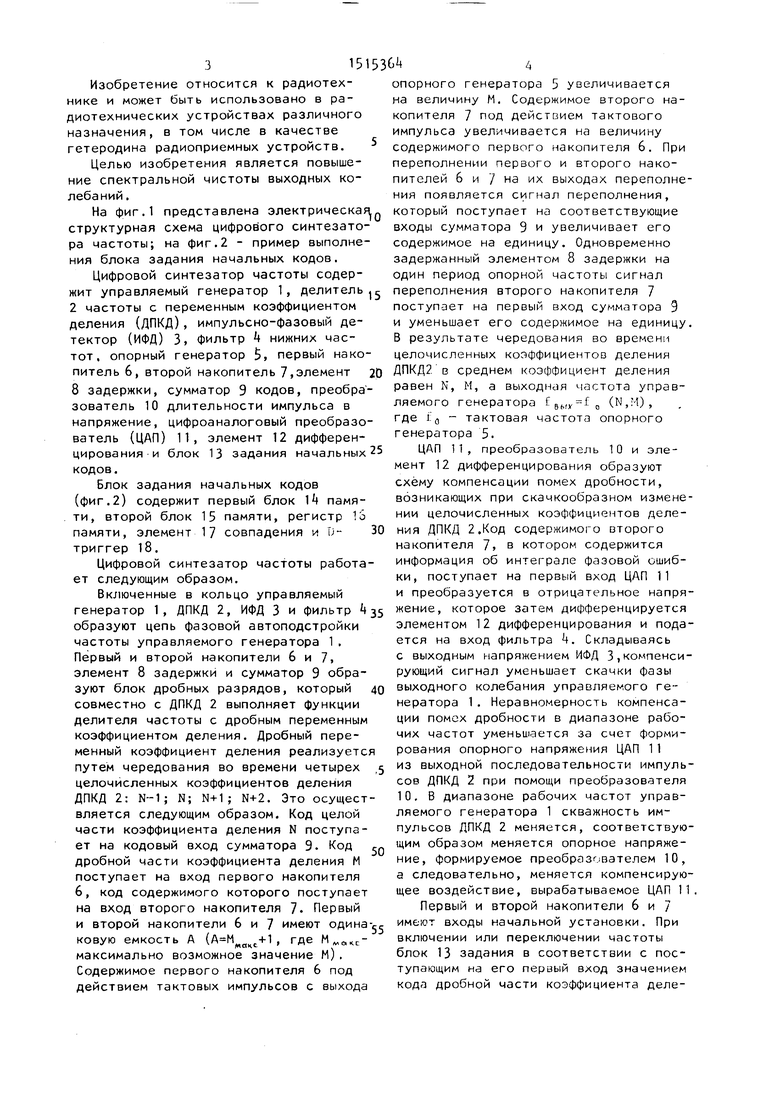

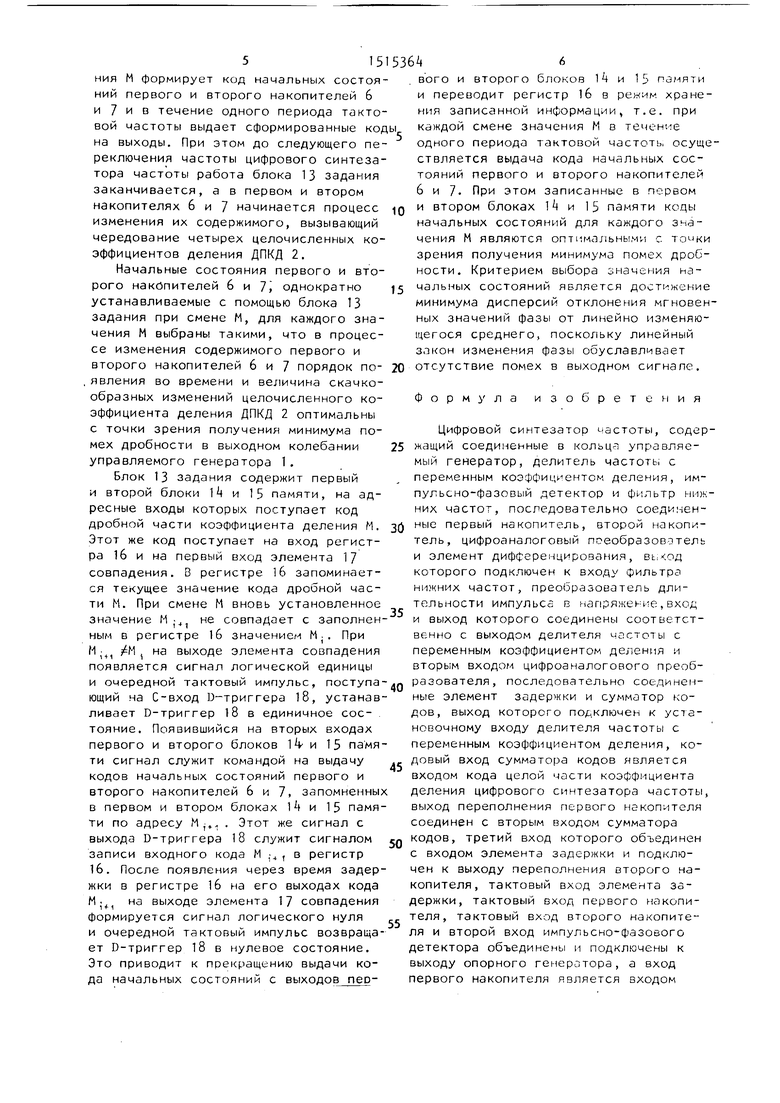

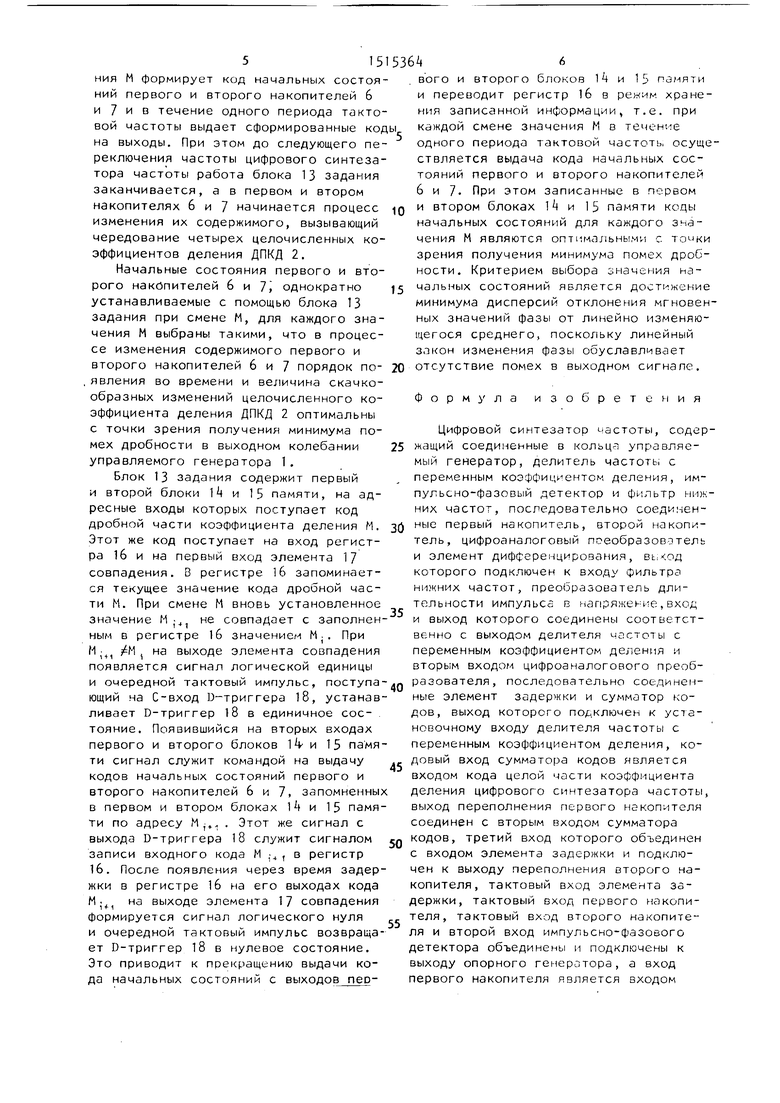

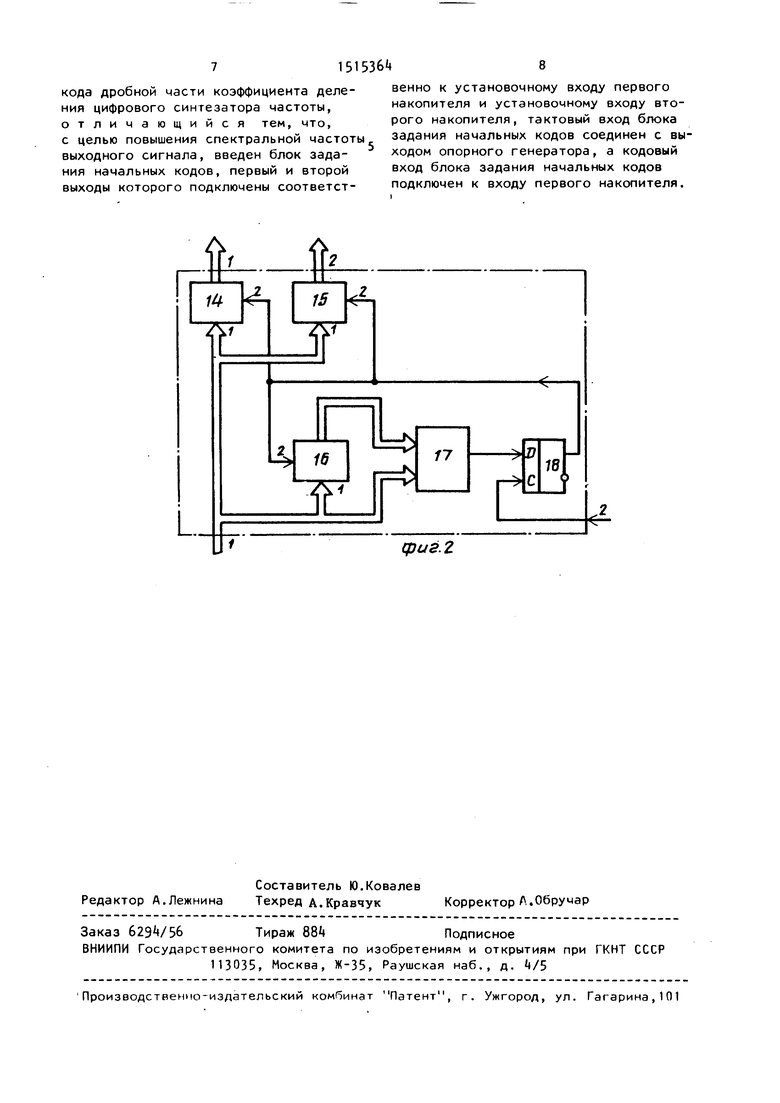

На фиг.1 представлена электрическа структурная схема цифрового синтезато ра частоты; на фиг.2 - пример выполнения блока задания начальных кодов.

Цифровой синтезатор частоты содер

жит управляемый генератор 1, делитель г переполнения второго накопителя 7 2 частоты с переменным коэффициентом деления (ДПКД), импульсно-фазовый детектор (ИФД) 3, фильтр k нижних частот, опорный генератор , первый накопитель 6, второй накопитель 7,элемент 20 8 задержки, сумматор 9 кодов, преобразователь 10 длительности импульса в напряжение, цифроаналоговый преобразователь (ЦАП) 11, элемент 12 дифференцирования и блок 13 задания начальных 25 кодов.

Блок задания начальных кодов (фиг.2) содержит первый блок 1 памяпоступает на первый вход сумматор и уменьшает его содержимое на еди В результате чередования во време целочисленных коэффициентов делен ДПКД2. в среднем коэффициент делен равен N, М, а выходная частота уп ляемого генератора СВ(,,У (N,M), где IQ тактовая частота опорног генератора 5.

ЦАП 11, преобразователь 10 и э мент 12 дифференцирования образую схему компенсации помех дробности возникающих при скачкообразном из нии целочисленных коэффициентов д ния ДПКД 2.Код содержимого второг накопителя 7, в котором содержитс информация об интеграле фазовой о ки, поступает на первый вход ЦАП и преобразуется в отрицательное н жение, которое затем дифференциру элементом 12 дифференцирования и ется на вход фильтра k. Складывая с выходным напряжением ИФД 3,компе рующий сигнал уменьшает скачки фа выходного колебания управляемого нератора 1. Неравномерность компе ции помех дробности в диапазоне р чих частот уменьшается за счет фо рования опорного напряжения ЦАП 1 из выходной последовательности им сов ДПКД 2 при помощи преобразова 10, В диапазоне рабочих частот уп ляемого генератора 1 скважность и пульсов ДПКД 2 меняется, соответс щим образом меняется опорное напр ние, формируемое преобразователем а следовательно, меняется компенс щее воздействие, вырабатываемое Ц

ти, второй блок 15 памяти, регистр 1о памяти, элемент 17 совпадения и D- 30 триггер 18.

Цифровой синтезатор частоты работает следующим образом.

Включенные в кольцо управляемый генератор 1, ДПКД 2, ИФД 3 и фильтр 35 образуют цепь фазовой автоподстройки частоты управляемого генератора 1, Первый и второй накопители 6 и 7, элемент 8 задержки и сумматор 9 образуют блок дробных разрядов, который 40 совместно с ДПКД 2 выполняет функции делителя частоты с дробным переменным коэффициентом деления. Дробный переменный коэффициент деления реализуется путем чередования во времени четырех ,5 целочисленных коэффициентов деления ДПКД 2: N-1; N; N+1; N+2. Это осуществляется следующим образом. Код целой части коэффициента деления N поступает на кодовый вход сумматора 9. Код дробной части коэффициента деления М поступает на вход первого накопителя 6, код содержимого которого поступает на вход второго накопителя 7. Первый и второй накопители 6 и 7 имеют одина-.

50

ковую емкость А ( , где М, максимально возможное значение М). Содержимое первого накопителя 6 под действием тактовых импульсов с выхода

55

который поступает входы сумматора 9

опорного генератора 5 увеличивается на величину М. Содержимое второго накопителя 7 под действием тактового импульса увеличивается на величину содержимого neptjoro накопителя 6. При переполнении первого и второго накопителей 6 и 7 на их выходах переполнения появляется сигнал переполнения,

на соответствующие и увеличивает его

содержимое на единицу. Одновременно задержанный элементом 8 задержки на один период опорной частоты сигнал

переполнения второго накопителя 7

поступает на первый вход сумматора 9 и уменьшает его содержимое на единицу. В результате чередования во времени целочисленных коэффициентов деления ДПКД2. в среднем коэффициент деления равен N, М, а выходная частота управляемого генератора СВ(,,У (N,M), где IQ тактовая частота опорного генератора 5.

ЦАП 11, преобразователь 10 и элемент 12 дифференцирования образуют схему компенсации помех дробности, возникающих при скачкообразном изменении целочисленных коэффициентов деления ДПКД 2.Код содержимого второго накопителя 7, в котором содержится информация об интеграле фазовой ошибки, поступает на первый вход ЦАП 11 и преобразуется в отрицательное напряжение, которое затем дифференцируется элементом 12 дифференцирования и подается на вход фильтра k. Складываясь с выходным напряжением ИФД 3,компенсирующий сигнал уменьшает скачки фазы выходного колебания управляемого генератора 1. Неравномерность компенсации помех дробности в диапазоне рабочих частот уменьшается за счет формирования опорного напряжения ЦАП 1 1 из выходной последовательности импульсов ДПКД 2 при помощи преобразователя 10, В диапазоне рабочих частот управляемого генератора 1 скважность импульсов ДПКД 2 меняется, соответствующим образом меняется опорное напряжение, формируемое преобразователем 10, а следовательно, меняется компенсирующее воздействие, вырабатываемое ЦАП 11.

Первый и второй накопители 6 и 7 имеют входы начальной установки. При включении или переключении частоты блок 13 задания в соответствии с поступающим на его первый вход значением кода дробной части коэффициента деле10

20

25

ния М формирует код начальных состояний первого и второго накопителей 6 и 7 и в течение одного периода тактовой частоты выдает сформированные коды на выходы. При этом до следующего пе- реключения частоты цифрового синтезатора частоты работа блока 13 задания заканчивается, а в первом и втором накопителях 6 и 7 начинается процесс изменения их содержимого, вызывающий чередование четырех целочисленных коэффициентов деления ДПКД 2.

Начальные состояния первого и второго накопителей 6 и 71 однократно 5 устанавливаемые с помощью блока 13 задания при смене М, для каждого значения М выбраны такими, что в процессе изменения содержимого первого и второго накопителей 6 и 7 порядок по- ,явления во времени и величина скачкообразных изменений целочисленного коэффициента деления ДПКД 2 оптимальны с точки зрения получения минимума помех дробности в выходном колебании управляемого генератора 1.

Блок 13 задания содержит первый и второй блоки 1 и 15 памяти, на адресные входы которых поступает код дробной части коэффициента деления М. Этот же код поступает на вход регистра 1б и на первый вход элемента 17 совпадения. В регистре 1б запоминается текущее значение кода дробной части М. При смене М вновь установленное значение М | не совпадает с заполненным в регистре 16 значением Mj. При Mi + i , на выходе элемента совпадения появляется сигнал логической единицы и очередной тактовый импульс, поступа-.п разователя, последовательно соединен- ющий на С-вход D-триггера 18, устанав- ные элемент задержки и сумматор ко- ливает D-триггер 18 в единичное состояние. Появившийся на вторых входах первого и второго блоков 14- и 15 памяти сигнал служит командой на выдачу ., кодов начальных состояний первого и второго накопителей 6 и 7, запомненных в первом и втором блоках 1 и 15 памяти по адресу М . Этот же сигнал с выхода D-триггера 18 служит сигналом JQ записи входного кода М ,-. , в регистр 1б. После появления через время задержки в регистре 1б на его выходах кода

30

35

вого и второго блоков 14 и 15 памяти и переводит регистр 1б в режим хране ния записанной информации, т.е. при каждой смене значения М в течение одного периода тактовой частоты осущ ствляется выдача кода начальных состояний первого и второго накопителей 6 и 7- При этом записанные в первом и втором блоках 1 4 и 15 памяти коды начальных состояний для каждого значения М являются оптимальными с зрения получения минимума помех дробности. Критерием выбора значения начальных состояний является достижение минимума дисперсий отклонения мгновен ных значений фазы от линейно изменяющегося среднего, поскольку линейный закон изменения фазы обуславливает отсутствие помех в выходном сигнале.

Формула изобретения

Цифровой синтезатор частоты, содер жащий соединенные в кольца управляемый генератор, делитель частоты с переменным коэффициентом деления, им- пульсно-фазовый детектор и фильтр ниж них частот, последовательно соединенные первый накопитель, второй накопитель, цифроаналогоЕзый поеобразовотель и элемент дифференцирования, которого подключен к входу фильтра нижних частот, преобразователь длительности импульса в напряжение,вход и выход которого соединены соответственно с выходом делителя частоты с переменным коэффициентом деления и BTopbiM входом цифроаналогового преобдов, выход которого подключен к установочному входу делителя частоты с переменным коэффициентом деления, кодовый вход сумматора кодов является входом кода целой части коэфф1-1циента деления цифрового синтезатора частоты выход переполнения первого накопителя соединен с вторым входом сумматора кодов, третий вход которого объединен с входом элемента задержки и подключен к выходу переполнения второго накопителя, тактовый вход элемента задержки, тактовый вход первого накопителя, тактовый вход второго накопителя и второй вход импульсно-фазового детектора объединены и подключены к выходу опорного генератора, а вход первого накопителя является входом

М. на выходе элемента 17 совпадения формируется сигнал логического нуля и очередной тактовый импульс возвраща- ет D-триггер 18 в нулевое состояние. Это приводит к прекращению выдачи кода начальных состояний с выходов пер

разователя, последовательно соединен- ные элемент задержки и сумматор ко-

вого и второго блоков 14 и 15 памяти и переводит регистр 1б в режим хранения записанной информации, т.е. при каждой смене значения М в течение одного периода тактовой частоты осуществляется выдача кода начальных состояний первого и второго накопителей 6 и 7- При этом записанные в первом и втором блоках 1 4 и 15 памяти коды начальных состояний для каждого значения М являются оптимальными с зрения получения минимума помех дробности. Критерием выбора значения начальных состояний является достижение минимума дисперсий отклонения мгновенных значений фазы от линейно изменяющегося среднего, поскольку линейный закон изменения фазы обуславливает отсутствие помех в выходном сигнале.

Формула изобретения

Цифровой синтезатор частоты, содержащий соединенные в кольца управляемый генератор, делитель частоты с переменным коэффициентом деления, им- пульсно-фазовый детектор и фильтр нижних частот, последовательно соединенные первый накопитель, второй накопитель, цифроаналогоЕзый поеобразовотель и элемент дифференцирования, которого подключен к входу фильтра нижних частот, преобразователь длительности импульса в напряжение,вход и выход которого соединены соответственно с выходом делителя частоты с переменным коэффициентом деления и BTopbiM входом цифроаналогового преобразователя, последовательно соединен- ные элемент задержки и сумматор ко-

дов, выход которого подключен к установочному входу делителя частоты с переменным коэффициентом деления, кодовый вход сумматора кодов является входом кода целой части коэфф1-1циента деления цифрового синтезатора частоты, выход переполнения первого накопителя соединен с вторым входом сумматора кодов, третий вход которого объединен с входом элемента задержки и подключен к выходу переполнения второго накопителя, тактовый вход элемента задержки, тактовый вход первого накопителя, тактовый вход второго накопителя и второй вход импульсно-фазового детектора объединены и подключены к выходу опорного генератора, а вход первого накопителя является входом

кода дробной части коэффициента деления цифрового синтезатора частоты, отличающийся тем, что, с целью повышения спектральной частоты, выходного сигнала, введен блок задания начальных кодов, первый и второй выходы которого подключены соответст151536 8

венно к установочному входу первого накопителя и установочному входу второго накопителя, тактовый вход блока задания начальных кодов соединен с выходом опорного генератора, а кодовый вход блока задания начальных кодов подключен к входу первого накопителя.

Авторы

Даты

1989-10-15—Публикация

1987-12-28—Подача