блок 7 ввода-вывода, дешифратор 8, счетчик 9, элементы И 10-14, элемент ИДИ 15, триггер 16, одновибратор 17, коммутатор 18 с трехстабильным состоянием и триггер 19. Цель достигается путем такой организации работы устройства в режиме накопления информации, при которой после получения сигнала конца преобразования информации код инфомации переносится в счетчик, а операционный блок считывает из блока памяти во внутренние регис1

Изобретение относится к вычислительной технике и может быть использовано в устройствах цифровой обработки информации в различных спектрометрических системах, например, для накопления информации при измерениях амплитудного или временного спектров,

Цель изобретения - повышение быстродействия.

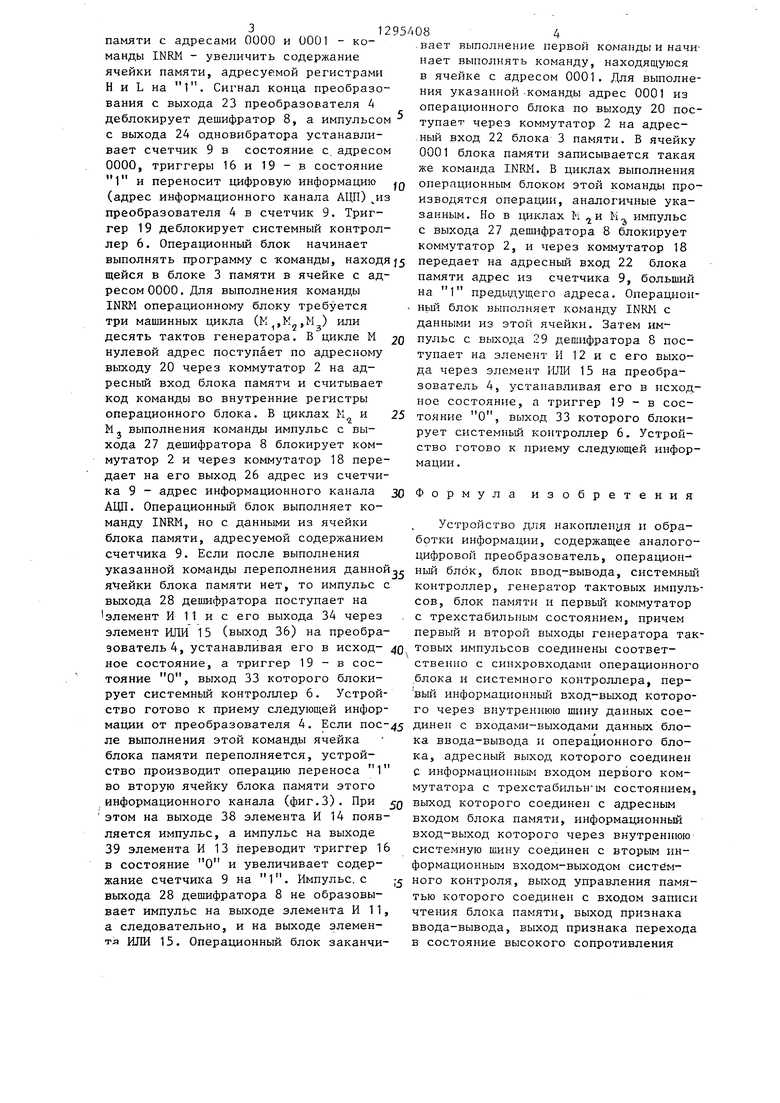

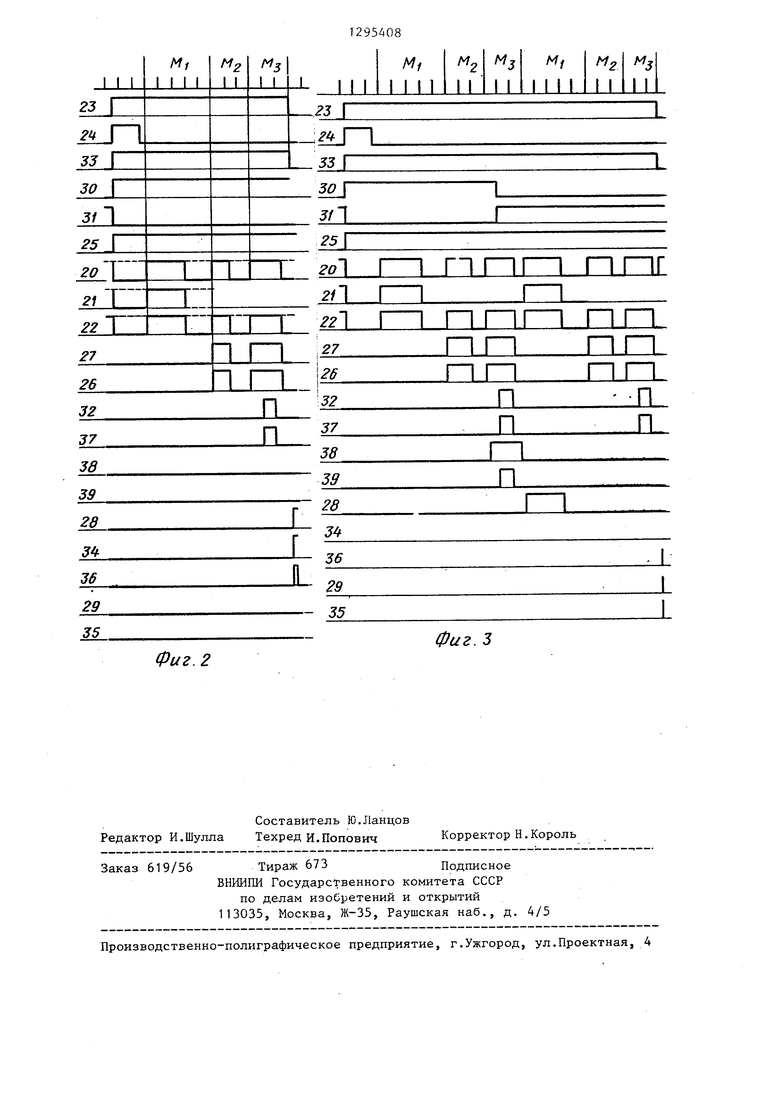

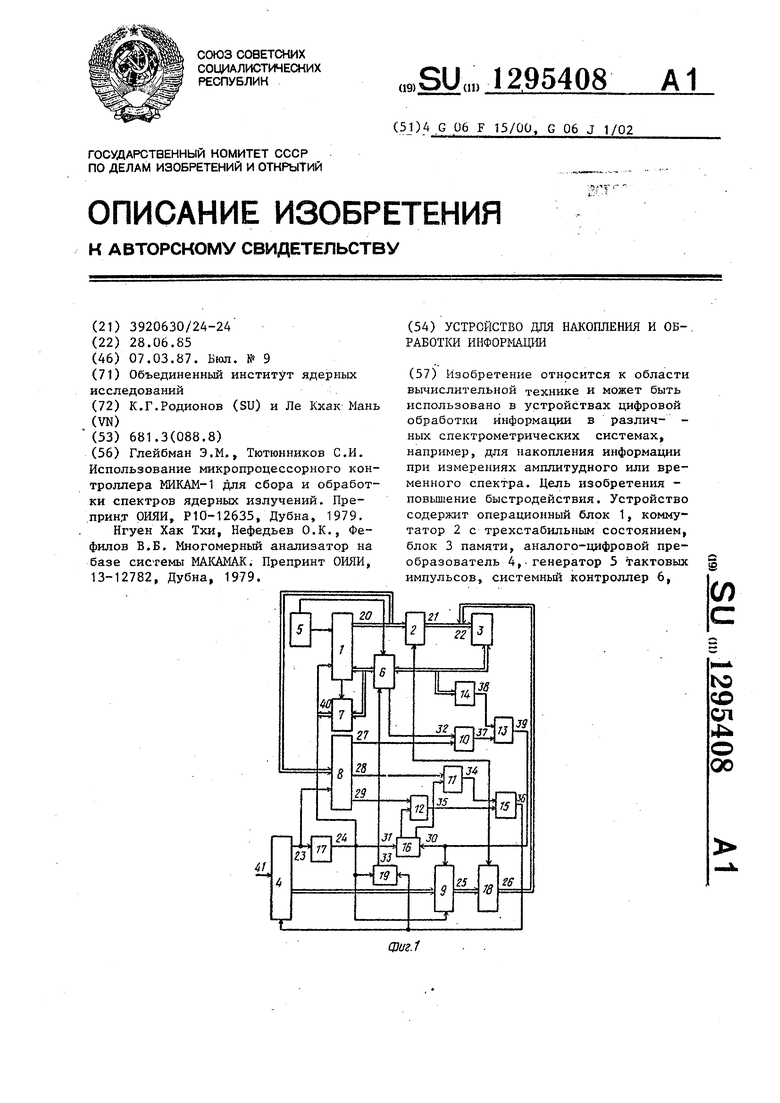

На фиг.1 представлена функциональная схема предлагаемого устройства| на фиг,2 и 3 - временные диаграммы, иллюстрирующие работу устройства.

Устройство для накопления и обработки информации содержит операционный блок 1, первый коммутатор 2 с трехстабильным состоянием, блок 3 памяти, аналого-цифровой преобразователь (АЦП) 4, генератор 5 тактовых импульсов, системный контроллер 6, блок 7 ввода-вывода, дешифратор 8, счетчик 9, третий 10, первый 11, второй 12, четвертый 13 и пятый 14 элементы И, элемент ИЛИ 15, первый триг гер 16, одновибратор 17, второй коммутатор 18 с трехстабильным состоянием, второй триггер 19, адресный выход 20 операционного блока, выход 21 первого коммутатора с трехстабильным состоянием, адресный вход 22 блока памяти, выход 23 признака конца преобразования аналого-цифрового преоб-- разователя, выход 24 одновибратора, выход 25 счетчика, выход 26 второго коммутатора с трехстабильным состоянием, выходы 27-29 дешифратора, выходы 30 и 31 установки первого триггетры команду - увеличить содержание ячейки блока памяти на 1. Затем дешифратор блокирует коммутатор и из счетчика через коммутатор выдается на адресный вход блока памяти адрес информационного канала. Операционный блок выполняет команду, но с данными ячейки блока памяти, указанной адресом информационного канала. Для выполнения операции +1 в ячейку блока памяти требуется только одна команда. 3 ил.

ра, выход 32 управления записью в память системного контроллера, выход 33 второго триггера, выход 34 первого элемента И, выход 35 второго злемен5 та И, выход 36 элемента ИЛИ, выход 37 третьего элемента И, выход 38 пятого элемента И, выход 39 четвертого элемента И, шину 40 данных и аналоговый вход 41. На фиг.2 и 3 нумерация

О диаграмм соответствует номерам выходов блоков устройства.

Системный контроллер предназначен для формирования управляющих сигна- 5 лов и сопряжения с операционным блоком, памятью и с интерфейсными схе- ,чами периферийных устройств. Систем- ньй контроллбф может быть реализован на базе КР 580ВК28. Операционный блок 20 может быть реализован на основе

КР580ИК80А. В качестве преобразователя можно использовать, например, блок временного или амплитудного кодирования. В качестве коммутаторов

25

2 и 18 можно использовать схемы типа К 589, Ап 16.

Устройство работает следующим образом.

Для накопления информации, получаемой от преобразователя 4, например, в блоке 3 памя:ти выделяется область. В этой области для одного информационного канала используются две ячейки

памяти. Предварительно в регистры операционного блока, например в Н и L, записывается произвольный адрес ячейки блока памяти, а в ячейки блока

312

памяти с адресами 0000 и 0001 - команды INRM - увеличить содержание ячейки памяти, адресуемой регистрами Н и L на 1. Сигнал конца преобразования с выхода 23 преобразователя 4 деблокирует дешифратор 8, а импульсом с выхода 24 одновибратора устанавливает счетчик 9 в состояние с адресом 0000, триггеры 16 и 19 - в состояние 1 и переносит цифровую информацию (адрес информационного канала АЦП) jis преобразователя 4 в счетчик 9. Триггер 19 деблокирует системный контроллер 6. Операционный блок начинает выполнять программу с команды, находя щейся в блоке 3 памяти в ячейке с адресом 0000. Для выполнения команды INRM операционному блоку требуется три машинных цикла (К,К ,М ) или десять т.актов генератора, В цикле М нулевой адрес поступает по адресному выходу 20 через коммутатор 2 на адресный вход блока памяти и считывает код команды во внутренние регистры операционного блока, В циклах М и М J выполнения команды импульс с выхода 27 дешифратора 8 блокирует коммутатор 2 и через коммутатор 18 передает на его выход 26 адрес из счетчика 9 - адрес информационного канала АЦП. Операционный блок выполняет команду INRM, но с данными из ячейки блока памяти, адресуемой содержанием счетчика 9. Если после выполнения указанной команды переполнения данной ячейки блока памяти нет, то импульс с вькода 28 дешифратора поступает на элемент И 11 и с его выхода 34 через элемент ИЛИ 15 (выход 36) на преобразователь 4, устанавливая его в исход- ное состояние, а триггер 19 - в состояние О, выход 33 которого блокирует системньш контроллер 6. Устройство готово к приему следующей информации от преобразователя 4. Если после выполнения этой команды ячейка блока памяти переполняется, устройство производит операцию переноса 1 во вторую ячейку блока памяти этого информационного канала (фиг.З). При этом на выходе 38 элемента И 14 появляется импульс, а импульс на выходе 39 элемента И 13 переводит триггер 16 в состояние О и увеличивает содержание счетчика 9 на 1. Импульс, с выхода 28 дешифратора 8 не образовывает импульс на выходе элемента И 11, а следовательно, и на выходе элемен- тя ИЛИ 15. Операционный блок заканчи084

.вает выполнение первой и начинает выполнять команду, находящуюся в ячейке с адресом 0001. Для выполнения указанной-команды адрес 0001 из опера1Ц1онного блока по выходу 20 поступает через коммутатор 2 на адресный вход 22 блока 3 памяти. В ячейку 0001 блока памяти записывается такая же команда INRM. В циклах выполнения операционнь м блоком этой команды производятся операции, аналогичные указанным. Но в гщклах М и М импульс с выхода 27 дешифратора 8 блокирует коммутатор 2, и через коммутатор 18 передает на адресный вход 22 блока памяти адрес из счетчика 9, больший на 1 предьщущего адреса. Операцыои- ньш блок выполняет команду INRM с данными из этой ячейки. Затем импульс с выхода 29 дешифратора 8 поступает на элемент И 12 и с его выхода через элемент ИЛИ 15 на преобразователь 4, устанавливая его в исходное состояние, а триггер 19 - в состояние О, выход 33 которого блокирует системный контроллер 6. Устройство готово к приему следующей информации .

Формула изобретения

Устройство для накоплепуя и обработки информации, содержащее аналого- цифровой преобразователь, операцион- ньм блок, блок ввод-вывода, системньш контроллер, генератор тактовых импульсов, блок памяти и первый коммутатор с трехстабильным состоянием, причем первый и второй выходы генератора тактовых импульсов соединены соответственно с синхровходами операционного блока и системного контроллера, пер- вьш информационный вход-выход которого через внутреннюю шину данных соединен с входами-выходами данных блока ввода-вывода и операционного блока, адресный выход которого соединен с информационным входом первого коммутатора с трехстабильн ш состоянием, выход которого соединен с адресным входом блока памяти, информационный вход-выход которого через внутреннюю системную шину соединен с вторым информационным входом-выходом системного контроля, выход управления памятью которого соединен с входом записи чтения блока памяти, выход признака ввода-вывода, выход признака перехода в состояние высокого сопротивления

и выход признака записи в память операционного блока соединены соответственно с входом признака ввода-вывода, входом управления состояниями выходов и входом признака записи в память системного контроллера, выход управления вводом-выводом КОТОРОГО соединен с входом управления вводом- выводом блока ввода-вывода, информационный вход-выход которого соединен с шиной данных устройства, аналоговый вход устройства соединен с информационным входом аналого-цифрового преобразователя, отличающееся тем, что, с целью повышения быстродействия, оно дополнительно содержит одновибратор, дешифратор, пять элементов И, элемент ИЛИ, два триггера, счетчик и второй коммутатор с трех- стабильным состоянием, причем выход конца преобразования аналого-цифрового преобразователя соединен с входом одновибратора и со стробирующим входом дешифратора, информационный вход которого соединен с адресным выходом операционного блока, вход сброса которого соединен с выходом одновибратора, с входами установки в 1 первого и второго триггеров и входом записи счетчика, информационный вход которого соединен с информационным выходом аналого-цифрового преобразователя, вход управления кондом преобразования которого соединен с входом

Ю

15

95А086

установки в О второго триггера и с выходом элемента ИЖ, первый и второй входы которого соединены с выходами соответственно первого и второго элементов И, первые входы которых соединены соответственно с первым .и вторым выходаг ш дешифратора, третий выход дешифратора соединен с первым входом третьего элемента И и управляющими входами первого и второго

коммутаторов с трехстабильным состоянием, информационный вход и выход второго коммутатора с трехстабильным состоянием соединены соответственно с выходом счетчика и адресным входом блока памяти, второй вход третьего элемента И соединен с выходом управления записью в память системного контроллера, вход блокировки которого соединен с выходом второго триггера, вход установки в О первого триггера соединен со счетным входом счетчика и с выходом четвертого элемента И, первый и второй входы которого соединены соответственно с выходами третьего и пятого элементов И, вход которого подключен через внутреннюю системную шину к информационному входу-выходу системного контроллера, вторые входы первого и второго элементов И соединены соответственно с прямым и инверсным выходами первого триггера.

20

25

30

Фиг. 2

Редактор И.Шулла

Составитель Ю.Ланцов Техред И.Попович

619/56

Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул,Проектная, 4

Корректор Н.Король

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| ОПЕРАТИВНЫЙ КОНТРОЛЛЕР СУММАРНОЙ МОЩНОСТИ НАГРУЗКИ ГРУППЫ ЭНЕРГОПОТРЕБИТЕЛЕЙ | 1998 |

|

RU2145717C1 |

| Программируемый контроллер | 1985 |

|

SU1509887A2 |

| Микропрограммное устройство управления | 1983 |

|

SU1108448A1 |

| Устройство для обучения | 1987 |

|

SU1559366A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА НА БАЗЕ МАТРИЦЫ ПРОЦЕССОРНЫХ ЭЛЕМЕНТОВ | 1998 |

|

RU2117326C1 |

| Микропрограммное устройство управления | 1985 |

|

SU1319029A1 |

| Устройство для ввода информации | 1989 |

|

SU1682996A1 |

| Многоканальное устройство ввода аналоговой информации | 1986 |

|

SU1403057A1 |

Изобретение относится к области вычислительной технике и может быть использовано в устройствах цифровой обработки информации в различ- - ных спектрометрических системах, например, для накопления информации при измерениях амплитудного или временного спектра. Цель изобретения - повьшение быстродействия. Устройство содержит операционный блок 1, коммутатор 2 с трехстабильным состоянием, блок 3 памяти, аналого-цифровой преобразователь 4,-генератор 5 тактовых импульсов, системньй контроллер 6, о Ф (Л to со 01 4: О 00

| Глейбман Э.М., Тютюнников С.И | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Пре- .прин,т РИЯИ, Р10-12635, Дубна, 1979 | |||

| Нгуен Хак Тхи, Нефедьев O.K., Фе- филов В.В, Многомерный анализатор на базе системы МАКАМАК | |||

| Препринт СИЯЙ, 13-12782, Дубна, 1979. | |||

Авторы

Даты

1987-03-07—Публикация

1985-06-28—Подача