рокоманд, группу блоков памяти 2.1- 2,п нанокоманд, блок формирования адреса 3, регистр А команд, регистры адреса 5 и 7, буферный регистр 6, регистр нанокоманд 8, блоки контроля 9 и 10, блок 11 коммутации, коммута-, торы адреса 12, 13 и 14, мультиплек131

1

Изобретение относится к вычислительной технике и может быть использовано при построении отказоустойчивых микропрограммных процессоров, программируемых контроллеров, вычислительных и управляющих систем с микропрограммным управлением.

Целью изобретения является повышение отказоустойчивости устройства.

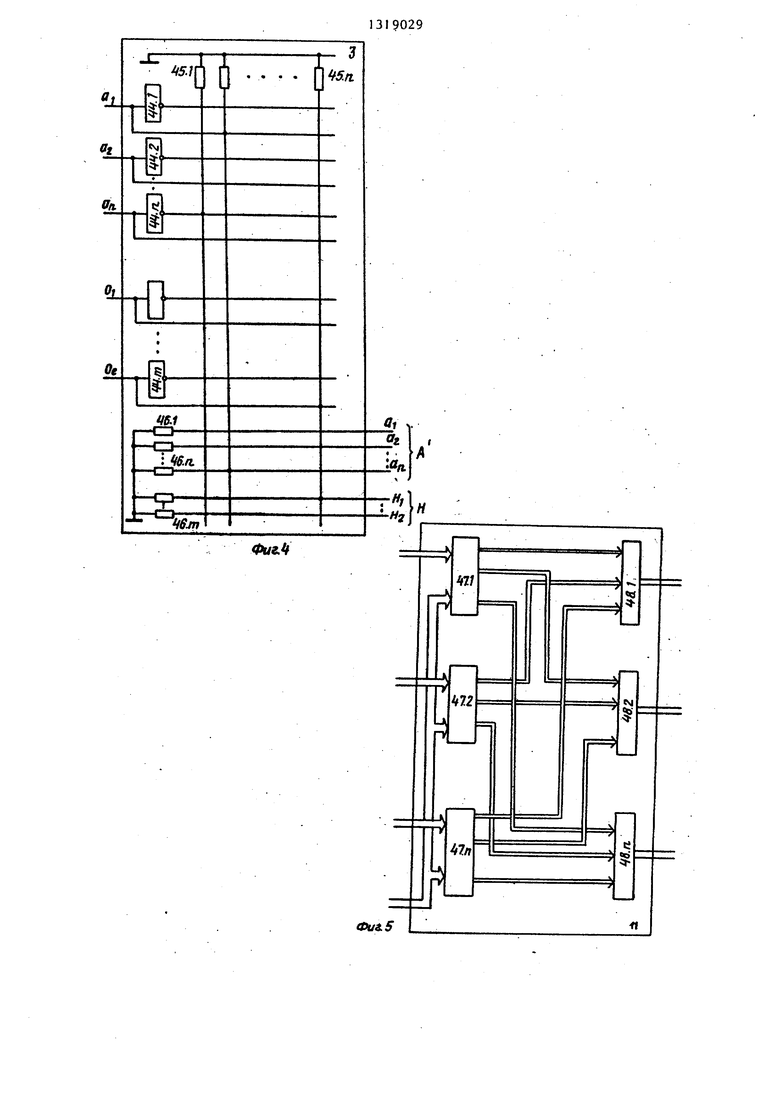

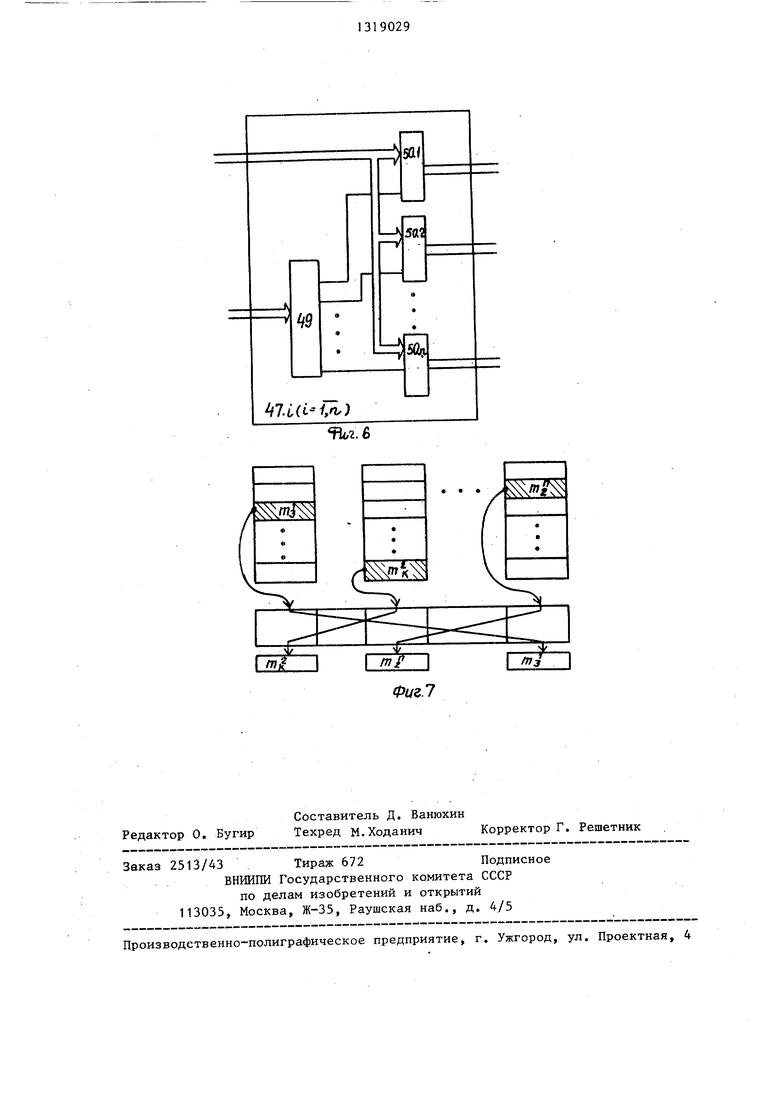

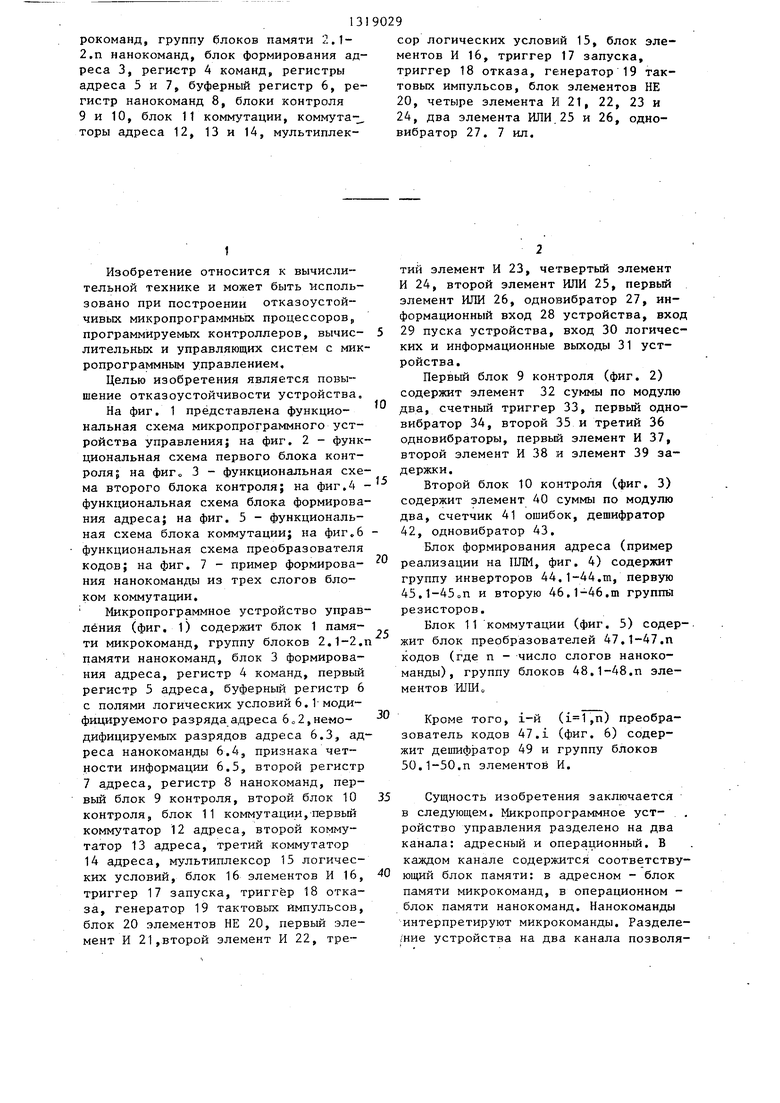

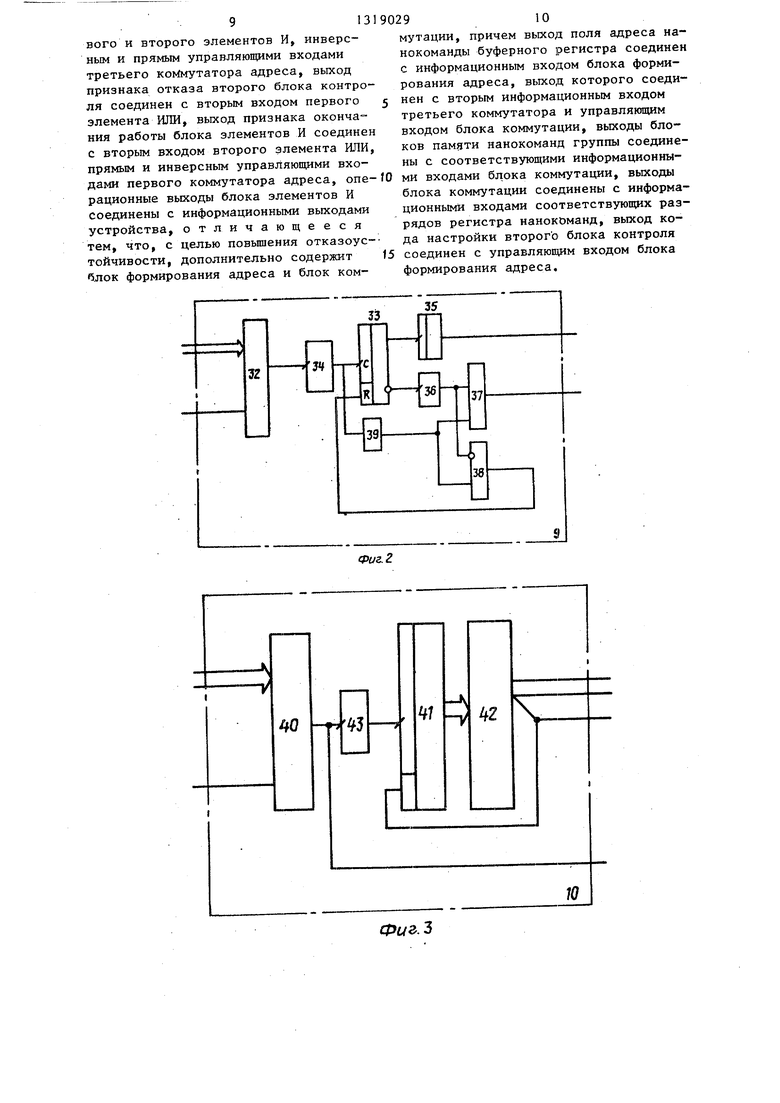

На фиг. 1 представлена функциональная схема микропрограммного устройства управления; на фиг. 2 - функциональная схема первого блока контроля; на фиго 3 - функциональная схема второго блока контроля; на фиг.4 - функциональная схема блока формирования адреса; на фиг. 5 - функциональная схема блока коммутации; на фиг.6 функциональная схема преобразователя кодов; на фиг. 7 - пример формирования нанокоманды из трех слогов блоком коммутации.

Микропрограммное устройство управления (фиг. 1) содержит блок 1 памяти микрокоманд, группу блоков 2.1-2.П памяти нанокоманд, блок 3 формирования адреса, регистр 4 команд, первый регистр 5 адреса, буферный регистр 6 с полями логических условий 6. V модифицируемого разряда адреса 6„2,немо- дифицируемых разрядов адреса 6.3, адреса нанокоманды 6.4, признака четности информации 6.5., второй регистр 7 адреса, регистр 8 нанокоманд, первый блок 9 контроля, второй блок 10 контроля, блок 11 коммутации,первый коммутатор 12 адреса, второй коммутатор 13 адреса, третий коммутатор 14 адреса, мультиплексор 15 логических условий, блок 16 элементов И 16, триггер 17 запуска, триггер 18 отказа, генератор 19 тактовых импульсов, блок 20 элементов НЕ 20, первый элемент И 21,второй элемент И 22, тре1319029

сор логических условий 15, блок элементов И 16, триггер 17 запуска, триггер 18 отказа, генератор 19 тактовых импульсов, блок элементов НЕ 20, четыре элемента И 21, 22, 23 и 24, два элемента ИЛИ 25 и 26, одно- вибратор 27. 7 ил.

5

о

5

0

5

0

тий элемент И 23, четвертый элемент И 24, второй элемент ИЛИ 25, первый элемент ИЛИ 26, одновибратор 27, информационный вход 28 устройства, вход 29 пуска устройства, вход 30 логических и информационные выходы 31 устройства.

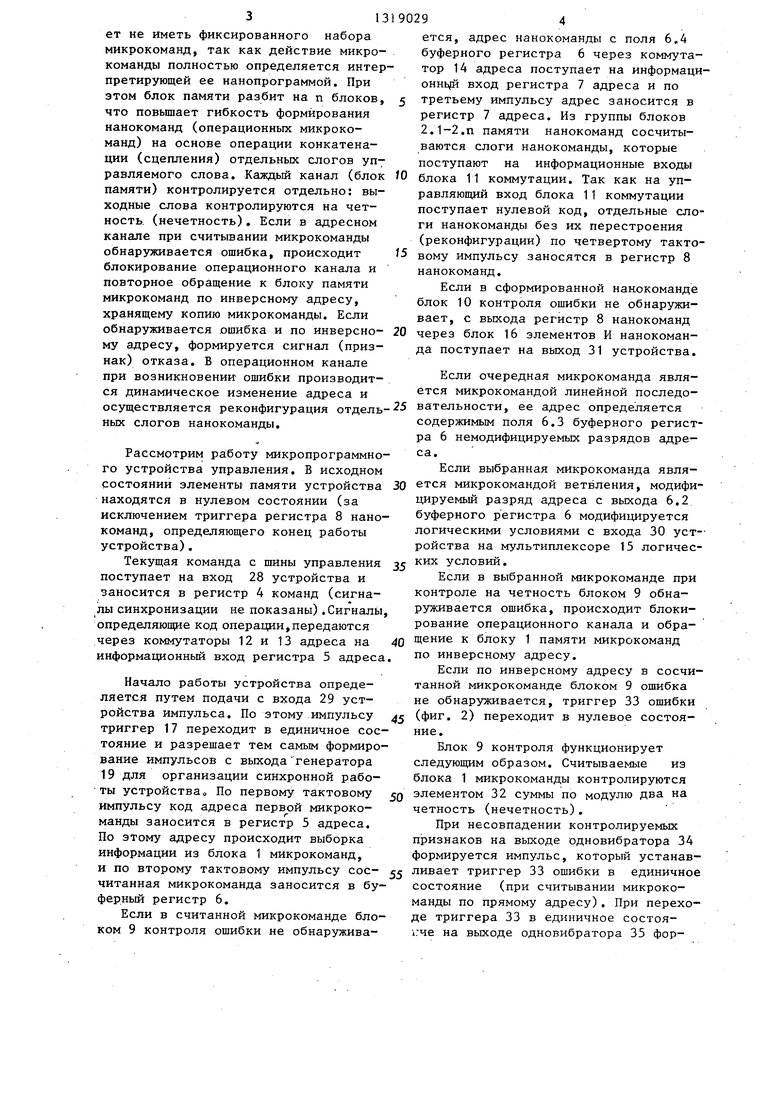

Первый блок 9 контроля (фиг. 2) содержит элемент 32 суммы по модулю два, счетный триггер 33, первьм одно- вибратор 34, второй 35 и третий 36 одновибраторы, первый элемент И 37, второй элемент И 38 и элемент 39 задержки.

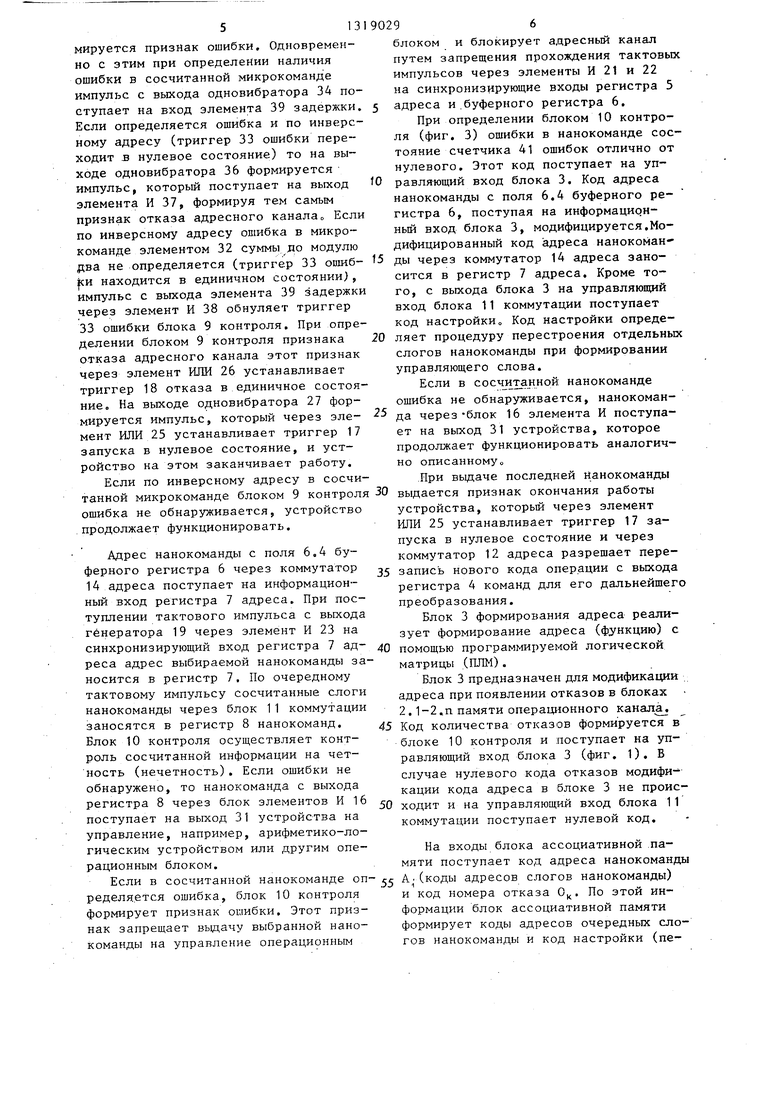

Второй блок 10 контроля (фиг. 3) содержит элемент 40 суммы по модулю два, счетчик 41 ошибок, дешифратор 42, одновибратор 43.

Блок формирования адреса (пример реализации на 1ШМ, фиг. 4) содержит группу инверторов 44.1-44.т, первую 45.1-45оп и вторую 46.1-46.т группа резисторов.

Блок 11 коммутации (фиг. 5) содер-. жит блок преобразователей 47.1-47.п кодов (где п - число слогов нанокоманды) , группу блоков 48.1-48.п элементов ШШо

Кроме того, i-й(,п) преобразователь кодов 47.1(фиг. 6) содержит дешифратор 49 игруппу блоков 50.1-50.п элементовИ.

Сущность изобретения заключается в следующем. Микропрограммное устройство управления разделено на два канала; адресный и операционный. В каждом канале содержится соответствующий блок памяти: в адресном - блок памяти микрокоманд, в операционном - блок памяти нанокоманд. Нанокоманды интерпретируют микрокоманды. Разделе- /ние устройства на два канала позволяет не иметь фиксированного набора микрокоманд, так как действие микрокоманды полностью определяется интерпретирующей ее нанопрограммой. При этом блок памяти разбит на п блоков, что повышает гибкость формирования нанокоманд (операционных микрокоманд) на основе операции конкатенации (сцепления) отдельных слогов управляемого слова. Каждый канал (блок памяти) контролируется отдельно: выходные слова контролируются на четность, (нечетность). Если в адресном канале при считывании микрокоманды обнаруживается ошибка, происходит блокирование операционного канала и повторное обращение к блоку памяти микрокоманд по инверсному адресу, хранящему копию микрокоманды. Если обнаруживается ошибка и по инверсно- му адресу, формируется сигнал (признак) отказа. В операционном канале при возникновении- ошибки производится динамическое изменение адреса и осуществляется реконфигурация отдель нык слогов нанокоманды.

Рассмотрим ра:боту микропрограммного устройства управления. В исходном состоянии элементы памяти устройства находятся в нулевом состоянии (за исключением триггера регистра 8 нанокоманд, определяющего конец работы устройства).

Текущая команда с шины управления поступает на вход 28 устройства и заносится в регистр 4 команд (сигналы синхронизации не показаны).Сигналы определяющие код операции,передаются через коммутаторы 12 и 13 адреса на информационный вход регистра 5 адреса

Начало работы устройства определяется путем подачи с входа 29 устройства импульса. По этому импульсу триггер 17 переходит в единичное состояние и разрешает тем самым формирование импульсов с выхода генератора 19 для организации синхронной работы устройства По первому тактовому импульсу код адреса первой микрокоманды заносится в регистр 5 адреса. По этому адресу происходит выборка информации из блока 1 микрокоманд, и по второму тактовому импульсу сое- читанная микрокоманда заносится в буферный регистр 6.

Если в считанной микрокоманде блоком 9 контроля ошибки не обнаруживается, адрес нанокоманды с поля 6,4 буферного регистра 6 через коммутатор 14 адреса поступает на информаци онньрй вход регистра 7 адреса и по третьему импульсу адрес заносится в регистр 7 адреса. Из группы блоков 2.1-2.П памяти нанокоманд сосчитываются слоги нанокоманды, которые поступают на информационные входы блока 11 коммутации. Так как на управляющий вход блока 11 коммутации поступает нулевой код, отдельные слоги нанокоманды без их перестроения (реконфигурации) по четвертому тактовому импульсу заносятся в регистр 8 нанокоманд.

Если в сформированной нанокоманде блок 10 контроля ошибки не обнаруживает, с выхода регистр 8 нанокоманд через блок 16 элементов И нанокоман- да поступает на выход 31 устройства.

Если очередная микрокоманда является микрокомандой линейной последовательности, ее адрес определяется содержимым поля 6.3 буферного регистра 6 немодифицируемых разрядов адреса.

Если выбранная микрокоманда является микрокомандой ветвления, модифицируемый разряд адреса с выхода 6.2 буферного регистра 6 модифицируется логическими условиями с входа 30 устройства на мультиплексоре 15 логических условий.

Если в выбранной микрокоманде при контроле на четность блоком 9 обнаруживается ошибка, происходит блокирование операционного канала и обращение к блоку 1 памяти микрокоманд по инверсному адресу.

Если по инверсному адресу в сосчитанной микрокоманде блоком 9 ошибка не обнаруживается, триггер 33 ошибки (фиг. 2) переходит в нулевое состояние.

Блок 9 контроля функционирует следующим образом. Считываемые из блока 1 микрокоманды контролируются элементом 32 суммы по модулю два на четность (нечетность).

При несовпадении контролируемых признаков на выходе одновибратора 34 формируется импульс, который устанавливает триггер 33 ошибки в единичное состояние (при считывании микрокоманды по прямому адресу). При переходе триггера 33 в единичное состоя- :че на выходе одновибратора 35 фор513

мируется признак ошибки. Одновременно с этим при определении наличия ошибки в сосчитанной микрокоманде импульс с выхода одновибратора 34 поступает на вход элемента 39 задержки. Если определяется ошибка и по инверсному адресу (триггер 33 ошибки переходит в нулевое состояние) то на выходе одновибратора 36 формируется импульс, который поступает на выход элемента И 37, формируя тем признак отказа адресного канала Если по инверсному адресу ошибка в микрокоманде элементом 32 суммы до модулю два не определяется (триггер 33 ошиб- и находится в единичном состоянии), импульс с выхода элемента 39 задержки через элемент И 38 обнуляет триггер 33 ошибки блока 9 контроля. При определении блоком 9 контроля признака отказа адресного канала этот признак через элемент ИЖ 26 устанавливает триггер 18 отказа в единичное состояние. На выходе одновибратора 27 формируется импульс, который через элемент ИЛИ 25 устанавливает триггер 17 запуска в нулевое состояние, и устройство на этом заканчивает работу.

Если по инверсному адресу в сосчитанной микрокоманде блоком 9 контроля ошибка не обнаруживается, устройство продолжает функционировать.

Адрес нанокоманды с поля 6.4 буферного регистра 6 через коммутатор 14 адреса поступает на информационный вход регистра 7 адреса. При поступлении тактового импульса с выхода генератора 19 через элемент И 23 на синхронизирующий вход регистра 7 адреса адрес выбираемой нанокоманды заносится в регистр 7. По очередному тактовому импульсу сосчитанные слоги нанокоманды через блок 11 коммутации заносятся в регистр 8 нанокоманд. Блок 10 контроля осуществляет контроль сосчитанной информации на четность (нечетность). Если ошибки не обнаружено, то нанокоманда с выхода регистра 8 через блок элементов И 16 поступает на выход 31 устройства на управление, например, арифметико-логическим устройством или другим операционным блоком.

Если в сосчитанной нанокоманде определяется ошибка, блок 10 контроля формирует признак ошибки. Этот признак запрещает выдачу выбранной нанокоманды на управление операционным

96

блоком и блокирует адресный канал путем запрещения прохождения тактовых импульсов через элементы И 21 и 22 на синхронизирующие входы регистра 5

адреса и.буферного регистра 6.

При определении блоком 10 контроля (фиг. 3) ошибки в нанокоманде состояние счетчика 41 ошибок отлично от нулевого. Этот код поступает на управля-ющий вход блока 3. Код адреса нанокоманды с поля 6.4 буферного регистра 6, поступая на информационный вход блока 3, модифицируется.Модифицированный код адреса нанокоманды через коммутатор 14 адреса заносится в регистр 7 адреса. Кроме того, с выхода блока 3 на управляющий вход блока 11 коммутации поступает код настройки Код настройки опреде-

ляет процедуру перестроения отдельных слогов нанокоманды при формировании управляющего слова.

Если в сосч 1танной нанокоманде ошибка не обнаруживается, нанокоманда через блок 16 элемента И поступает на выход 31 устройства, которое продолжает функционировать аналогично описанному

При вьщаче последней Нанокоманды

выдается признак окончания работы устройства, который через элемент ИЛИ 25 устанавливает триггер 17 запуска в нулевое состояние и через коммутатор 12 адреса разрешает перезапись нового кода операции с выхода регистра 4 команд для его дальнейшего преобразования.

Блок 3 формирования адреса реализует формирование адреса (функцию) с

помощью программируемой логической матрицы (Ш1М) .

Блок 3 предназначен для модификации адреса при появлении отказов в блоках 2.1-2.п памяти операционного канала

Код количества отказов формируется в блоке 10 контроля и поступает на управляющий вход блока 3 (фиг. 1). В случае нулевого кода отказов модифи- кации кода адреса в блоке 3 не происходит и на управляющий вход блока 11 коммутации поступает нулевой код.

На входы блока ассоциативной памяти поступает код адреса нанокоманды (коды адресов слогов нанокоманды) и код номера отказа 0. По этой информации блок ассоциативной памяти формирует коды адресов очередных слогов нанокоманды и код настройки (пе

рестроения слогов при формировании нанокоманды в блоке коммутации I 1 .

Формула изобретения

Микропрограммное устройство управления, содержащее блок памяти, микрокоманд, группу блоков памяти наноко- манд, три коммутатора адреса, два блока контроля, регистр команд, два регистра адреса, буферный регистр, мультиплексор логических условий, ре гистр нанокоманд, блок элементов И, блок элементов НЕ, триггер запуска, генератор тактовых импульсов, триггер отказа, четыре элемента И, два элемента ИЛИ, одновибратор, причем информационный вход устройства соединен с входом регистра команд, выход которого соединен с первым информационным входом первого коммутатора адреса, вход пуска устройства соединен с единичным входом триггера запус

ка, прямой выход которого соединен

ход генератора тактовых импульсов соединен с прямьп входом третьего элемента И, выход которого соединен с синхронизирующим входом второго регистра адреса, выходы полей которого соединен с адресными входами соответствующих блоков памяти нанокоманд группы, четвертый выход генератора тактовых импульсов соединен с прямым входом четвертого элемента И, выход которого соединен с синхронизирующим входом регистра нанокоманд, выход первого коммутатора адреса соединен с первым информационным входом второго коммутатора адреса и входом блока элементов НЕ, выход которого соединен с вторым информационным.входом второго коммутатора адреса, выход которого соединен с информационным входом первого регистра адреса, выход поля адреса нанокоманды буферного регистра соединен с первым информационным входом третьего коммутатора адреса, выход которого соединен.с информационным входом второго регистра адреса, выходы поля кода логических условий, поля немодифицируемых разрядов адреса, поля адреса нанокоманды буферного регистра соединены с информа- 30 ционным входом первого блока контрос входом пуска генератора тактовых импульсов первый выход которого соединен с прямым входом первого элемента И, выход которого соединен с синхронизирующим входом первого регистра адреса, выход-первого регистра адреса соединен с входом адреса блока памяти микрокоманд, выход которого соединен с информационным входом буферного регистра, выход поля 35 блока контроля соединен с прямым и кода логических условий буферного ре- инверсным управляющими входами второ-г

f гистра соединен с управляющим входом мультиплексора логических условий, выход поля модифицируемого разряда адреса буферного регистра соединен с первым ин-40 блока контроля соединен с первым вхо- формационным входом мультиплексора ло- дом первого элемента ИЛИ, выход ко- гических условий, выход поля немодифици- руемых разрядов адреса буферного регис.тра соединен с входом немодифицируемых

i разрядов адреса второго информацион- 45 ратора, выход которого соединен с ного входа первого коммутатора адре- первым входом второго элемента ИЛИ,

ля, выход поля признака четности буферного регистра соединен с входом признака четкости первого блока контроля, выход признака ошибки первого

го коммутатора адреса и инверсными входами третьего и четвертого элементов И, выход признака отказа первого

торого соединен с единичным входом триггера отказа, прямой выход которого соединен с входом запуска одновибса, выход мультиплексора логических условий соединен с входом модифицируемого разряда адреса второго информационного входа первого коммутатора адреса, вход логических условий устройства соединен с вторым информационным входом мультиплексора логических условий, второй выход генератора тактовых импульсов соединен с прямым входом второго элемента И, выход которого соединен с синхронизирующим входом буферного регистра, третий выw

5

5 20

I90298

ход генератора тактовых импульсов соединен с прямьп входом третьего элемента И, выход которого соединен с синхронизирующим входом второго регистра адреса, выходы полей которого соединен с адресными входами соответствующих блоков памяти нанокоманд группы, четвертый выход генератора тактовых импульсов соединен с прямым входом четвертого элемента И, выход которого соединен с синхронизирующим входом регистра нанокоманд, выход первого коммутатора адреса соединен с первым информационным входом второго коммутатора адреса и входом блока элементов НЕ, выход которого соединен с вторым информационным.входом второго коммутатора адреса, выход которого соединен с информационным входом первого регистра адреса, выход поля адреса нанокоманды буферного регистра соединен с первым информационным входом третьего коммутатора адреса, выход которого соединен.с информационным входом второго регистра адреса, выходы поля кода логических условий, поля немодифицируемых разрядов адреса, поля адреса нанокоманды буферного регистра соединены с информа- 30 ционным входом первого блока контро25

35 блока контроля соединен с прямым и инверсным управляющими входами второ-г

блока контроля соединен с прямым и инверсным управляющими входами второ-г

ля, выход поля признака четности буферного регистра соединен с входом признака четкости первого блока контроля, выход признака ошибки первого

блока контроля соединен с первым вхо- дом первого элемента ИЛИ, выход ко-

го коммутатора адреса и инверсными входами третьего и четвертого элементов И, выход признака отказа первого

блока контроля соединен с первым вхо- дом первого элемента ИЛИ, выход ко-

торого соединен с единичным входом триггера отказа, прямой выход которого соединен с входом запуска одновибвыход которого соединен с нулевым входом триггера запуска, выход информационного поля регистра нанокоманд

50 соединен с информационным входом блока элементов И и информационным входом второго блока контроля, выход поля признака четности регистра нанокоманд соединен с входом признака

55 четности второго блока контроля, выход признака ошибки которого соединен с инверсным управляющим входом блока элементов И,инверсными входами первого и второго элементов И, инверсным и прямым управляющими входами третьего коммутатора адреса, выход признака отказа второго блока контроля соединен с вторым входом первого элемента ИЛИ, выход признака окончания работы блока элементов И соединен с вторым входом второго элемента ИЛИ, прямым и инверсным управляющими входами первого коммутатора адреса, операционные выходы блока элементов И соединены с информационными выходами устройства, отличающееся тем, что, с целью повьппения откаэоустойчивости, дополнительно содержит блок формирования адреса и блок коммутации, причем выход поля адреса на- нокоманды буферного регистра соединен с информационным входом блока формирования адреса, выход которого соединен с вторым информационным входом третьего коммутатора и управляющим входом блока коммутации, выходы блоков памяти нанокоманд группы соединены с соответствующими информационными входами блока коммутации, выходы блока коммутации соединены с информационными входами соответствующих разрядов регистра нанокьманд, выход кода настройки второго блока контроля соединен с управляющим входом блока формирования адреса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммный процессор | 1986 |

|

SU1365091A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1277105A1 |

| Адаптивный модуль микропрограммного устройства управления | 1984 |

|

SU1273926A1 |

| Нанопрограммное устройство управления | 1983 |

|

SU1136160A1 |

| Устройство для программного регулирования | 1988 |

|

SU1571550A1 |

| Устройство для программного управления процессами | 1986 |

|

SU1328795A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1310818A1 |

| Устройство для обмена данными в распределенной вычислительной системе | 1988 |

|

SU1580382A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1179338A1 |

Микропрограммное устройство управления относится к вычислительной технике и может быть использовано при построении отказоустойчивых микропрограммных процессоров программируемых контроллеров, вычислительных и управляющих систем с микропрограммным управлением. Цель изобретения - повышение отказоустойчивости устройства. Микропрограммное устройство управления содержит блок памяти 1 микS (Л 00 со со Риз.1

40

Г

- -у

42

Фл/а.З

.

47/

«e

ff7.2

iun

4

e

А/г5

«

2,6

Редактор О. Бугир

Составитель Д. Ванюхин

Техред М.Ходанич Корректор Г. Решетник

Заказ 2513/43 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Микропрограммное устройство управления | 1983 |

|

SU1103231A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1277105A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-06-23—Публикация

1985-06-26—Подача