11297052

Изобретение относится к вычислительной технике и может быть использовано для контроля цифровых уст- . ройств.

Целью изобретения является повышение достоверности контроля сигнатурного анализатора.

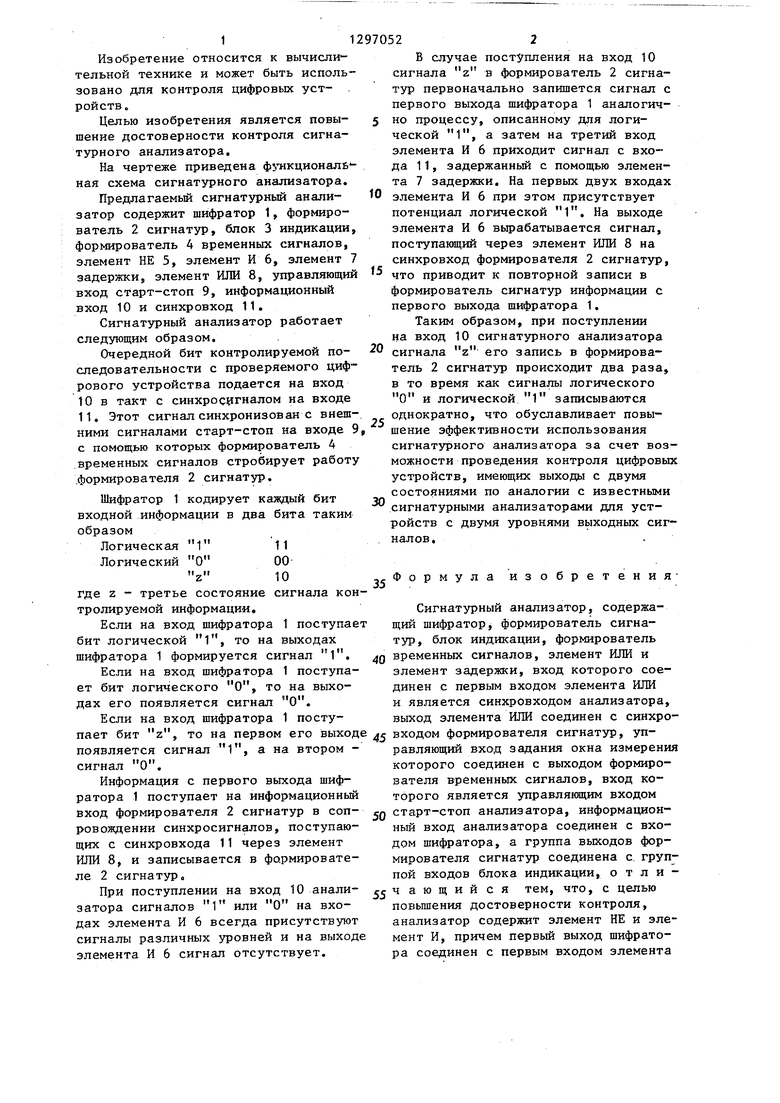

На чертеже приведена ф икцноналб - ная схема сигнатурного анализатора.

Предлагаемый сигнатурный анализатор содержит шифратор 1, формирователь 2 сигнатур, блок 3 индикации, формирователь 4 временных сигналов, элемент НЕ 5, элемент И 6, элемент 7

10

В случае поступления на вход 1 сигнала z в формирователь 2 сиг тур первонача.пьно запишется сигнал первого выхода шифратора 1 аналог но процессу, описанному для логической 1, а затем на третий вхо элемента И 6 приходит сигнал с вх да 1 1 , задержанньй с помощью элем та 7 задержки. На первых двух вхо элемента И 6 при этом присутствуе потенциал логической 1. На выхо элемента И 6 вырабатывается сигнал поступающий через элемент ИЛИ 8 н синхровход формирователя 2 сигнату

20

25

задержки, элемент ИЛИ 8, управляющий 5 приводит к повторной записи в вход старт-стоп 9, информационный вход 10 и синхровход 11.

Сигнатурный анализатор работает следующим образом. .

Очередной бит контролируемой последовательности с проверяемого цифрового устройства подается на вход 10 в такт с синхросигналом на входе 11. Этот сигнал синхронизован с внешними сигналами старт-стоп на входе 9, с помощью которых формирователь 4 временных сигналов стробирует работу .формирователя 2 сигнатур.

Шифратор 1 кодирует каждый бит входной информации в два бита таким образом

Логическая 1 11

Логический О 00 г 10

где Z - третье состояние сигнала контролируемой информации.

Если на вход шифратора 1 поступает бит логической 1, то на выходах шифратора 1 формируется сигнал 1.

Если на вход шифратора 1 поступает бит логического О, дах его появляется сигнал О

Если на вход шифратора 1 посту30

35

формирователь сигнатур информации первого выхода шифратора 1.

Таким образом, при поступлении на вход 10 сигнатурного анализатор сигнала z его запись в формирова тель 2 сигнатур происходит два раз в то время как сигналы логического О и логической 1 записываются однократно, что обуславливает повы шение эффектшзности использования сигнатурного анализатора за счет в можности проведения контроля ЦИфрО устройств, имеющих выходы с двумя состояниями по аналогии с известны сигнатурными анализаторами для уст ройств с двумя уровнями выходных с налов.

Формула изобретени

то на выхоип

Сигнатурный анализатор, содержа щий шифратор, формирователь сигнатур, блок индикации, формирователь 40 временных сигналов, элемент ШШ и элемент задержки, вход которого со динен с первым входом элемента ИЛИ и является синхровходом анализатор выход элемента ИЛИ соединен с синх

пает бит z, то на первом его выходе входом формирователя сигнатур, , а на втором появляется сигнал О.

сигнал

Информация с первого выхода шифратора 1 поступает на информационный

равляющий вход задания окна измерен которого соединен с выходом формиро вателя временных сигналов, вход которого является управляющим входом

вход формирователя 2 сигнатур в соп- Q старт-стоп анализатора, информационровождении синхросигналов, поступающих с синхровхода 11 через элемент ИЛИ 8, и записывается в формирователе 2 сигнатур.

При поступлении на вход 10 анализатора сигналов 1 или О на входах элемента И 6 всегда присутствуют сигналы различных уровней и на выходе элемента И 6 сигнал отсутствует.

В случае поступления на вход 10 сигнала z в формирователь 2 сигнатур первонача.пьно запишется сигнал с первого выхода шифратора 1 аналогично процессу, описанному для логической 1, а затем на третий вход элемента И 6 приходит сигнал с входа 1 1 , задержанньй с помощью элемента 7 задержки. На первых двух входах элемента И 6 при этом присутствует потенциал логической 1. На выходе элемента И 6 вырабатывается сигнал, поступающий через элемент ИЛИ 8 на синхровход формирователя 2 сигнатур.

приводит к повторной записи в

20

25

5 приводит к повторной записи в

30

35

формирователь сигнатур информации с первого выхода шифратора 1.

Таким образом, при поступлении на вход 10 сигнатурного анализатора сигнала z его запись в формирователь 2 сигнатур происходит два раза, в то время как сигналы логического О и логической 1 записываются однократно, что обуславливает повышение эффектшзности использования сигнатурного анализатора за счет возможности проведения контроля ЦИфрОВЕЛХ устройств, имеющих выходы с двумя состояниями по аналогии с известными сигнатурными анализаторами для устройств с двумя уровнями выходных сигналов.

Формула изобретенияСигнатурный анализатор, содержащий шифратор, формирователь сигнатур, блок индикации, формирователь 40 временных сигналов, элемент ШШ и элемент задержки, вход которого соединен с первым входом элемента ИЛИ и является синхровходом анализатора, выход элемента ИЛИ соединен с синхроравляющий вход задания окна измерения которого соединен с выходом формирователя временных сигналов, вход которого является управляющим входом

5

ный вход анализатора соединен с входом шифратора, а группа выходов формирователя сигнатур соединена с. группой входов блока индикации, отличающийся тем, что, с целью повышения достоверности контроля, анализатор содержит элемент НЕ и элемент И, причем первьй выход шифратора соединен с первым входом элемента

312970524

И и информационным входом формирова- элемента И, третий вход которого сое- теля сигнатур, второй выход шифратора динен с выходом элемента задержки, соединен с входом элемента НЕ, выход выход элемента И соединен с вторым которого соединен с вторым входом входом элемента ИЛИ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнатурный анализатор | 1982 |

|

SU1108452A1 |

| Сигнатурный анализатор | 1986 |

|

SU1361555A1 |

| Сигнатурный анализатор | 1987 |

|

SU1434437A1 |

| Сигнатурный анализатор | 1984 |

|

SU1223231A1 |

| Сигнатурный анализатор | 1980 |

|

SU903898A1 |

| Сигнатурный анализатор | 1984 |

|

SU1354194A1 |

| Сигнатурный анализатор | 1985 |

|

SU1298771A2 |

| Сигнатурный анализатор | 1986 |

|

SU1456958A1 |

| Сигнатурный анализатор | 1982 |

|

SU1065857A1 |

| Сигнатурный анализатор | 1986 |

|

SU1343413A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля цифровых устройств. Целью изобретения является повьппение достоверности контроля сигнатурного анализатора. Сигнатурный анализатор содержит шифратор 1, формирователь 2 сигнатур, блок 3 индикации, формирователь 4 временных сигналов, элемент НЕ 5, элемент И 6, элемент 7 задержки, элемент ИЛИ 8, Сущность функционирования сигнатурного анализатора состоит в том, что при поступлении на его информационный вход сигналов с уровнями логического О и логической 1 он работает как обычный сигнатурный анализатор, а при поступлении сигнала с уровнем z осуществляет удвоенную запись информации за счет удвоения соответствующего синхросигнала. 1 ип. S (Л

| Патент США | |||

| ГАЙКА | 0 |

|

SU397686A1 |

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Сигнатурный анализатор | 1980 |

|

SU903898A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-03-15—Публикация

1985-10-23—Подача