(Л

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнатурный анализатор | 1987 |

|

SU1434437A1 |

| Сигнатурный анализатор | 1985 |

|

SU1277113A1 |

| Сигнатурный анализатор | 1985 |

|

SU1297052A1 |

| Сигнатурный анализатор | 1982 |

|

SU1108452A1 |

| Сигнатурный анализатор | 1984 |

|

SU1354194A1 |

| Сигнатурный анализатор | 1985 |

|

SU1280635A1 |

| Сигнатурный анализатор | 1984 |

|

SU1223231A1 |

| Сигнатурный анализатор | 1984 |

|

SU1238074A1 |

| Сигнатурный анализатор | 1987 |

|

SU1589278A1 |

| Сигнатурный анализатор | 1986 |

|

SU1361555A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля дискретных объектов. Упрощение устройства достигнуто за счет упрощения структуры шифратора, осзтцествляющего кодирование каждого бита входной информации. Устройство содержит шифратор I, формирователь 2 временных сигналов, первый формирователь 3 сигнатур, первый блок 4 индикации, второй формирователь 5 сигнатур, второй блок 6 индикации, вход 7 Старт-стоп, информационный вход 8 и синхровход 9. Шифратор содержит два компаратора. 2 ил., 1 табл.

;л

эо

11456958

Изобретение относится к вычисли™ тельной технике и может быть использовано для контроля дискретных объектов.

Целью изобретения является упрощение конс:; рукции.

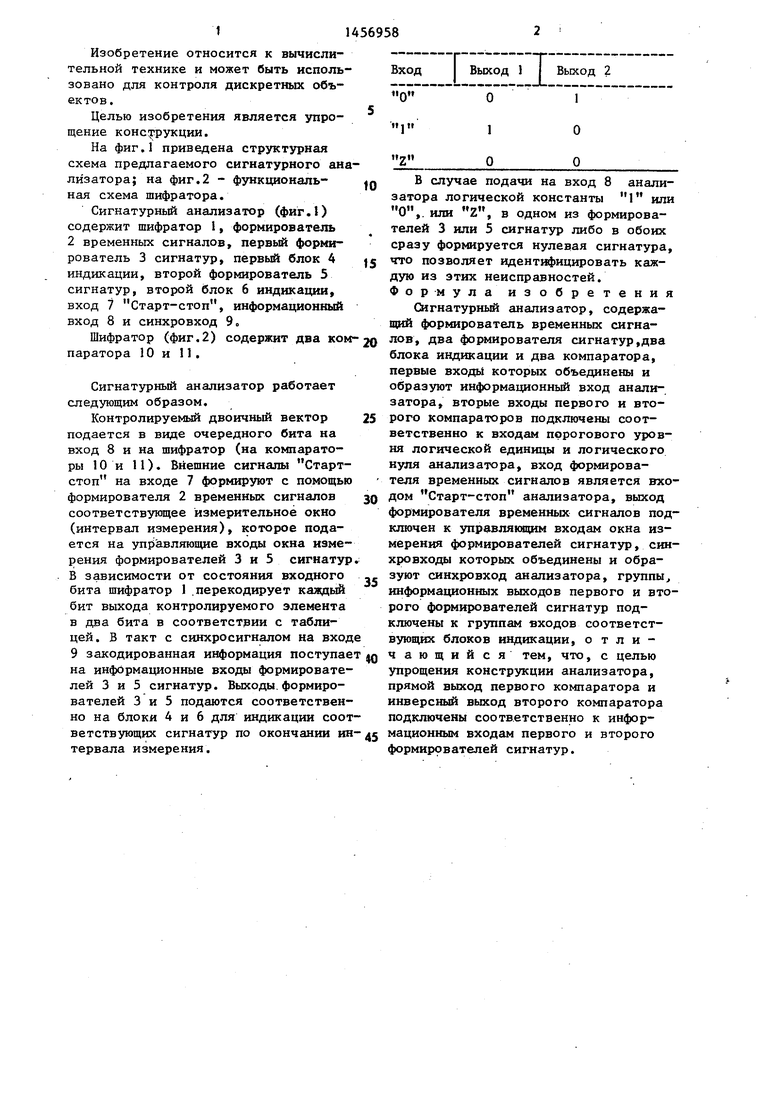

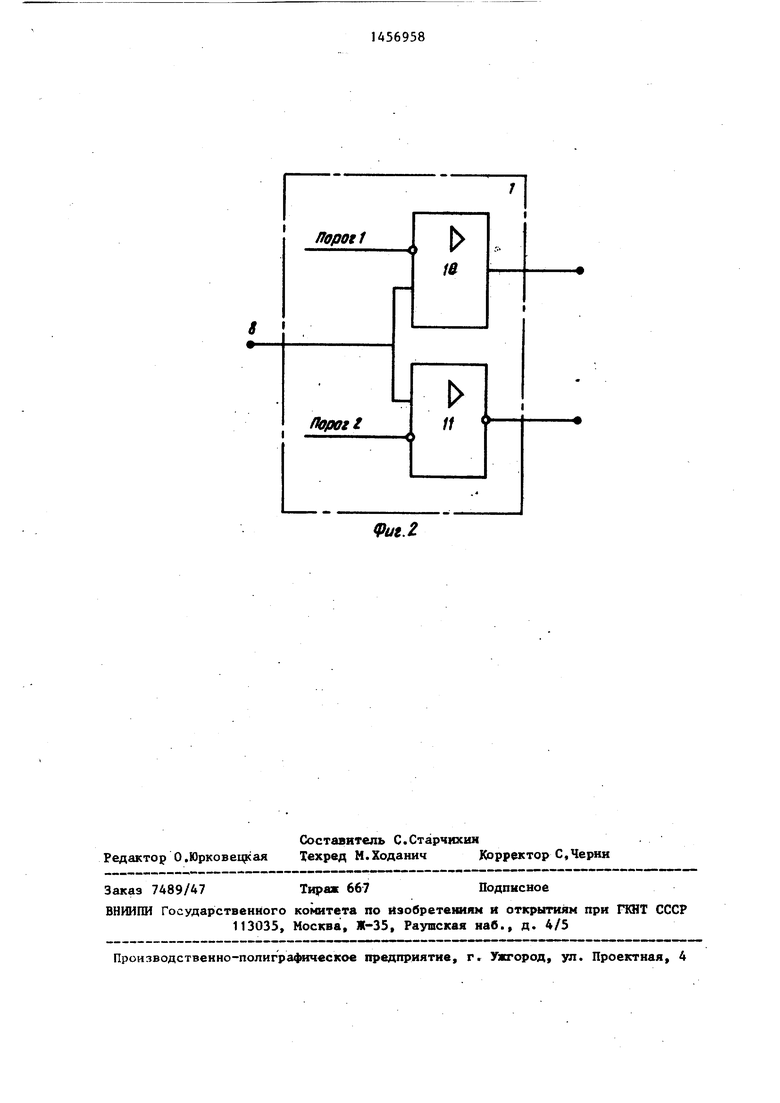

На фиг.1 приведена структурная схема предлагаемого сигнатурного анализатора; на фиг.2 - функциональная схема шифратора.

Сигнатурньй анализатор (фиг.1) содержит шифратор 1, формирователь 2 временньге сигналов, первый формирователь 3 сигнатур, первый блок 4 индикации, второй формирователь 5 сигнатур, второй блок 6 индикации, вход 7 Старт-стоп, информационный вход 8 и синхровход 9 о

Вход

IIQU

I Выход 1 I

Выход 2 1

HI «I

1(1711

1

О

О

10

анали- 1 или

fS

В случае подачи на вход 8 затора логической константы О,, или Z, в одном из формирователей 3 или 5 сигнатур либо в обоих сразу формируется нулевая сигнатура, что позволяет идентифицировать каждую из этих неисправностей. Формула изобретения

Сигнатурный анализатор, содержащий формирователь временных сигна- Шифратор (фиг.2) содержит два ком-20 лов, два формирователя сигнатур,два

паратора 10 и П

Сигнатурный анализатор работает следующим образом.

Контролируемый двоичный вектор подается в виде очередного бита на вход 8 и на шифратор (на компараторы 10 и 11). Внешние сигналы Старт- стоп на входе 7 формируют с помощью формирователя 2 временных сигналов соответствующее измерительное окно (интервал измерения), которое подается на управляющие входы окна измерения формирователей 3 и 5 сигнатур. В зависимости от состояния входного бита шифратор 1 .перекодирует каяздыЙ бит выхода контролируемого элемента в два бита в соответстрии с таблицей. В такт с синхросигналом на входе

25

блока индикации и два компаратора, первые входы которых объединены и образуют информационный вход анализатора, вторые входы первого и второго компараторов подключены соответственно к входам порогового уровня логической единицы и логического нуля анализатора, вход формирова- теля временных сигналов является вхо 30 дом Старт-стоп анализатора, выход формирователя временных сигналов под ключен к управлякяцим входам окна измерения формирователей сигнатур, син хровходы которых объединены и образуют синхровход анализатора, группыj информационных выходов первого и вто рого формирователей сигнатур подключены к группам входов соответствующих блоков индикации, о т л и 35

9 закодированная информация поступает Q чающийся тем, что, с целью

на информационные входы формирователей 3 и 5 сигнатур. Выходы.формирователей 3 и 5 подаются соответственно на блоки 4 и 6 для индикации соответствующих сигнатур по окончании ин- j мационным входам первого и второго тервапа измерения.формирователей сигнатур.

упрощения конструкции анализатора, прямой выход первого компаратора и инверсный выход второго компаратора подключены соответственно к инфор

I Выход 1 I

Выход 2 1

HI «I

1(1711

О

О

анали- 1 или

В случае подачи на вход 8 затора логической константы О,, или Z, в одном из формирователей 3 или 5 сигнатур либо в обоих сразу формируется нулевая сигнатура, что позволяет идентифицировать каждую из этих неисправностей. Формула изобретения

Сигнатурный анализатор, содержа5

блока индикации и два компаратора, первые входы которых объединены и образуют информационный вход анализатора, вторые входы первого и второго компараторов подключены соответственно к входам порогового уровня логической единицы и логического нуля анализатора, вход формирова- теля временных сигналов является вхо- 0 дом Старт-стоп анализатора, выход формирователя временных сигналов подключен к управлякяцим входам окна измерения формирователей сигнатур, син- хровходы которых объединены и образуют синхровход анализатора, группыj информационных выходов первого и второго формирователей сигнатур подключены к группам входов соответствующих блоков индикации, о т л и 5

мационным входам первого и второго формирователей сигнатур.

упрощения конструкции анализатора, прямой выход первого компаратора и инверсный выход второго компаратора подключены соответственно к инфорГ

8

-

Составитель С.Старчихин Редактор О.Юрковец сая Техред М.Ходанич Корректор С,Черни

Заказ 7489/47

Тираж 667

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Put.Z

Подписное

| Клапан к вакуум-протезу бедра | 1947 |

|

SU71796A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Сигнатурный анализатор | 1982 |

|

SU1108452A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-02-07—Публикация

1986-06-16—Подача