Изобретение относится к вычислительной технике, а именно к запомина кмцим устройствам, и может быть испол зовано при изготовлении и испытании оперативных запоминающих блоков. Известно устройство для контроля оперативных запоминающих блоков, содержащее счётчик адреса, соединенный с адресными входами накопителя, регистры числа, подключенные к числовым входам накопителя, логические схемы, элементы задержки, схемы фиксации ошибки, регистры управления и контроля и одноразрядный счетчик, вы ход счетчика младших разрядов адреса через элемент задержки подключен ко входу регистра управления, другой вход которого соединен через первую схему совпадения с выходом накопителя, а выход регистра управления подключен ко входу второй схемы совпаде ния, другой вход которой соединен с выходом счетчика младших разрядов адреса, а выход подключен ко входу регистра числа через сборку и непосредственно ко входу счетчика старших рязрядов адреса, выход которого соединен со входом одноразрядного счетчика , выходы которого подключены соответственно ко входу первой схемы совпадения и ко входу регистра контроля т. Известное устройство не обеспечивает эффективного контроля оперативных запоминающих блоков по всему набору контролирующих тестов, а также не позволяет использовать его в составе автоматизированной системы с малой ЦВМ. Известное также устройство для контроля оперативных запоминающих блоков, содержащее первый счетчик, регистр числа и блок управления, подключенные к выходным шинам устройства, основные коммутаторы, выходы которых .соединены с входами регистра числа, второй счетчик, третий счетчик формирователь, счетный триггер.

полусумматор, дополнительные коммутаторы и элемент И, инверсный вход которого подключен к выходу формирователя, прямой вход и вход третьего счетчика - к выходу блока управления, а выход к одной из выходных шин устройства и входу первого счетчика, выход которого через счетный триггер соединен с входом формирователя, выходы третьего счетчика и счетного триггера подключены к входам полусумматора, выход которого соединен с одним из выходов основных коммутаторов, другие входы которых подключены к соответствующим выходам дополнитель ных коммутаторов, информационные которых подключены к выходам третьего счетчика, а управляющие входы - к выходам второго счетчика, вход которого соединен с выходом счетного триггера .

Недостатком этого устройства является то, что оно не позволяет использовать его в составе автоматизированной контролирующей системы с малой ЦВМ и не обеспечивает достоверности контроля оперативных запоминающих блоков по всему набору контролирующих тестов,

Наиболееблизким по технической .сущности к предлагаемому является контролирующая система с программным управлением, содержащая многопрограммный блок, устройство адресации, генёратор контрольных данных проверяе мый накопитель, выходной накопитель данных, блок сравнения, адресный регистр, регистр контрольных данных, регистр выходных данных, схему для блокировки перезаписи из устройства адресации в адресный регистр, из генератора контрольных данных в регистр контрольных данных и из выходного накопителя данных в регистр выходных данных t ЗЗНедостатком данного устройства является невозможность использовать малую ЦВМ, что снижает общее быстродействие системы и не обеспечивает достоверности контроля оперативных запоминающих блоков по всему набору контролирующих тестов.

Цель изобретения - увеличение быстродействия устройства и повышени достоверности контроля оперативных запоминающих блоков.

Поставленная цель достигается тем что в устройство для контроля оперативных запоминающих блоков, содержащее первый информационный регистр, входы которого подключены к выходам первого коммутатора, первый выход к первому входу второго коммутатора,

а второй выход - к первому входу блока сравнения, второй информационный регистр, первый вход которого подключен ко второму входу второго коммутатора, второй выход - к первому

входу третьего коммутатора, третий выход второго информационного регистра подключен ко второму входу блока сравнения, первый выход которого подключен к третьему входу второго комs мутатора, второй выход блока сравнения подключен к первому входу блока управления, блок регистров, первый выход которого подключен ко входу третьего коммутатора, а второй выход блока,регистров подключен к первому вхо,ду первого коммутатора, второй вход (которого подключен к первому выходу

блока управления; регистр адреса, первый вход которого подключен ко второму выходу блока управления, а выход - к четвертому входу второго коммутатора, дешифратор, первый вход которого подключен ко второму входу блока управления, а второй выход к пятому входу второго коммутатора, блок синхронизации, выходы которого подключены к третьим входам блока управления, третьи входы блока управления подключены ко вторым входам третьего коммутатора, дополнительно введены первый накопитель, первый выход которого подключен ко входу блока регистров, а второй выход - ко второму входу регистра адреса-, счетчик адреса , первый вход которого подключен к третьему выходу дешифратора, вторые входы - к четвертым входам блока управления, а первый выход - к первому входу первого накопителя и второй выход - к шестому входу второго коммутатора, четвертый коммутатор, входы которого подключены к четвертым выходам дешифратора, а выходы - ко вторым входам первого накопителя, второй накопитель, первый вход которого подключен к третьему выходу счетчика адреса, а выходы - ко входам второго информационного регистра, и пятый коммутатор, входы которого подключены к пятым выходам дешифратора, а выходы 5 ко входам второго накопителя.

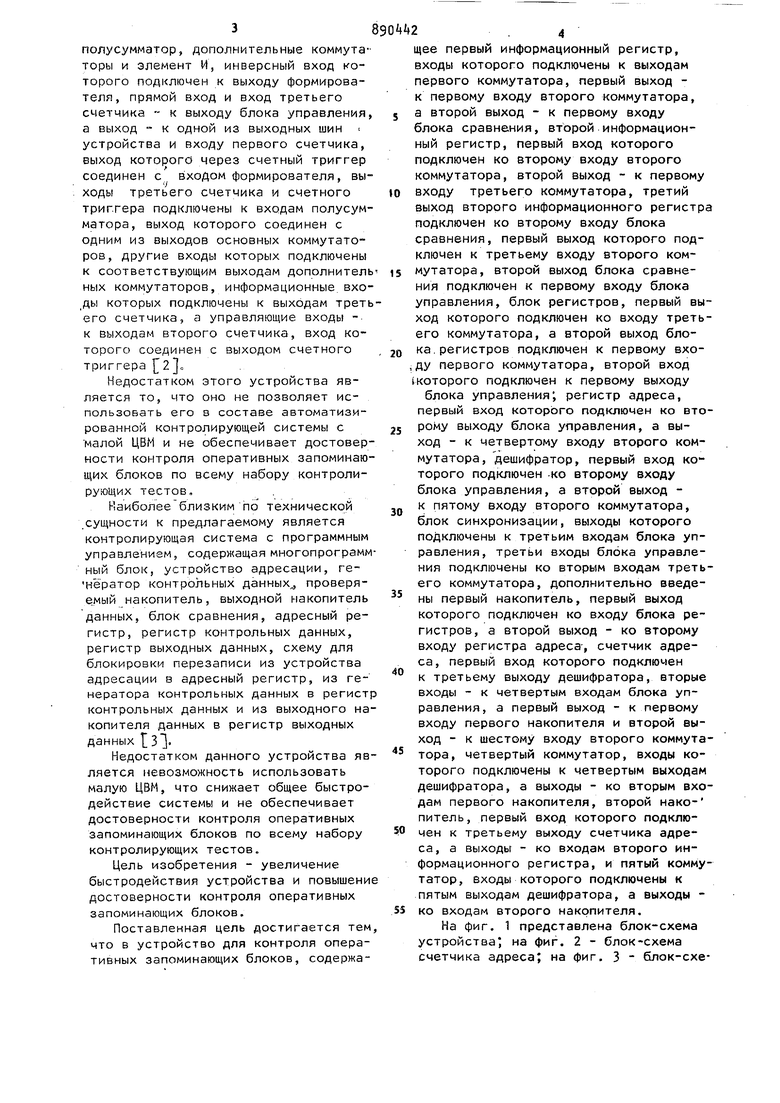

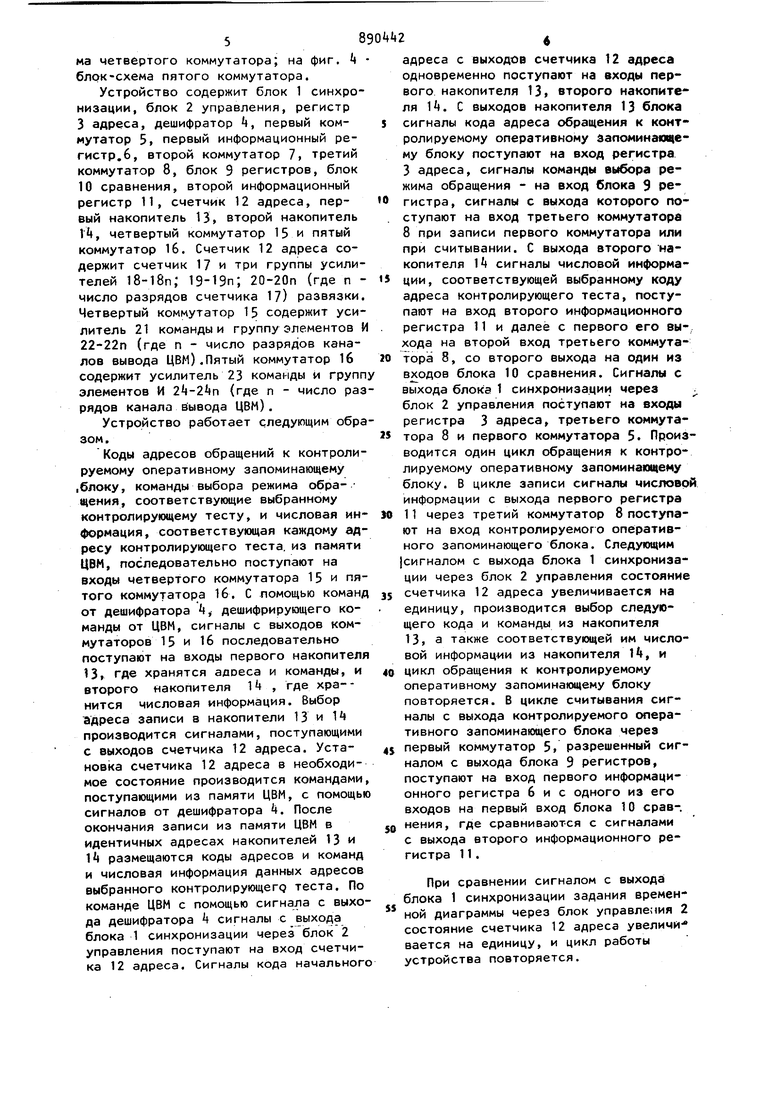

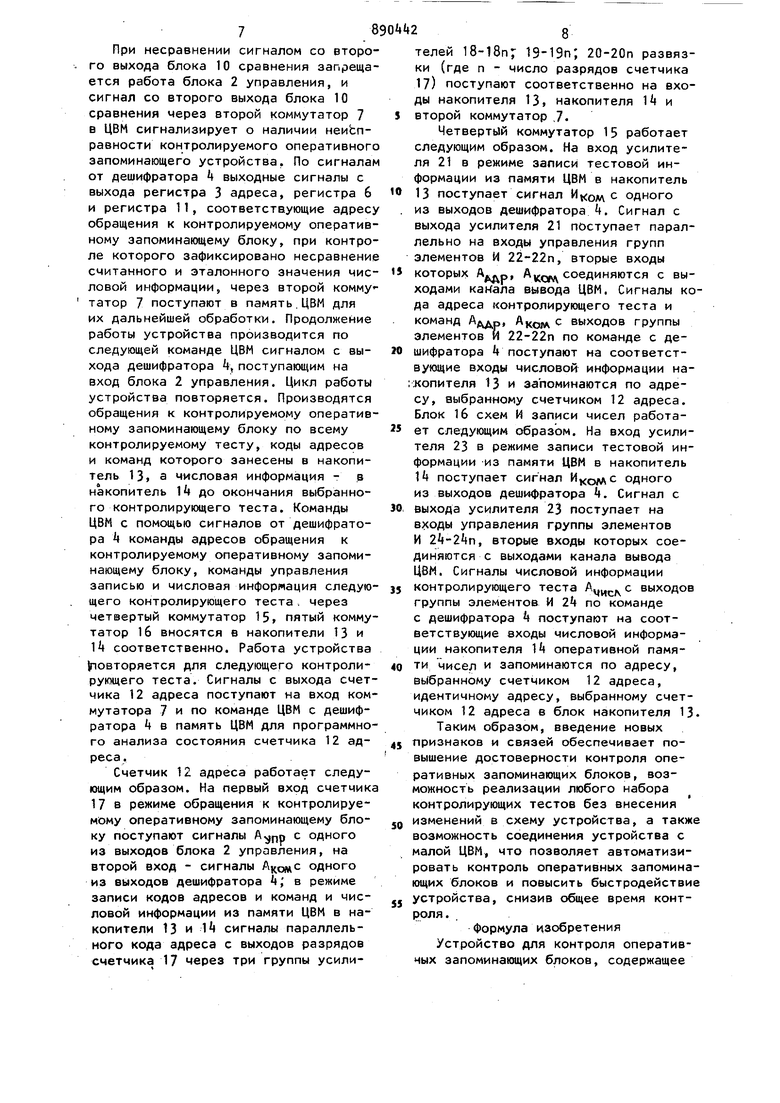

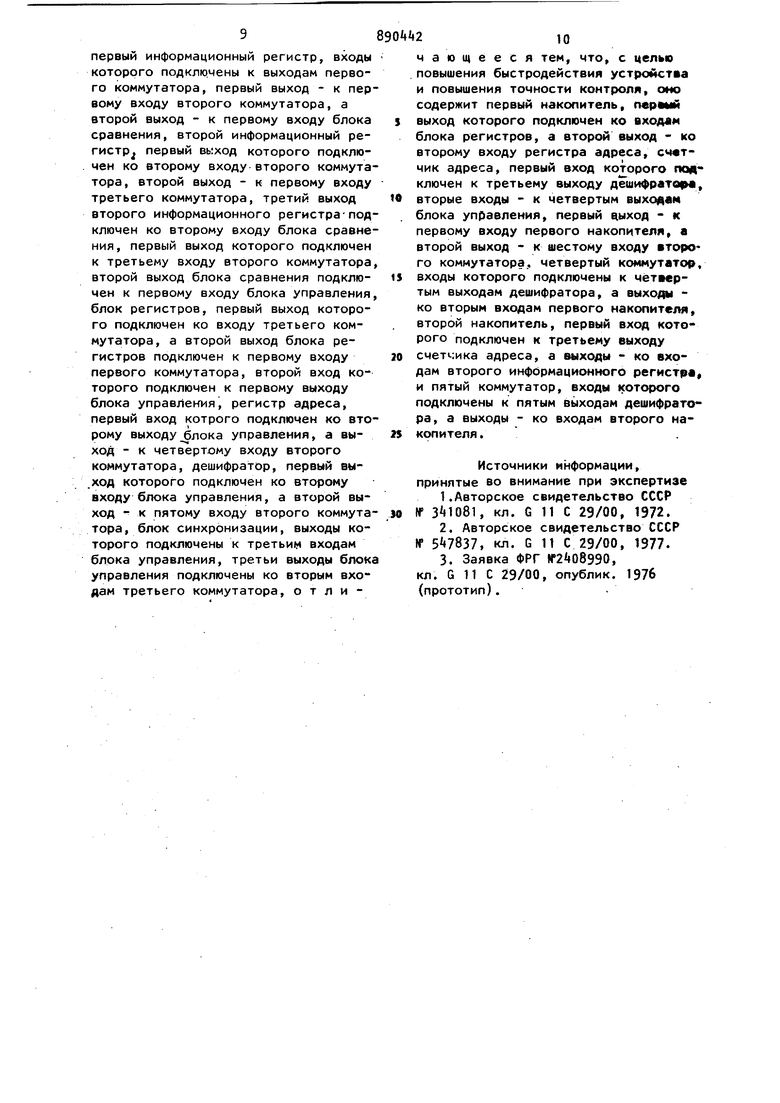

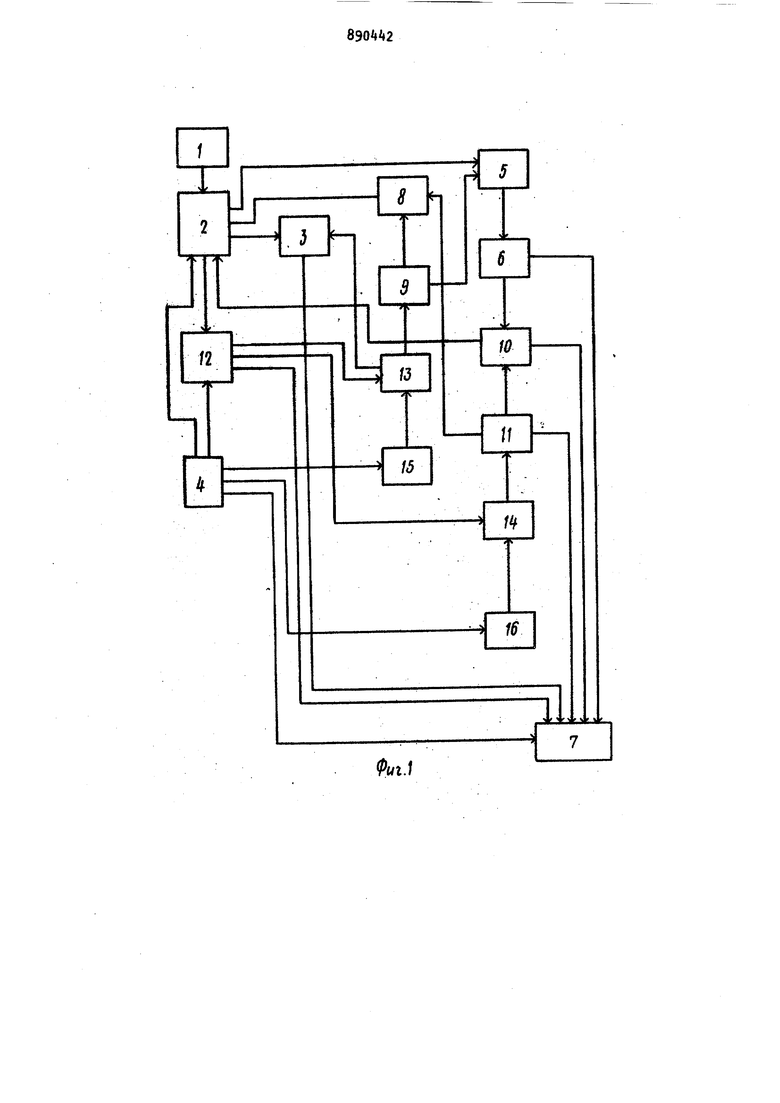

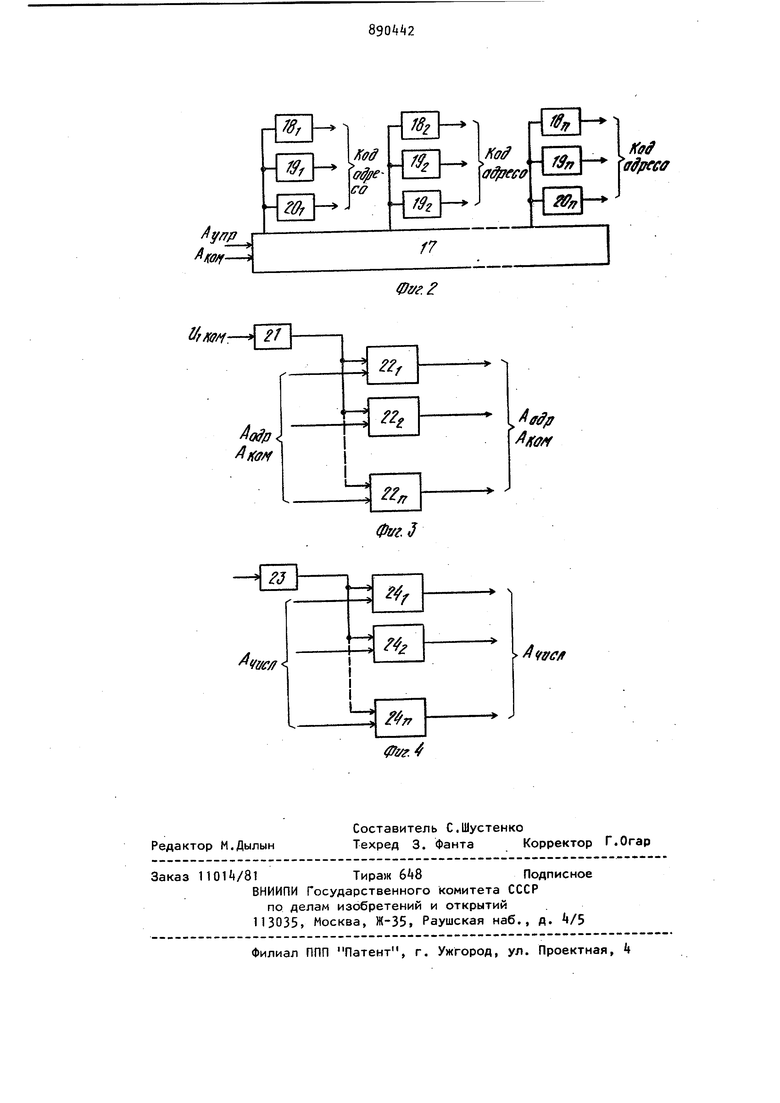

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - блок-схема счетчика адреса; на фиг. 3 - блок-схе58ма четвёртого коммутатора; на фиг, k блок-схема пятого коммутатора. Устройство содержит блок 1 синхронизации, блок 2 управления, регистр 3 адреса, дешифратор 4, первый коммутатор 5, первый информационный регистр.6, второй коммутатор 7, третий коммутатор 8, блок 9 регистров, блок 10 сравнения, второй информационный регистр 11, счетчик 12 адреса, первый накопитель 13, второй накопитель I, четвертый коммутатор 15 и пятый коммутатор 16. Счетчик 12 адреса содержит счетчик 17 и три группы усилителей l8-l8n; 19-19п; 20-20п (где п число разрядов счетчика 17) развязки. Четвертый коммутатор 15 содержит усилитель 21 команды и группу элементов И 22-22п (где п - число разрядов каналов вывода ЦВМ).Пятый коммутатор 16 содержит усилитель 23 команды и групп элементов И (где п - число раз рядов канала вывода ЦВМ). Устройство работает следующим обра зом. Коды адресов обращений к контролируемому оперативному запоминающему .блоку, команды выбора режима обра- щения, соответствующие выбранному контролирующему тесту, и числовая информация, соответствующая каждому адресу контролирующего теста, из памяти ЦВМ, последовательно поступают на входы четвертого коммутатора 15 и пятого коммутатора 16. С помощью команд от дешифратора , дешифрирующего команды от ЦВМ, сигналы с выходов коммутаторов 15 и 16 последовательно поступают на входы первого накопителя 13, где хранятся адреса и команды, и второго накопителя 1 , где хра- нится числовая информация. Выбор Адреса записи в накопители 13 и 1й производится сигналами, поступающими с выходов счетчика 12 адреса. Установка счетчика 12 адреса в необходимое состояние производится командами поступающими из памяти ЦВМ, с помощью сигналов от дешифратора 4. После окончания записи из памяти ЦВМ в идентичных адресах накопителей 13 и I размещаются коды адресов и команд и числовая информация данных адресов выбранного контролирующегр теста. По команде ЦВМ с помощью сигнала с выхода дешифратора k сигналы с выхода блока 1 синхронизации через блок 2 управления поступают на вход счетчика 12 адреса. Сигналы кода начального 2 адреса с выходов счетчика 12 адреса одновременно поступают на входы первого накопителя 13, второго накопителя 1. С выходов накопителя 13 блока сигналы кода адреса обращения к контролируемому оперативному запоминающему блоку поступают на вход регистра 3 адреса, сигналы команды выбора режима обращения - на вход блока S регистра, сигналы с выхода которого поступают на вход третьего коммутатора 8 при записи первого коммутатора или при считывании. С выхода второго накопителя 1 сигналы числовой информации, соответствующей выбранному коду адреса контролирующего теста, поступают на вход второго информационного регистра 11 и далее с первого его выхода на второй вход третьего коммутатора 8, со второго выхода на один из входов блока 10 сравнения. Сигналы с выхода блока 1 синхронизации через блок 2 управления поступают на входы регистра 3 адреса, третьего коммутатора 8 и первого коммутатора 5. Производится один цикл обращения к контролируемому оперативному запоминающему блоку. В цикле записи сигналы числовой информации с выхода первого регистра 11 через третий коммутатор 8 поступают на вход контролируемого оперативного запоминающего блока. Следующим сигналом с выхода блока 1 синхронизации через блок 2 управления состояние счетчика 12 адреса увеличивается на единицу, производится выбор следующего кода и команды из накопителя 13, а также соответствующей им числовой информации из накопителя Н, и цикл обращения к контролируемому оперативному запоминающему блоку повторяется. В цикле считывания си|- налы с выхода контролируемого оперативного запоминающего блока через первый коммутатор 5, разрешенный сигналом с выхода блока 9 регистров, поступают на вход первого информационного регистра бис одного из его входов на первый вход блока 10 срав-. нения, где сравниваются с сигналами с выхода второго информационного регистра 11 . При сравнении сигналом с выхода блока 1 синхронизации задания временной диаграммы через блок управления 2 состояние счетчика 12 адреса увеличи вается на единицу, и цикл работы устройства повторяется.

При несравнении сигналом со второго выхода блока 10 сравнения запрещается работа блока 2 управления, и сигнал со второго выхода блока 10 сравнения через второй коммутатор 7 в ЦВМ сигнализирует о наличии неиЬправности контролируемого оперативного запоминающего устройства. По сигналам от дешифратора выходные сигналы с выхода регистра 3 адреса, регистра 6 и регистра 11, соответствующие адресу обращения к контролируемому оперативному запоминащему блоку, при контроле которого зафиксировано несравнение считанного и эталонного значения числовой информации, через второй коммутатор 7 поступают в память.ЦВМ для их дальнейшей обработки. Продолжение работы устройства производится по следующей команде ЦВМ сигналом с выхода дешифратора 4, поступающим на вход блока 2 управления. Цикл работы устройства повторяется. Производятся обращения к контролируемому оперативному запоминающему блоку по всему контролируемому тесту, коды адресов и команд которого занесены в накопитель 13, а числовая информация - в накопитель 1k до окончания выбранного контролирующего теста. Команды ЦВМ с помощью сигналов от дешифратора k команды адресов обращения к контролируемому оперативному запоминающему блоку, команды управления записью и числовая информация следующего контролирующего теста . через четвертый коммутатор 15, пятый коммутатор 16 вносятся в накопители 13 и 1 соответственно. Работа устройства |повторяется для следующего контролирующего теста. Сигналы с выхода счетчика 12 адреса поступают на вход коммутатора 7 и по команде ЦВМ с дешифратора k в память ЦВМ для программного анализа состояния счетчика 12 адреса.

Счетчик 12 адреса работает следующим образом. На первый вход счетчика 17 в режиме обращения к контролируемому оперативному запоминающему блоку поступают сигналы с одного из выходов блока 2 управления, на второй вход - сигналы Ajjo«c одного из выходов дешифратора k, в режиме записи кодов адресов и команд и числовой информации из памяти ЦВМ в накопители 13 и Т сигналы параллельного кода адреса с выходов разрядов счетчика 17 через три группы усилителей 18-18п; 19-19п; 20-20п развязки (где п - число разрядов счетчика 17) поступают соответственно на входы накопителя 13, накопителя 1А и второй коммутатор .7.

Четвертый коммутатор 15 работает следующим образом. На вход усилителя 21 в режиме записи тестовой информации из памяти ЦВМ в накопитель 13 поступает сигнал Иком с одного . из выходов дешифратора k. Сигнал с выхода усилителя 21 поступает параллельно на входы управления групп элементов И 22-22п, вторые входы

которых Аддр, АjjQp соединяются с выходами канала вывода ЦВМ. Сигналы кода адреса контролирующего теста и команд Аддр, Ajtoj с выходов группы элементов И 22-22п по команде с дешифратора поступают на соответствующие входы числовой информации накопителя 13 и запоминаются по адресу, выбранному счетчиком 12 адреса. Блок 16 схем И записи чисел работает следующим образом. На вход усилителя 23 в режиме записи тестовой информации -из памяти ЦВМ в накопитель Н поступает сигнал одного из выходов дешифратора 4. Сигнал с выхода усилителя 23 поступает на входы управления группы элементов И 24-2in, вторые входы которых соединяются с выходами канала вывода ЦВМ, Сигналы числовой информации

контролирующего теста А, с выходов группы элементов И 2 по команде с дешифратора поступают на соответствующие входы числовой информации накопителя Н оперативной памяти чисел и запоминаются по адресу, выбранному счетчиком 12 адреса, идентичному адресу, выбранному счетчиком 12 адреса в блок накопителя 13.

Таким образом, введение новых признаков и связей обеспечивает повышение достоверности контроля оперативных запоминающих блоков, возможность реализации любого набора контролирующих тестов без внесения

Q изменений в схему устройства, а также возможность соединения устройства с малой ЦВМ, что позволяет автоматизировать контроль оперативных запоминающих блоков и повысить быстродействие

5 устройства, снизив общее время контроля.

Формула изобретения

Устройство для контроля оперативных запоминанмцих блоков, содержащее 9 первый информационный регистр, входы которого подключены к выходам первого коммутатора, первый выход - к пер вому входу второго коммутатора, а второй выход - к первому входу блока сравнения, второй информационный регистр первый выход которого подключен ко второму входу второго коммута тора, второй выход - к первому входу третьего коммутатора, третий выход второго информационного регистра-под ключен ко второму входу блока сравне ния, первый выход которого подключен к третьему входу второго коммутатора второй выход блока сравнения подключен к первому входу блока управления блок регистров, первый выход которого подключен ко входу третьего коммутатора, а второй выход блока регистров подключен к первому входу первого коммутатора, второй вход которого подключен к первому выходу блока управлен 1я, регистр адреса, первый вход котрого подключен ко вто рому выходу блока управления, а выход - к четвертому входу второго коммутатора, дешифратор, первый вы.ход которого подключен ко второму входу блока управления, а второй выход - к пятому входу второго коммута тора, блок синхронизации, выходы которого подключены к третьим входам блока управления, третьи выходы блок управления подключены ко вторым входам третьего коммутатора, отли2чающееся тем, что, с целью повышения быстродействия устройства и повышения точности контроля, оно содержит первый накопитель, перм1й выход которого подключен ко входам блока регистров, а второй выход - ко второму входу регистра адреса, счетчик адреса, первый вход которого подключен к третьему выходу дешифрато| «, вторые входы - к четвертым выходам блока управления, первый аыход - к первому входу первого накопителя, а второй выход - к шестому входу второ го коммутатора, четвертый коммутатор, входы которого подключены к четвертым выходам дешифратора, а выхода ко вторым входам первого накопителя, второй накопитель, первый вход которого подключен к третьему выходу счет1-:ика адреса, а выходы - ко входам второго информационного регистра, и пятый коммутатор, входы которого подключены к пятым выходам дешифратора, а выходы - ко входам второго накопителя. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР ff , кл. G 11 С 29/00, 1972. 2.Авторское свидетельство СССР fP 5«7837, кл. G 11 С 29/00, 1977. 3.Заявка ФРГ М2408990, кл. G 11 С 29/00, опублик. 1976 (прототип).

упр

W/f-

17

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков постоянной памяти | 1982 |

|

SU1049984A1 |

| Устройство для контроля оперативнойпАМяТи | 1978 |

|

SU822297A1 |

| Устройство для тестового контроля блоков памяти | 1986 |

|

SU1365134A1 |

| Устройство для контроля блоковпОСТОяННОй пАМяТи | 1979 |

|

SU824318A1 |

| Устройство для тестового контроля блоков памяти | 1988 |

|

SU1541678A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Постоянное запоминающее устройство с резервированием | 1986 |

|

SU1372363A1 |

| Устройство для контроля постоянной памяти | 1977 |

|

SU693442A1 |

| Оперативное запоминающее устройство с самоконтролем | 1978 |

|

SU771731A1 |

| Устройство сопряжения | 1974 |

|

SU519704A1 |

fyfff

Авторы

Даты

1981-12-15—Публикация

1980-04-09—Подача