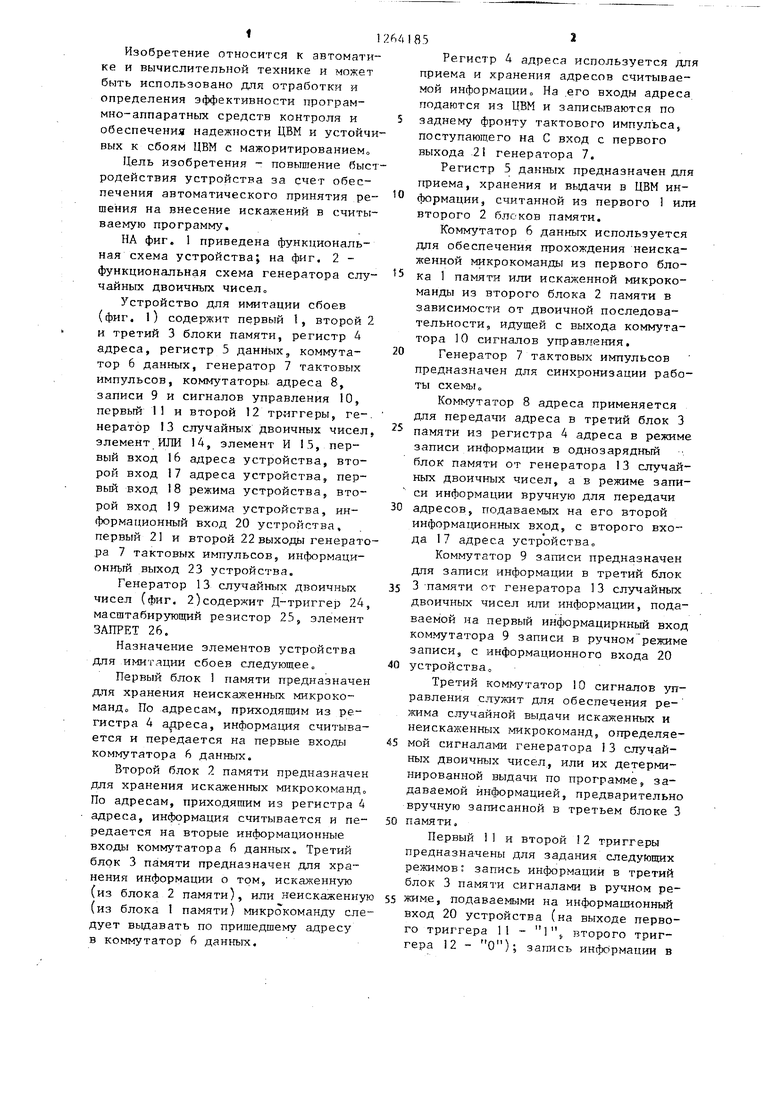

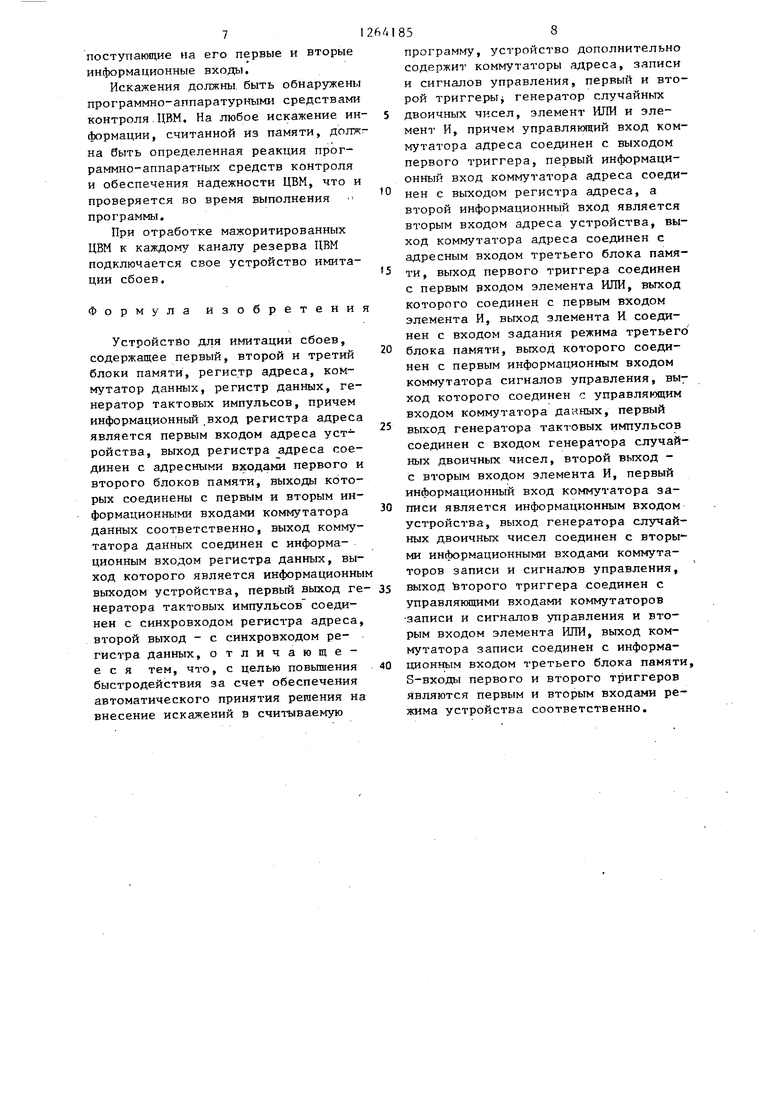

Изобретение относится к автомати ке и вычислительной технике и может быть использовано для отработки и определения эффективности программно-аппаратных средств контроля и обеспечения надежности ЦВМ и устойч вых к сбоям ЦВМ с мажоритированиемо Ц.ель изобретения - повышение быс родействия устройства за счет обеспечения автоматического принятия ре шения на внесение искажений в считы ваемую программу. НА фиг, 1 приведена функциональная схема устройства; на фиг, 2 функциональная схема генератора слу чайных двоичных чисело З стройство для имитации сбоев (фиг. 1) содержит первый 1, второй и третий 3 блоки памяти, регистр 4 адреса, регистр 5 данных, коммутатор 6 данных, генератор 7 тактовых импульсов, коммутаторы, адреса 8, записи 9 и сигналов управления 10, первый 11 и второй 12 триггеры, генератор 13 случайных двоичных чисел элемент ИЛИ 14, элемент И 15, первый вход 16 адреса устройства, второй вход 17 адреса устройства, первый вход 18 режима устройства, второй вход 19 режима устройства, информационный вход 20 устройства, первый 2 и второй 22 выходы генерат .ра 7 тактовых импульсов, ин(}юрмационньгй выход 23 устройства. Генератор 13 случайных дззоичных чисел (фиг. 2)содержит Д-триггер 24 масштабирующий резистор 25, элемент ЗАПРЕТ 26, Назначение элементов устройства для имитации сбоев следующее „ Первый блок 1 памяти предназначе для хранения неискаженных микрокоманд По адресам, приходящим из регистра 4 ацреса, информация считыва ется и передается на первые входы коммутатора 6 данных. Второй блок 2 памяти предназначе для хранения искаженных микрокоманд По адресам, приходящим из регистра адреса, информация считывается и пе редается на вторые информационные входы коммутатора 6 данных. Третий блрк 3 памяти предназначен для хранения информации о том, искаженную (из блока 2 памяти), или неискаженн (из блока 1 памяти) микрокоманду сл дует вьщавать по пришедшему адресу в коммутатор 6 данных. 5 Регистр 4 адреса используется для приема и хранения адресов считываемой информации о На .его входы адреса подаются из ЦВМ и записьгеаются по заднему фронту тактового импульса, поступающего на С вход с первого выхода 21 генератора 7. Регистр 5 данных предназначен для приема, хранения и выдачи в ЦВМ информации, считанной из первого 1 или второго 2 блоков памяти. Комг татор 6 данных используется для обеспечения прохождения неискаженной микрокоманды из первого блока 1 памяти или искаженной микрокоманды из второго блока 2 памяти в зависимости от двоичной последова тельности, идущей с выхода коммутатора 10 сигналов управления. Генератор 7 тактовых импульсов предназначен для синхронизации работы схемыо Коммутатор 8 адреса применяется для передает адреса в третий блок 3 памяти из регистра 4 адреса в режиме записи информации в однозарядный блок памяти от генератора 13 случайных двоичных чисел, а в режиме записи информации вручную для передачи адресов, подаваемых на его второй ИНфОрМаХЩОННЫХ вход, с второго ВХО да 17 адреса устройствао Коммутатор 9 записи предназначен для записи информации в третий блок 3 -памяти от генератора 13 случайных двоичных чисел или информации, подаваемой на первый информацирнный вход коммутатора 9 записи в ручномрежиме записи, с информационного входа 20 устройства. Третий коммутатор 10 сигналов управления служит для обеспечения режима случайной выдачи искаженньпс и неискаженных микрокоманд, определяемой сигнала1чи генератора 13 случайных двоичных чисел., или их детерминированной выдачи по программе5 задаваемой информацией, предварительно вручную записанной в третьем блоке 3 памяти. Первый 11 и второй 2 триггеры предназначены для задания следующих режимов: запись информации в третий блок 3 памяти сигналами в ручном режим.е, подаваемыми на информационный вход 20 устройства (на выходе первого триггера 11 - I, второго триггера 12 - О); запись информации в третий блок 3 памяти от генератора 13 случайных двоичных чисел и выдач искаженных и неискаженных микрокоманд в последовательности, определя мой информацией, записанной в третьем 3памяти (на выходе первого три гера 11 - О,второго триггера ); считывание информации с программой искажений, предварительно за писанной в третий блок 3 памяти в ручном режиме (на выходе первого П и второго 12 триггеров - О, в тре тий блок 3 памяти записана программ искажений)о Триггеры 11 и 12 имеют раздельны входы установки в нуль (не показаны) Генератор 13 случайных двоичных чисел (фиг. 2) предназначен для обе печения автоматического режима прохождения по случайному закону через коммутатор 6 данных искаженной или неискаженной микрокоманды из соотве ствующего блока памяти, причем посредством изменения параметров рези тора генератора случайных двоичных чисел возможно изменение вида закон распределения нулей и единиц, задающих выдачу искаженных микрокоманд. Элемент ИЛИ 14 используется дпя обеспечения задания режима записи или считывания третьему блоку 3 памяти по сигналам первого 11 и второго 12 триггеров. Элемент И 15 предназначен для синхронизации задания режима третьему блоку 3 памяти о Устройство для имитации сбоев работает следующим образом. В исходном состоянии все элементы памяти устройства находятся в нулевом состоянии за исключением первого блока 1 памяти, в котором записаны неискаженные микрокоманды, и второго блока 2 памяти, в котором записаны искаженные микрокоманды (цепи устаНОНКИ в исходное состояние на фиг. 1 и 2 «е показаны)о Устройство может работать в трех режимах: ручной записи информации в третий блок 3 памяти; считътания информации с программой вьщачи искаженных микрокоманд, предварительно записанной в третий блок 3 памяти; автоматической записи информации в . третий блок 3 памяти и одновременной выдачи неискаженных и искаженных мик рокоманд из первого 1 и второго 2 блоков памяти соответственно. 854 При необходимости выдачи программы с заданной последовательностью искаженных микрокоманд сначала в первом режиме в соответствующие адреса третьего блока 3 памяти, по которым необходимо выдать неискаженные микрокоманды, записываются единицы, а искаженные - нули Затем во втором режиме выдается программа с заданной последовательностью искаженных микрокоманд. При необходимости выдачи программы с произвольной последовательностью искаженных микрокоманд устройство функционирует в третьем режиме Режим ручной записи информации в третий блок 3 памяти. Работа начинается с послупления на вход 18 первого триггера 11 единичного сигнала, которьгй через элемент ИЛИ 14 передается на первый вход элемента И 15. При поступленииочередного синхроимпульса с второго выхода 22 генератора 7 тактовых импульсов на второй вход элемента ИЛИ 15 единичный сигнал проходит на вход задания режима третьего блока 3 памяти и устанавливает его в режим записи информации,, Кроме того, единичный сигнал с выхода первого трит гера 1 1 поступает на управлякмций вход коммутатора адреса и открывает его второй информационный вход 17, на который подаются адреса ячеек памяти,- в которые необходимо записать информацию. Адреса с входа 17 через второй информационный вход коммутатора 8 адреса поступают на адресный вход третьего блока 3 памяти. С выхода второго триггера 12, который находится в нулевом состоянии, нулевой сигнал, поступающий на управляющий вход коммутатора 9 записи, открывает его первьй информационный вход 20 J, на который подается информация, записываемая по заданному адресу. Режим считывания информации с программой искажений, предварительно записанной в третий блок 3 памяти. При переводе первого триггера 11 в нулевое состояние нулевой сигнал с его выхода, прошедший через элемент ИЛИ 14, поступает на вход элемента И 15, При приходе первого синхроимпульса с второго выхода 22 генератора 7 тактовых импульсов нулевой сигнал приходит на вход задания 512 блока 3 памяти и усрежима третьего в режим считывания танавливает его информации. Кроме того, нулевой сигнал с выхода первого триггера 1 1 поступает на управляющий вход коммутатора 8 адреса и открывает его первый информационный вход. При приходе адреса считываемой микрокоманды на ЦВМ, на информационный вход 16 регистра адреса он записывается в не го по заднему фронту первого пришедшего синхроимпульса с первого выхода 21 генератора 7 тактовых импульсов. По заднему фронту второго синхроимпульса, поступившего оттуда же, адрес поступает на адресные входы первого 1 и второго -2 блоков памяти, а также через открытый первый информационный вход коммутатора 8 адреса на адресный вход третьего блока памя ти. Информация по пришедшему адресу из первого 1 и 2 блоков памяти поступает на первые и вторые информационные входы коммутатора 6 данных соответственно. Кроме того, информация считывается по этому адресу из третьего блока 3 памяти, поступает на первый информационный вход коммутатора 10 сигналов управления, который открыт нулевым сигналом, поступающим с выхода второго триггера 12 на управляющий вход ко {мутатора 10 сигналов управления, В зависимости от того, что было записано по данному адресу в третьем блоке памяти, выходной сигнал с него через первый информационный вход коммутатора 10 сигналов управления поступает на управляющий вход коммутатора В данных и открывает первый или второй информационный вход, следовательно, через коммутатор 6 данных на информационный вход регистра 3 данных поступает неискаженная или искаженная микрокоманда из первого 1 или второго 2 блоков памяти соответственно. При поступлении синхроимпульса на синхровход регистра 5 данных с второго входа 22 генератора 7 тактовых импульсов микрокоманда записывается в регистр 5 данных, а следующим синхроимпульсом, поступившим оттуда же, она передается для дальнейшей обработки в ЦВМ

Режим автоматической записи информации в третий блок 3 памяти и одновременной выдачи неискаженных и искаженных микрокоманд из первого I

третьего блока 3 /тамяти и устанавливает его в режим записи. Случайная двоичная последовательность с выхода генератора 13 случайных двоичных чисел поступает на второй информационный вход коммутатора 9 записи, который открыт единичным сигналом, поступающим с выхода второго триггера 1 на управляюш,ий вход этого коммутатора, С выхода второго коммутатора 9 информация по адресам, приходящим на адресный вход, записывается в третий блок памяти. Кроме того, двоичная последовательность с выхода генератора 13 случайных двоичный чисел поступает на второй информационный вход коммутатора 10 сигналов управления , который открыт единичным сигналом, поступающим с выхода второго триггера 12 на его управляющий вход. Случайная двоичная последовательность с выхода коммутатора 10 сигналов управления поступает на управляющий вход коммутатора 6 данных и, в зависимости от пришедшего значения пропускает неискаженную или искаженную микрокоманды соответственно из первого 1 и второго 2 блоков памяти. 56 и второго - гшоков памяти соответственно. Для задания этого режима первый триггер I1 устанавливается в нулевое состояние, а второй 12 - в единичное, В этом режиме адрес, записанный в регистр 4 адреса, по приходе синхроимпульса на синхровход с первого выхода 21 генератора 7 тактовых импульсов передается на адресные входы первого 1, второго 2 и третьего 3 блоков памяти, так как первый триггер : 11, находящийся в нулевом состоянии, своим выходным сигналом, поступающим на управляющий вход коммутатора 8 адреса, открывает его первый информационный вход, на который приходит адрес с регистра А адреса. Микрокоманды, считанные по пришедшему адре,у из первого 1 и второго 2 блоков памяти, поступают на первые и вторые информационные входы коммутатора 6 данных соответственно. Второй триггер 12, находящийся в единичном состоянии, единичным выходным сигналом, прошедшим через элемент ИЛИ 14, и при поступлении синхроимпульса с второго выхода 22 генератора 7 тактовых импульсов через элемент И 15 поступает на вход задания режима 7 поступающие на его первые и вторые информационные входы. Искажения должны, быть обнаружены программно-аппаратурными средствами контроля-ЦВМ. На любое искажение ин формации, считанной из памяти, долх на быть определенная реакция программно-аппаратных средств контроля и обеспечения надежности ЦВМ, что и проверяется во время выполнения программы. При отработке мажоритированных ЦВМ к каждому каналу резерва ЦВМ подключается свое устройство имитации сбоев. Формула изобретени Устройстбо для имитации сбоев, содержащее первый, второй и третий блоки памяти, регистр адреса, коммутатор данных, регистр данных, генератор тактовых импульсов, причем информационный .вход регистра адреса является первым входом адреса устройства, выход регистра адреса соединен с адресными входами первого и второго блоков памяти, выходы которых соединены с первым и вторым информационными входами коммутатора данных соответственно, выход коммутатора данных соединен с информационным входом регистра данных, выход которого является информационны выходом устройства, первый выход ге нератора тактовых импульсов соединен с синхровходом регистра адреса, второй выход - с синхровходом регистра данных, отличающееся тем, что, с целью повьппения быстродействия за счет обеспечения автоматического принятия решения на внесение искажений в считываемую 858 программу, устройство дополнительно содержит коммутаторы адреса, записи и сигналов управления, первый и второй триггерыj генератор случайных двоичных чисел, элемент ИЛИ и элемент И, причем управлянлдий вход коммутатора адреса соединен с выходом первого триггера, первый информационный вход коммутатора адреса соединен с выходом регистра адреса, а второй информационный вход является вторым входом адреса устройства, выход коммутатора адреса соединен с адресным входом третьего блока памяти, выход первого триггера соединен с первым входом элемента ИЛИ, выход которого соединен с первым входом элемента И, выход элемента И соединен с входом задания режима третьего блока памяти, выход которого соединен с первым информационным входом коммутатора сигналов управления, ВЫ7 ход которого соединен с управляющим входом коммутатора данных, первый выход генератора тактовых импульсов соединен с входом генератора случайных двоичных чисел, второй выход с вторым входом элемента И, первый информационный вход коммутатора записи является информационным входом устройства, выход генератора случайных двоичных чисел соединен с вторыми информационными входами коммутаторов записи и сигналов управления, выход йторого триггера соединен с управляющими входами коммутаторов записи и сигналов управления и вторым входом элемента ИЛИ, выход коммутатора записи соединен с информационным входом третьего блока памяти, S-входы первого и второго триггеров являются первым и вторым входами режима устройства соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления с динамической памятью | 1985 |

|

SU1260954A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1275442A1 |

| Микропрограммное устройство управления | 1981 |

|

SU1016782A1 |

| Микропрограммное устройство управления с контролем и восстановлением | 1983 |

|

SU1120337A1 |

| Микропрограммное устройство управления с контролем и восстановлением | 1984 |

|

SU1242947A1 |

| Устройство для программного управления | 1989 |

|

SU1656498A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Микропрограммное устройство для управления обменом управляющей информацией в распределенной системе | 1986 |

|

SU1325477A1 |

| Устройство для сортировки информации | 1986 |

|

SU1365075A1 |

| Устройство для контроля и управления технологическими процессами | 1984 |

|

SU1193641A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для отработки и определения эффективности программно-аппаратных средств контроля и обеспечения надежности ЦВМ и устойчивых к сбоям ЦВМ с мажоритированием. Цель изобретения - повышение быстродействия устройства путем.обеспечения автоматического принятия решения на внесение искажения в считываемую программу, запоминания порядка следования искаженных и неискаженных микрокоманд и обеспечения возможности повторения псевдослучайной последовательности их чередования. Устройство содержит три блока памяти, регистр адреса, регистр данных, коммутаторы данных, адреса, записи § и сигналов управления, генератор тактовых импульсов, генератор слу(Л чайных двоичных чисел, два триггера, элемент И и элемент ИЛИ. 2 ил

| Устройство для имитации сбоев цифровых вычислительных машин | 1980 |

|

SU879592A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для имитации сбоев | 1983 |

|

SU1107126A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-15—Публикация

1985-05-20—Подача