112

Изобретение относится к вычислительной технике, а именно к цифровым измерительным преобразователям частота - код, и может быть использовано в системах преобразования формы ин- формации,

Цель изобретения - повьшение быстродействия преобразования,

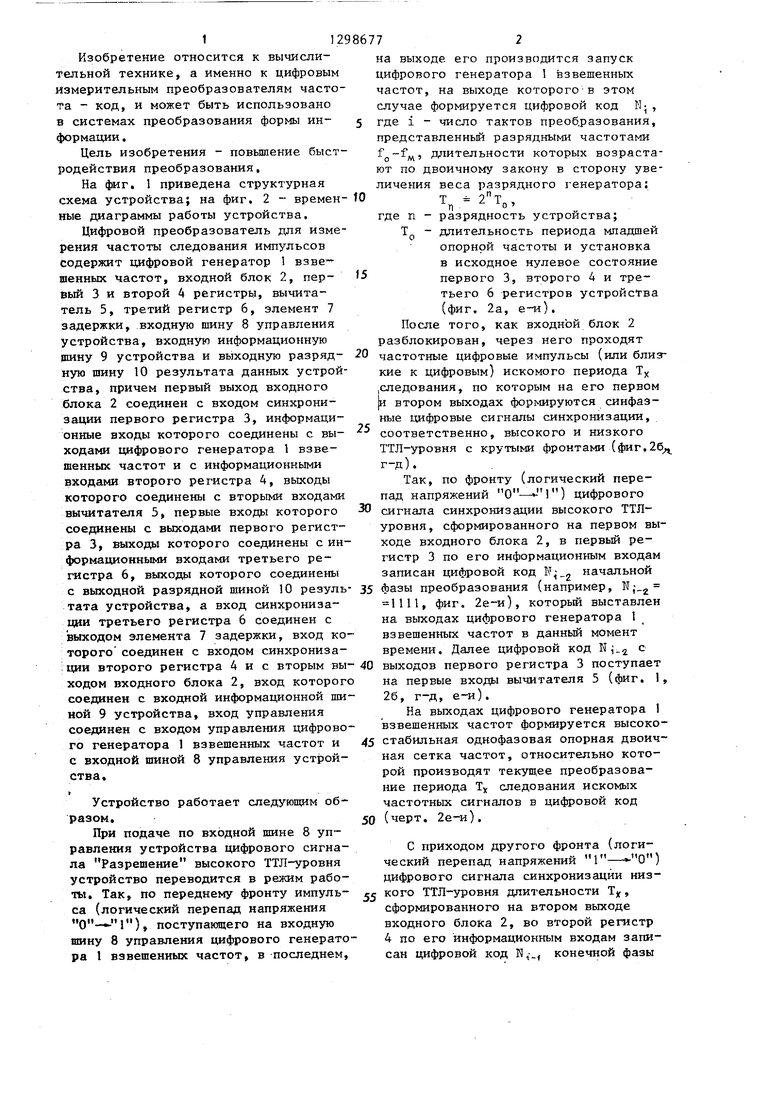

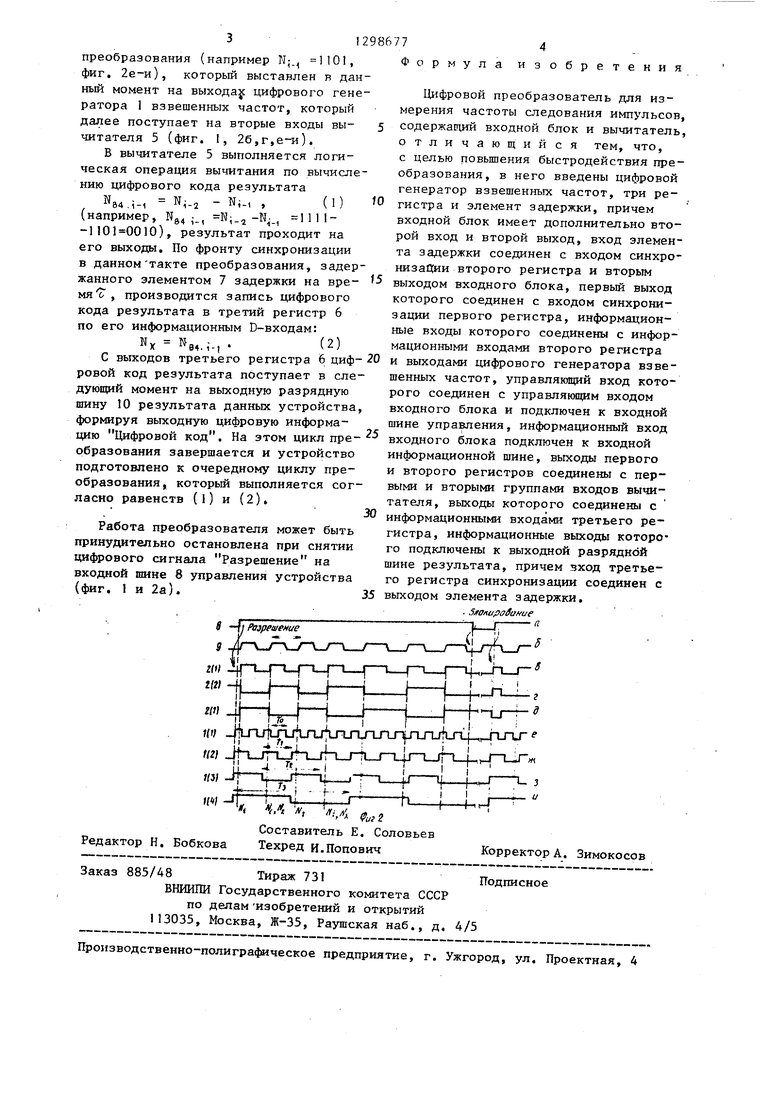

На фкг, приведена структурная схема устройства; на фиг, 2 - времен ные диаграммы работы устройства.

Цифровой преобразователь для измерения частоты следования импульсов Содержит цифровой генератор 1 взве- шенных частот, входной блок 2, первый 3 и второй А регистры, вычита- тель 5, третий регистр 6, элемент 7 задержки, входную шину 8 управления устройства, входную информационную шину 9 устройства и выходную разрядную шину 10 результата данных устройства, причем первый выход входного блока 2 соединен с входом синхронизации первого регистра 3, информационные входы которого соединены с выходами цифрового генератора 1 взвешенных частот и с информационными входами второго регистра 4, выходы которого соединены с вторыми входами вычитателя 5, первые входы которого соединены с выходами первого регистра 3, выходы которого соединены с информационными входами третьего ре

Так, по фронту (логический перепад напряжений ) цифрового 30 сигнала синхронизации высокого ТТЛ- уровня, сформированного на первом выходе входного блока 2, в первый регистр 3 по его информационным входам записан цифровой код начальной

гистра 6, выходь которого соединены

с выходной разрядной шиной 10 резуль- 35 фазы преобразования (например, тата устройства, а вход синхрониза- 1111, фиг. 2е-и), который выставлен дин третьего регистра 6 соединен с выходом элемента 7 задержки, вход которого соединен с входом синхрониза- ции второго регистра А и с вторым вы- 40 выходов первого регистра 3 поступает ходом входного блока 2, вход которого на первые входы вычитателя 5 (фиг, 1, соединен с входной информационной шиной 9 устройства, вход управления соединен с входом управления цифровона выходах цифрового генератора 1 взвешенных частот в данный момент времени. Далее цифровой код Nj.,

26, г-д, е-и).

На выходах цифрового генератора 1 взвешенных частот формируется высокого генератора 1 взвешенных частот и 45 стабильная однофазовая опорная двоичс входной шиной 8 управления ства.

Л. .

Устройство работает следующем образом.

При подаче по входной шине 8 управления устройства цифрового сигнала Разрешение высокого ТТЛ-уровня устройство переводится в режим работы. Так, по переднему фронту импуль- кого ТТЛ-уровня дпительности Tjf,

са (логический перепад напряжениясформированного на втором выходе

), поступающего на входнуювходного блока 2, во второй регистр

шину 8 управления цифрового генерато-4 по его информационным входам запира 1 взвешенных частот, в последнем,сан цифровой код И,-., конечной фазы

5

5

O

на выходе его производится запуск цифрового генератора 1 взвешенных частот, на выходе которого-в этом случае формируется цифровой код N, где i - число тактов преобразования, представленньй разрядными частотами длительности которых возрастают по двоичному закону в сторону увеличения веса разрядного генератора: Т

где п Т„

о т -П - 2 0

разрядность устройства;

длительность периода младшей опорной частоты и установка в исходное нулевое состояние первого 3, второго 4 и третьего 6 регистров устройства (фиг, 2а, e-n-i).

После того, как входной блок 2 разблокирован, через него проходят 0 частотные цифровые импульсы (или близкие к цифровым) искомого периода Т .следования, по которым на его первом |и втором выходах формируются синфазные цифровые сигналы синхронизации, соответственно, высокого и низкого ТТЛ-уровня с крутыми фронтами (фиг,26 г-д).

Так, по фронту (логический перепад напряжений ) цифрового 30 сигнала синхронизации высокого ТТЛ- уровня, сформированного на первом выходе входного блока 2, в первый регистр 3 по его информационным входам записан цифровой код начальной

5

35 фазы преобразования (например, 1111, фиг. 2е-и), который выставлен 40 выходов первого регистра 3 поступает на первые входы вычитателя 5 (фиг, 1,

фазы преобразования (например, 1111, фиг. 2е-и), который выставле выходов первого регистра 3 поступае на первые входы вычитателя 5 (фиг,

на выходах цифрового генератора 1 взвешенных частот в данный момент времени. Далее цифровой код Nj.,

фазы преобразования (например, 1111, фиг. 2е-и), который выставлен выходов первого регистра 3 поступает на первые входы вычитателя 5 (фиг, 1,

26, г-д, е-и).

На выходах цифрового генератора 1 взвешенных частот формируется высоконая сетка частот, относительно которой производят текущее преобразование периода Ту следования искомых частотных сигналов в цифровой код 50 (черт. 2е-и),

С приходом другого фронта (логический перепад напряжений ) цифрового сигн;зла синхронизации низпреобразования (например N;., 1101, фиг. 2е-и), который выставлен в данный момент на выхода цифрового генератора 1 взвешенных частот, который далее поступает на вторые входы вы- читателя 5 (фиг. 1, 2б,г,е-и).

В вычитателе 5 выполняется логическая операция вычитания по вычислению цифрового кода результата

N94 И-, N.2 - Wi., ,(1

(например, Ng , N;.o-N,-, 1111

1--2

-1101 0010), результат проходит на его выходы. По фронту синхронизации в данном такте преобразования, задержанного элементом 7 задержки на вре- мя , производится запись цифрового кода результата в третий регистр 6 по его информационным D-входам:

NX .,--, 2 с выходов третьего регистра 6 циф-

ровой код результата поступает в следующий момент на выходную разрядную шину 10 результата данных устройства формируя выходную цифровую информацию Цифровой код. На этом цикл преобразования завершается и устройство подготовлено к очередному циклу преобразования, который выполняется coi- ласно равенств (1) и (2).

Работа преобразователя может быть принудительно остановлена при снятии цифрового сигнала Разрешение на входной шине 8 управления устройства (фиг. I и 2а).

рмула

изобретения

10

-5

0

-

0

5

Цифровой преобразователь для измерения частоты следования импульсов, содержащий входной блок и вычитатель, отличающийся тем, что, с целью повьппения быстродействия преобразования, в него введены цифровой генератор взвешенных частот, три регистра и элемент задержки, причем входной блок имеет дополнительно второй вход и второй выход, вход элемента задержки соединен с входом синхро- низа13;ии второго регистра и вторым выходом входного блока, первый выход которого соединен с входом синхронизации первого регистра, информационные входы которого соединены с информационными входами второго регистра и выходами цифрового генератора взвешенных частот, управляющий вход которого соединен с управляющим входом входного блока и подключен к входной шине управления, информационный вход входного блока подключен к входной информационной шине, выходы первого и второго регистров соединены с первыми и вторыми группами входов вычи- тателя, выходы которого соединены с информационными входами третьего регистра, информационные выходы которого подключены к выходной разрядной шине результата, причем вход третьего регистра синхронизации соединен с выходом элемента задержки. . 5fo/uif aSaHae

W -jlnjiCrufUT riJTJTJTJ//г; jH JT-ujH ff - I- i- : J4. rV--.-i iI I

/w

Редактор H. Бобкова

Л ф,,2 Составитель E. Соловьев Техред И.Попович

Корректор А. Зимокосов

Заказ 885/48 Тираж 731Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственио-полигра4 1ческое предприятие, г. Ужгород, ул. Проектная, 4

Изобретение относится к области вычислительной техники и может быть использовано в системах преобразования формы информации. Цель изобретения - повышение быстродействия преобразования. Преобразователь содержит входной блок 2, вычислитель 5 и шины 8-10 управления, информацис нную и результата данных устройства. Для достижения поставленной цели в устройство введены генератор 1 взвешенных частот, регистры 3, 4 и 6, элемент 7 задержки с образованием новых функциональных связей. 2 ил. W С ьэ со оо 05 vj 0uz. }

Авторы

Даты

1987-03-23—Публикация

1985-08-15—Подача