L

§

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой преобразователь для измерения частоты следования импульсов | 1985 |

|

SU1298677A1 |

| Цифровой измеритель отношения временных интервалов | 1987 |

|

SU1499312A1 |

| Преобразователь линейных перемещений (его варианты) | 1985 |

|

SU1285631A1 |

| УЛЬТРАЗВУКОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЙ | 1991 |

|

RU2035692C1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Умножитель частоты следования импульсов | 1989 |

|

SU1728964A2 |

| АВТОМАТИЧЕСКИЙ СЛЕДЯЩИЙ ДЕЛИТЕЛЬ ПЕРИОДОВ ИМПУЛЬСНЫХ СИГНАЛОВ | 1992 |

|

RU2105410C1 |

| Ультразвуковой измеритель перемещений | 1989 |

|

SU1619027A1 |

| УСТРОЙСТВО ФАЗОВОЙ СИНХРОНИЗАЦИИ | 1997 |

|

RU2119717C1 |

| Измерительный преобразователь длительности временных интервалов | 1985 |

|

SU1357913A1 |

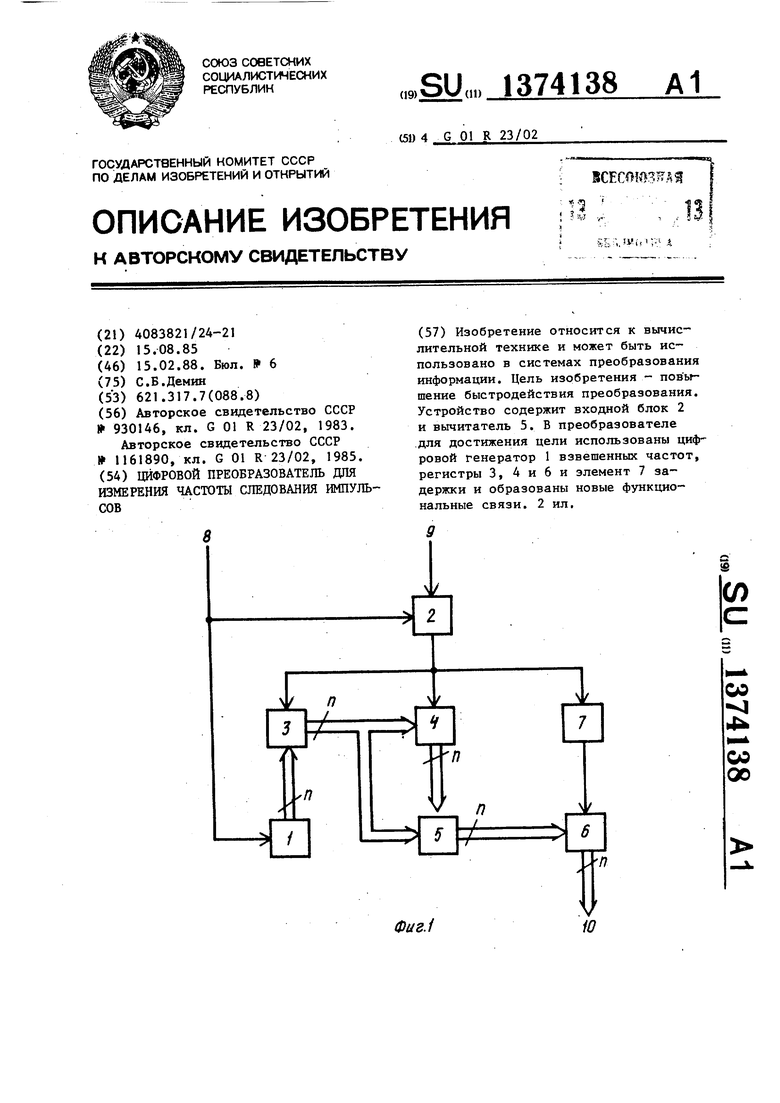

Изобретение относится к вычислительной технике и может быть использовано в системах преобразования информации. Цель изобретения - пов ы- шение быстродействия преобразования. Устройство содержит входной блок 2 и вычитатель 5. В преобразователе для достижения цели использованы цифровой генератор 1 взвешенных частот, регистры 3, 4 и 6 и элемент 7 задержки и образованы новые функциональные связи. 2 ил.

WL П

-П

f

-/7

оо

4

00 00

« I

V /7 /

Изобретение относится к области вычислительной техники, а именно к цифровым измерительным преобразователям частота-код, и может быть ис- пользовано в системах преобразования информации.

Целью изобретения является повьг- шение быстродействия преобразования.

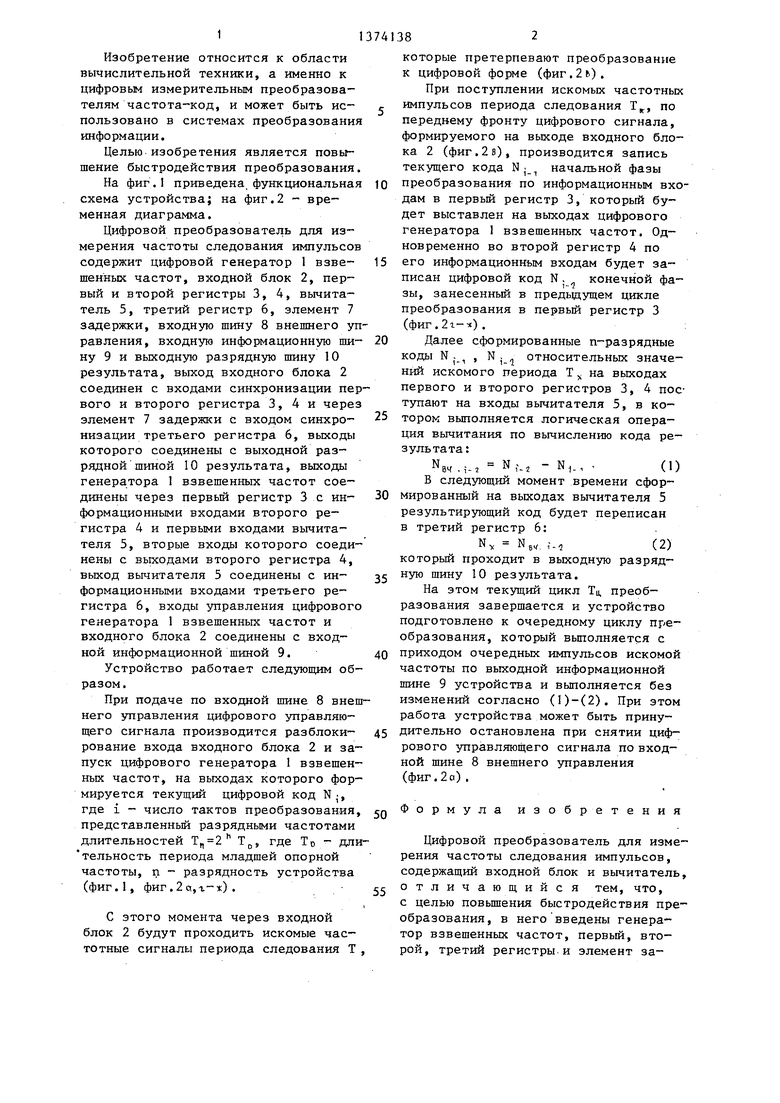

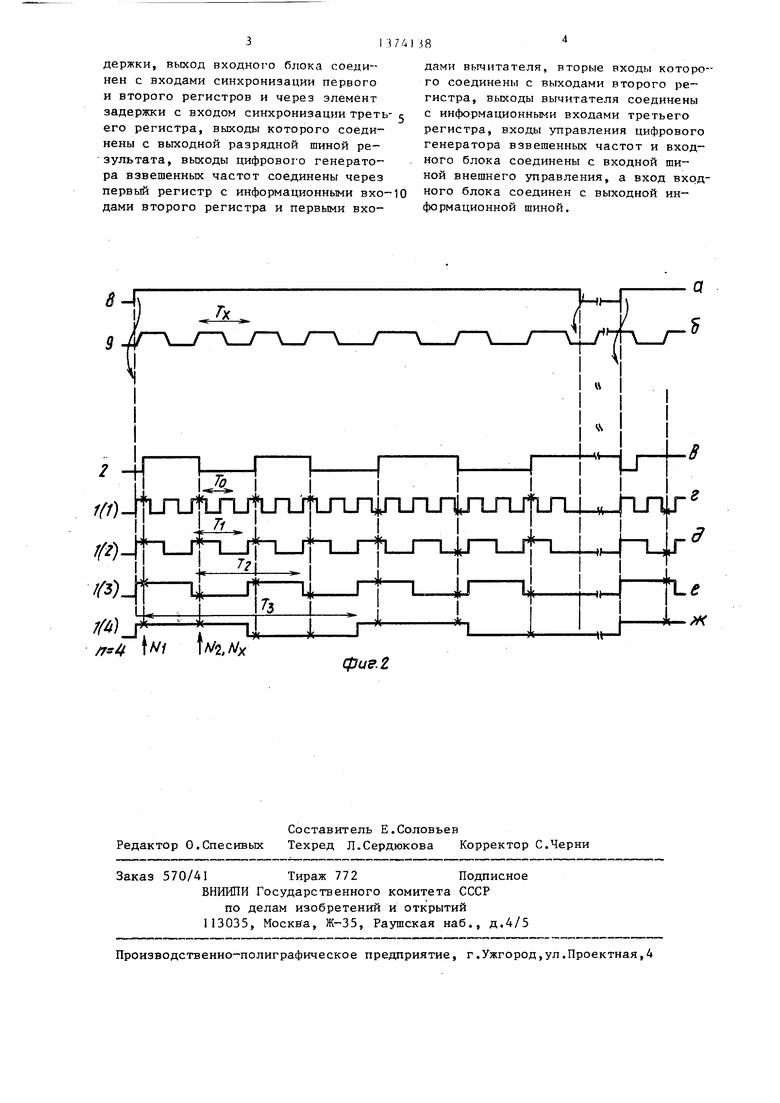

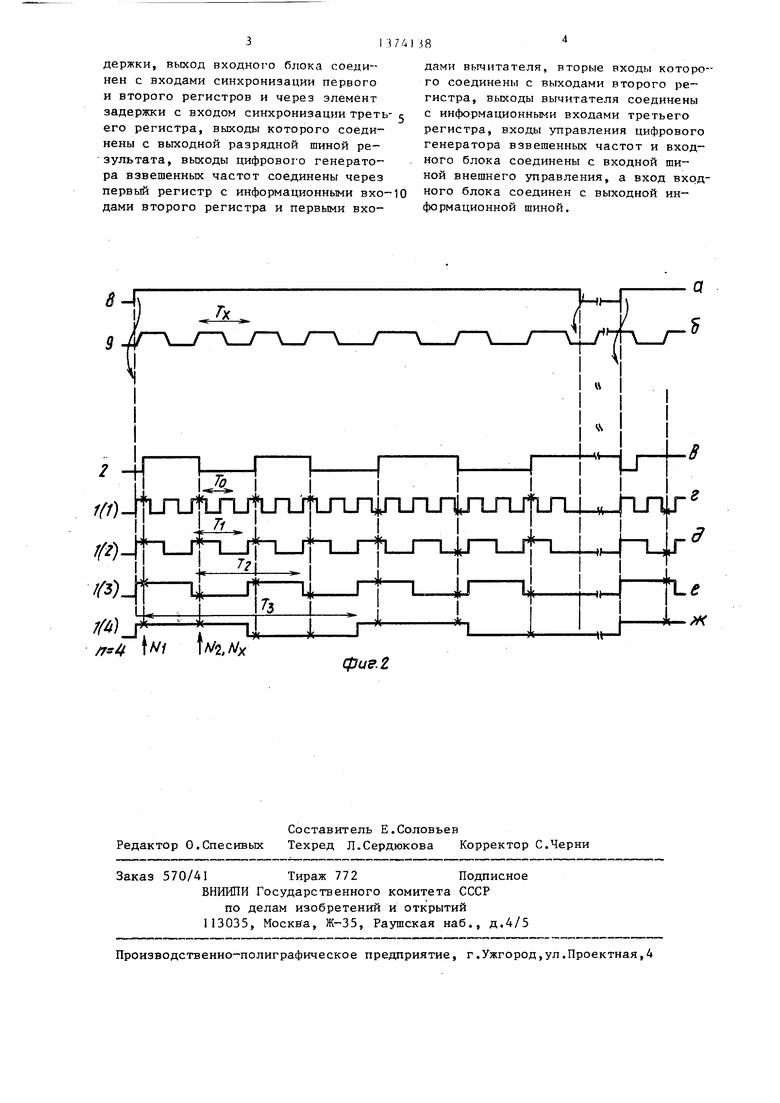

На фиг.I приведена, функциональная схема устройства; на фиг.2 - временная диаграмма.

Цифровой преобразователь для измерения частоты следования импульсов содержит цифровой генератор 1 взве- шенных частот, входной блок 2, первый и второй регистры 3, 4, вычита- тель 5, третий регистр 6, злемент 7 задержки, входную шину 8 внешнего управления, входную информационную ши- ну 9 и выходную разрядную шину 10 результата, выход входного блока 2 соединен с входами синхронизации первого и второго регистра 3, 4 и через злемент 7 задержки с входом синхро- низации третьего регистра 6, выходы которого соединены с выходной раз- рядной шиной 10 результата, выходы генератора 1 взвешенных частот соединены через первый регистр 3 с ин- формационными входами второго регистра 4 и первыми входами вычита- теля 5, вторые входы которого соединены с выходами второго регистра 4, выход вьгаитателя 5 соединены с ин- формационными входами третьего регистра 6, входы управления цифрового генератора 1 взвешенных частот и входного блока 2 соединены с входной информационной шиной 9.

Устройство работает следуюш;им образом.

При подаче по входной шине 8 внешнего управления цифрового управляющего сигнала производится разблоки- рование входа входного блока 2 и запуск цифрового генератора 1 взвешенных частот, на выходах которого формируется текущий цифровой код N, где i - число тактов преобразования, предетавленньй разрядньми частотами длительностей Т, где TD - дли тельность периода младшей опорной частоты, п - разрядность устройства (фиг.1, фиг. 2 а, г-ж).

С этого момента через входной блок 2 будут проходить искомые частотные сигналы периода следования Т

которые претерпевают преобразование к цифровой форме (фиг.2(.).

При поступлении искомых частотных импульсов периода следования Т, по переднему фронту цифрового сигнала, формируемого на выходе входного блока 2 (фиг.2 в), производится запись текущего кода Nj начальной фазы преобразования по информационным входам в первьй регистр 3, который будет выставлен на выходах цифрового генератора 1 взвешенных частот. Одновременно во второй регистр 4 по его информационным входам будет записан цифровой код N . конечной фа1 Y

зы, занесенный в предыдущем цикле преобразования в первый регистр 3 (фиг . 2г-) .

Далее сформированные п-разрядные коды Nj , N, относительных значений искомого периода Т на выходах первого и второго регистров 3, 4 поступают на входы вычитателя 5, в котором выполняется логическая операция вычитания по вычислению кода результата:

NB.,--. N,.. - N,., - (1) В следующий момент времени сформированный на выходах вычитателя 5 результирующий код будет переписан в третий регистр 6:

NV N,,. ,-.,(2)

который проходит в выходную разрядную шину 10 результата.

На этом текущий цикл Тц преобразования завершается и устройство подготовлено к очередному циклу преобразования, который выполняется с приходом очередных импульсов искомой частоты по выходной информационной шине 9 устройства и выполняется без изменений согласно (1)-(2). При этом работа устройства может быть принудительно остановлена при снятии цифрового управляюш;его сигнала по входной шине 8 внешнего управления (фиг.2а).

Формула изобретения

Цифровой преобразователь для измерения частоты следования импульсов, содержащий входной блок и вычитатель отличающийся тем, что, с целью повьш1ения быстродействия преобразования, в него введены генератор взвешенных частот, первый, второй, третий регистры и элемент за-

держки, выход входнот о блока соединен с входами синхронизации первого и второго регистров и через элемент задержки с входом синхронизации треть его регистра, выходы которого соединены с выходной разрядной шиной ре- зультата, выходы цифрового генератора взвешенных частот соединены через первьй регистр с информационными входами второго регистра и первыми входами вьгчитателя, вторые входы которого соединены с выходами второго регистра, выходы вычитателя соединены с информационными входами третьего регистра, входы управления цифрового генератора взвешенных частот и входного блока соединены с входной шиной внешнего управления, а вход входного блока соединен с выходной информационной шиной.

1

| Устройство цифрового измерения частоты следования импульсов | 1980 |

|

SU930146A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровой измеритель длительности периода | 1979 |

|

SU1161890A2 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-02-15—Публикация

1985-08-15—Подача