11

Изобретение относится к кмпульс- ной технике, в частности к измерительным преобразователям длительности временных интервалов.

Целью изобретения является повышение точности измерения и расширение динамического диапазона.

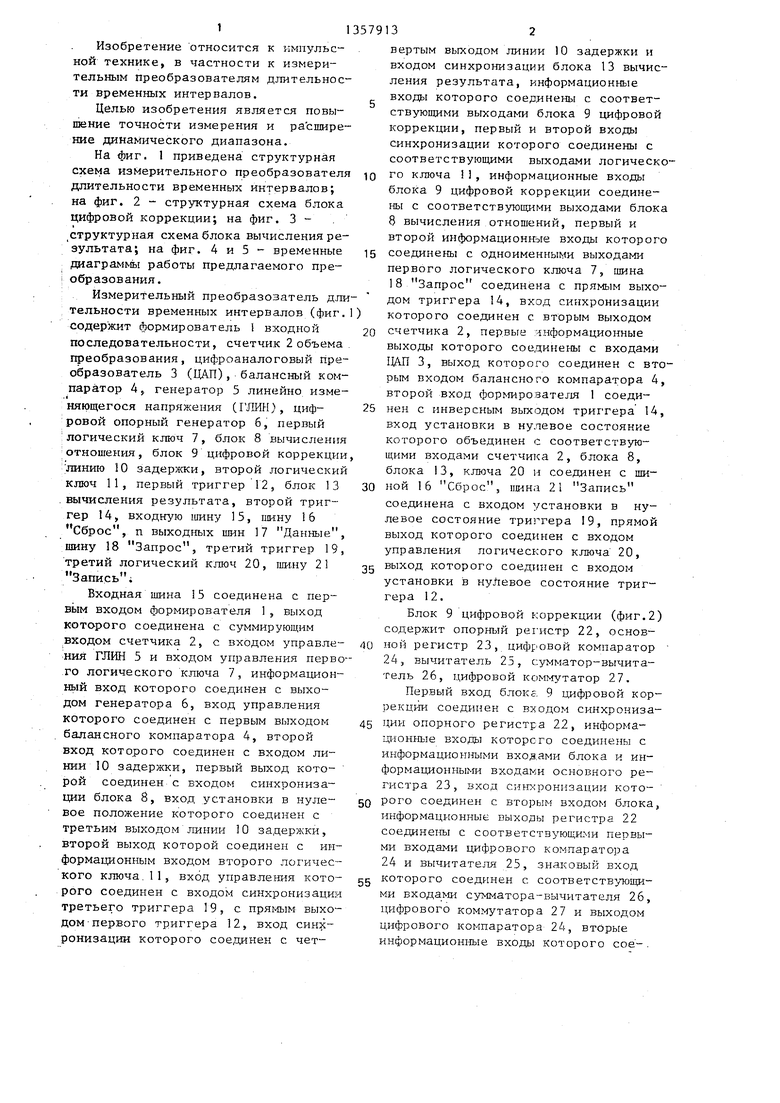

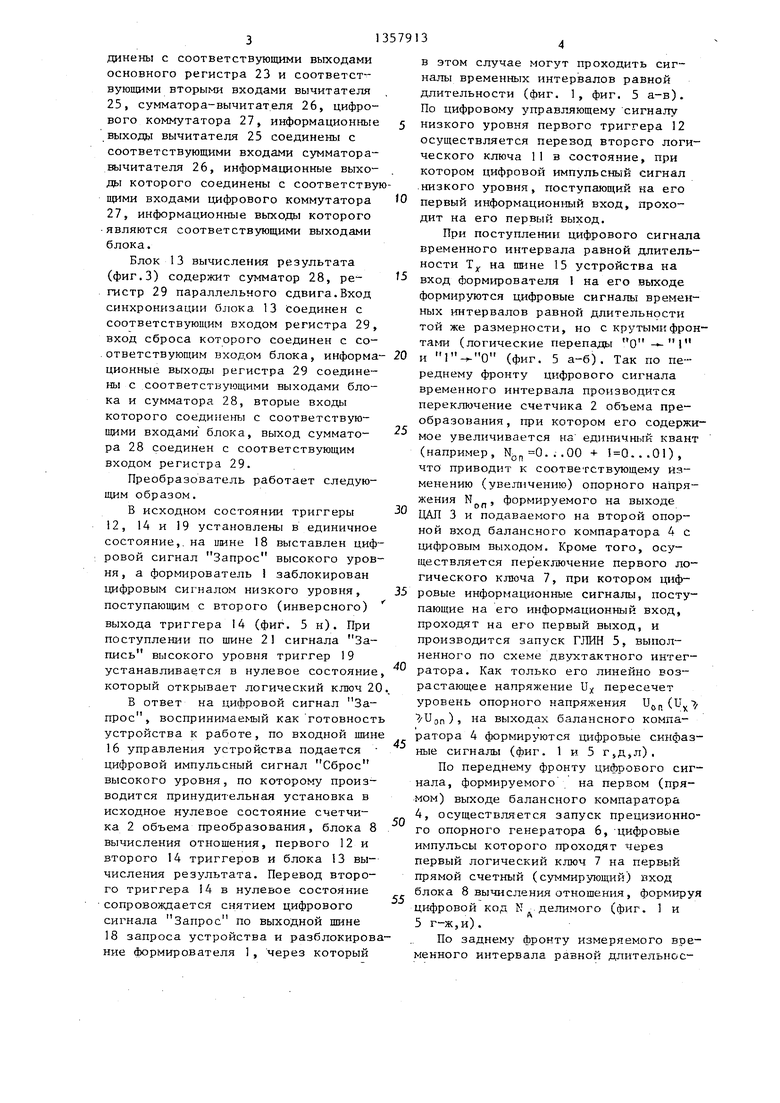

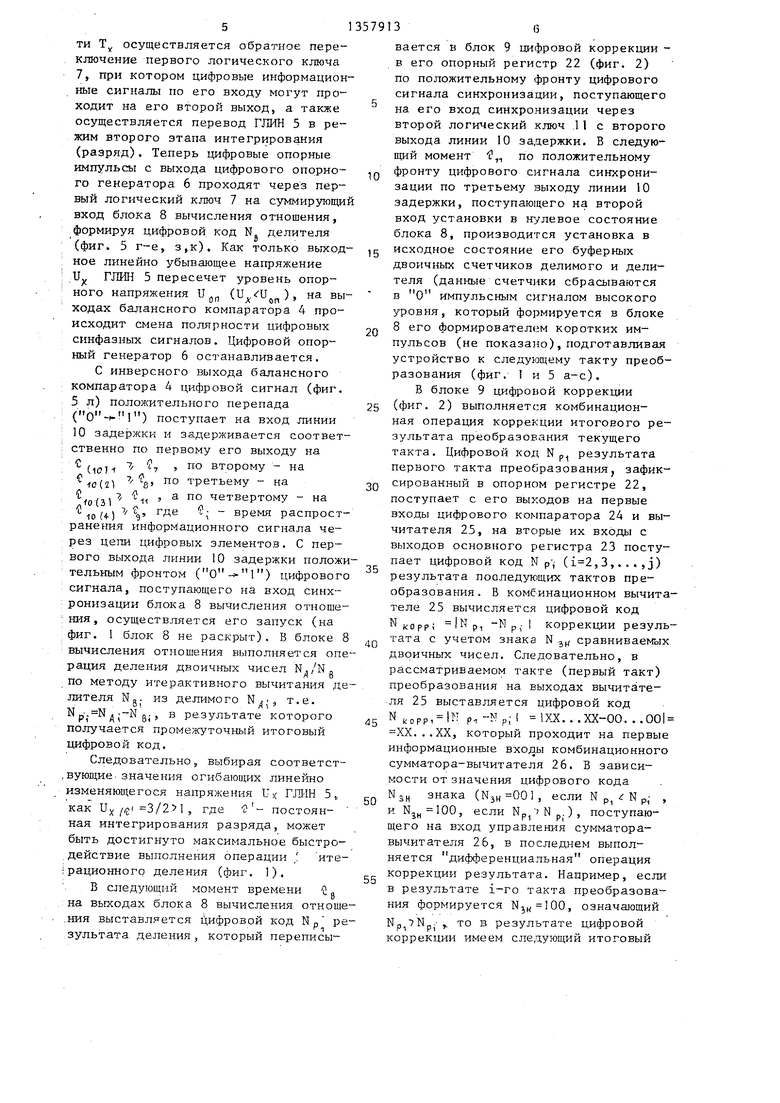

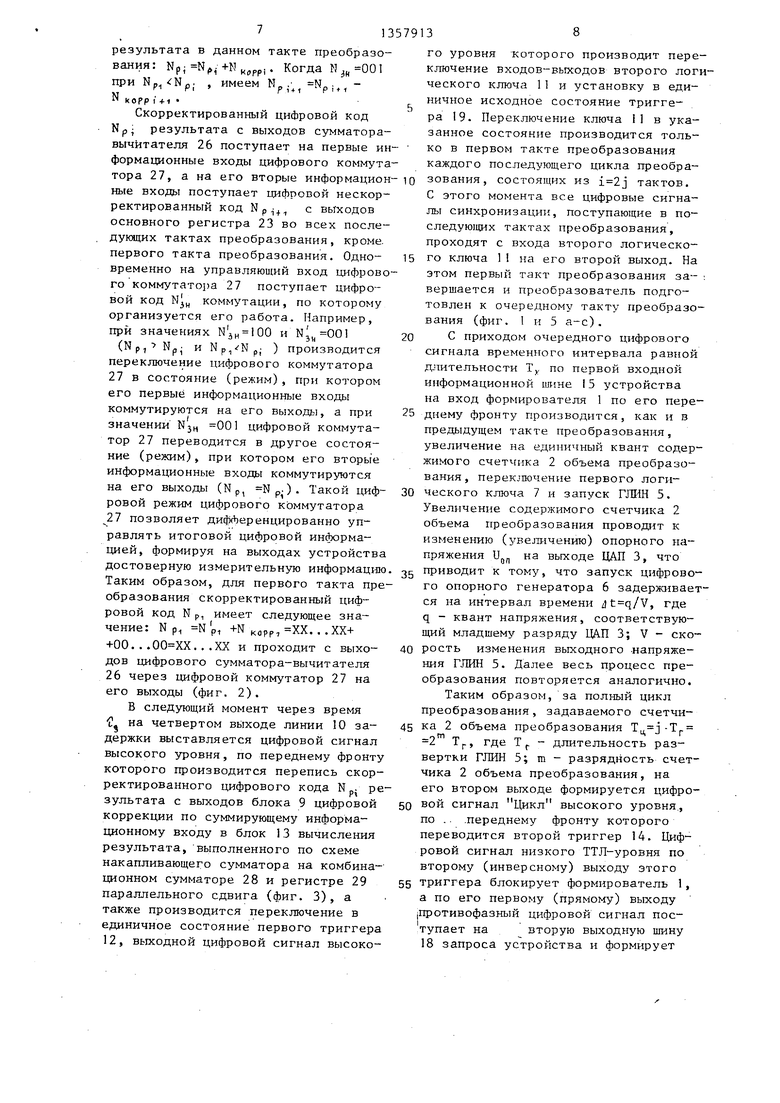

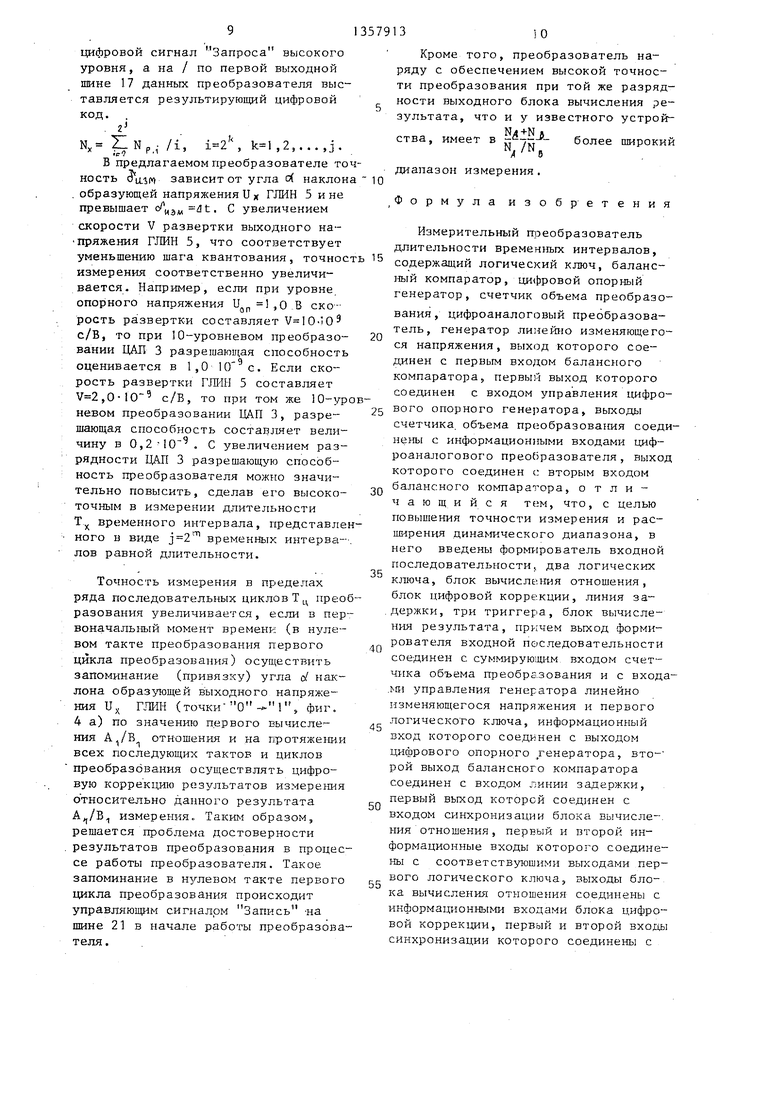

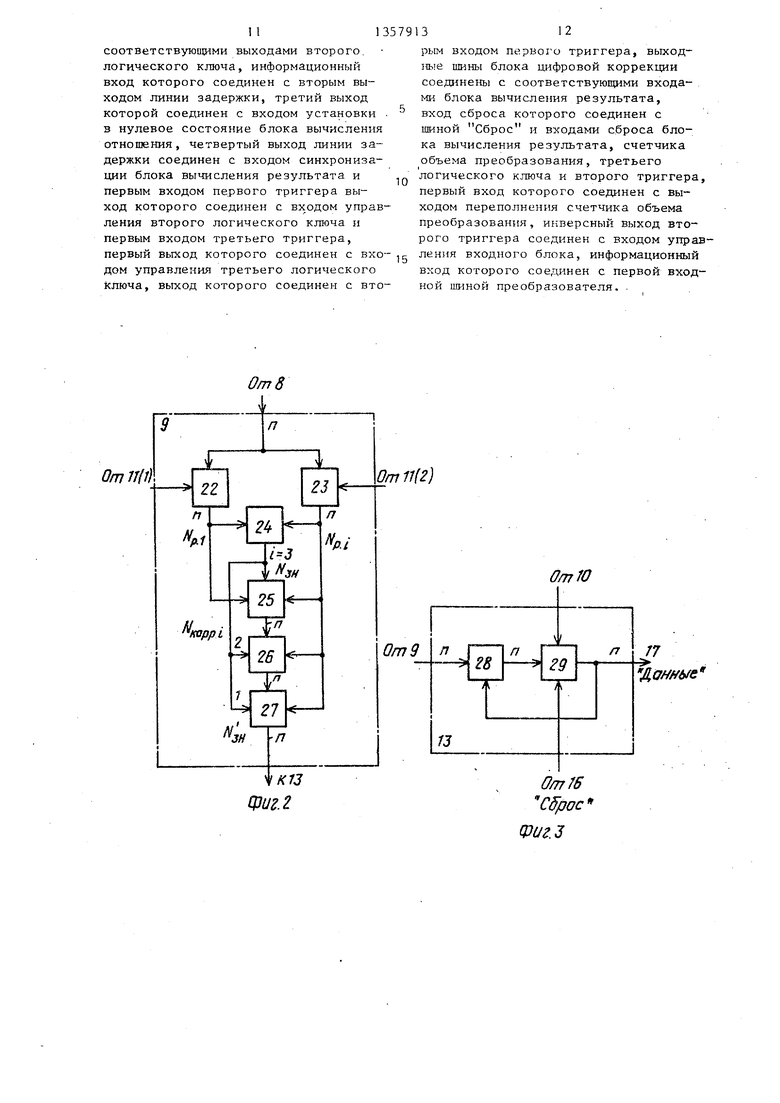

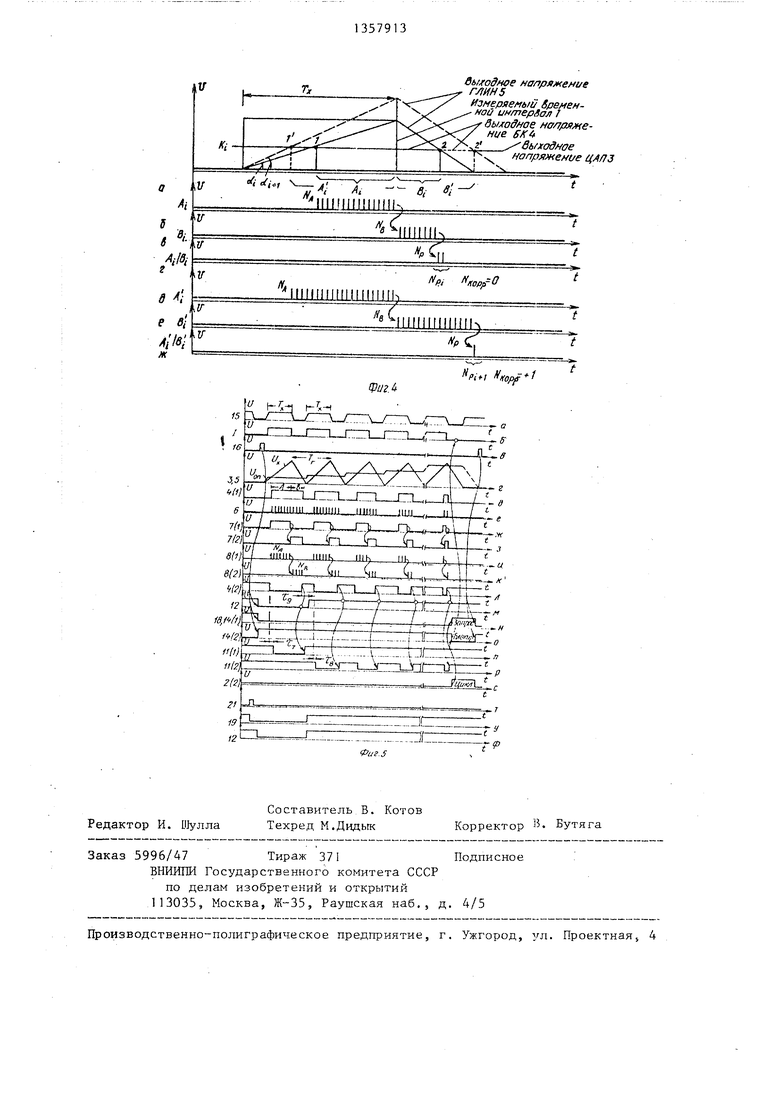

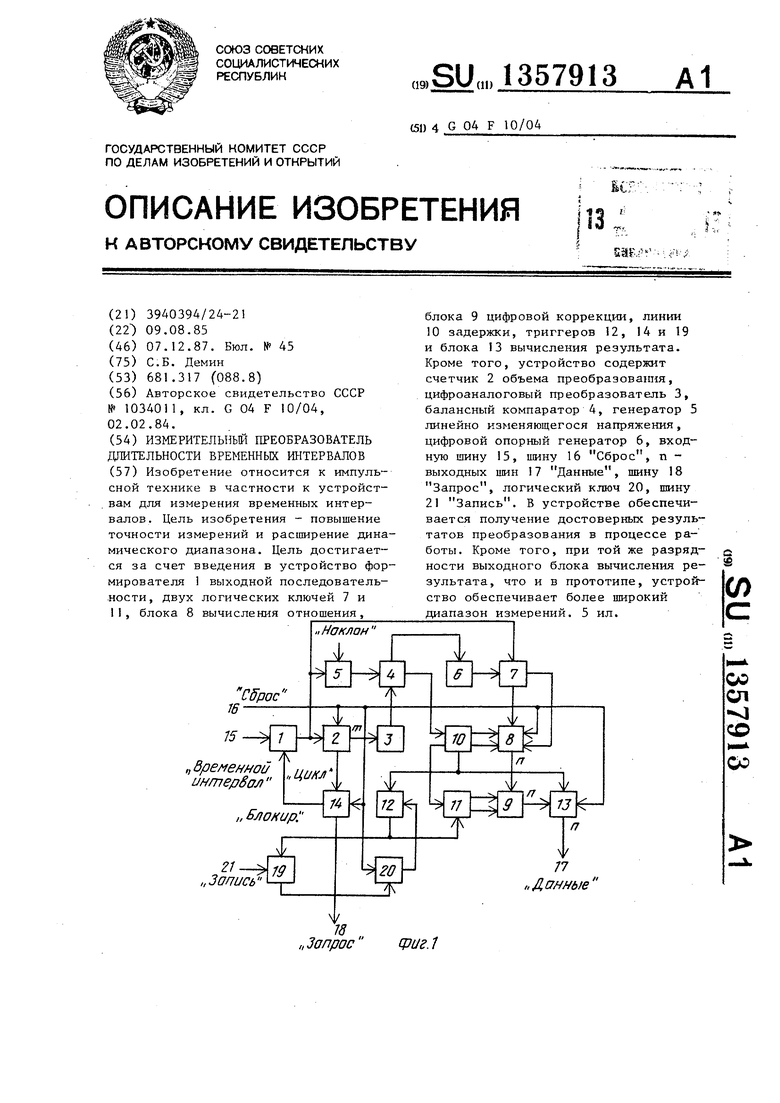

На |)иг. 1 приведена структурная схема измерительного преобразователя длительности временных интервалов; на фиг. 2 - структурная схема блока цифровой коррекции; на фиг. 3 - структурная схема блока вычисления результата; на фиг. 4 и 5 - временные диаграм№1 работы предлагаемого преобразования.

Измерительный преобразователь д.пи тельности временных интервалов (фиг. содержит формирователь 1 входной последовательности, счетчик 2 объема гфеобразования, цифроаналоговый преобразователь 3 (ЦАП), балансный компаратор 45 генератор 5 линейно изменяющегося напряжения (ГЛИМ), циф- ровой опорный генератор б, первый Алогический ключ 7, блок 8 вычисления отношения, блок 9 цифровой коррекции линию 10 задержки, второй логический ключ 11, первый триггер 12, блок 13 вычисления результата, второй триггер 14, входную шину 15, шину 16 Сброс, п выходных шин 17 Данные, шину 18 Запрос, третий триггер 19, третий логический ключ 20, ши.ну 21 Запись ;

Входная шина 15 соединена с первым входом формирователя 1, выход которого соединена с суммирующим входом счетчика 2, с входом управле- ния ГЛИН 5 и входом управления перво ,го логического ключа 7, информацион- НЬ1Й вход которого соединен с выходом генератора 6, вход управления которого соединен с первым выходом балансного компаратора 4, второй вход которого соединен с входом линии 10 задержки, первый выход которой соединен с входом синхронизации блока 8, вход, установки в нуле- вое положение которого соединен с третьим выходом линии 10 задержки, второй выход которой соединен с информационным входом второго логического ключа.11, вход управления кото- рого соединен с входом синхронизации третьего триггера 19, с прямым выходом -первого триггера 12, вход синхронизации которого соединен с чет32

вертым выходом линии 10 задержки и входом синхронизации блока 13 вычисления результата, информационные входы которого соединены с соответствующими выходами блока 9 цифровой коррекции, первый и второй входы синхронизации которого соединены с соответствующими выходами логического ключа , информационные входы блока 9 цифровой коррекции соединены с соответствующими выходами блока 8 вычисления отношений, первый и второй информационшге входы которого соединены с одноименными выходами первого логического ключа 7, шина 18 Запрос соединена с прямым выходом триггера 14, вход синхронизации которого соединен с вторым выходом счетчика 2, первые информационные выходы которого соединены с входами 11ДП 3, выход которого соединен с вторым входом балансного компаратора 4 второй вход фap mpoвaтeля 1 соединен с инверсным выходом триггера 14 вход установки в нулевое состояние которого объединен с соответствующими входами счетчика 2, блока 8, блока 13, ключа 20 м соединен с шиной 16 Сброс, тина 21 Запись соединена с входом установки в нулевое состояние триггера 19, прямой выход которого соединен с входом управления логического ключа 20, выход которого соедтген с входом установки в нулевое состояние триггера 12.

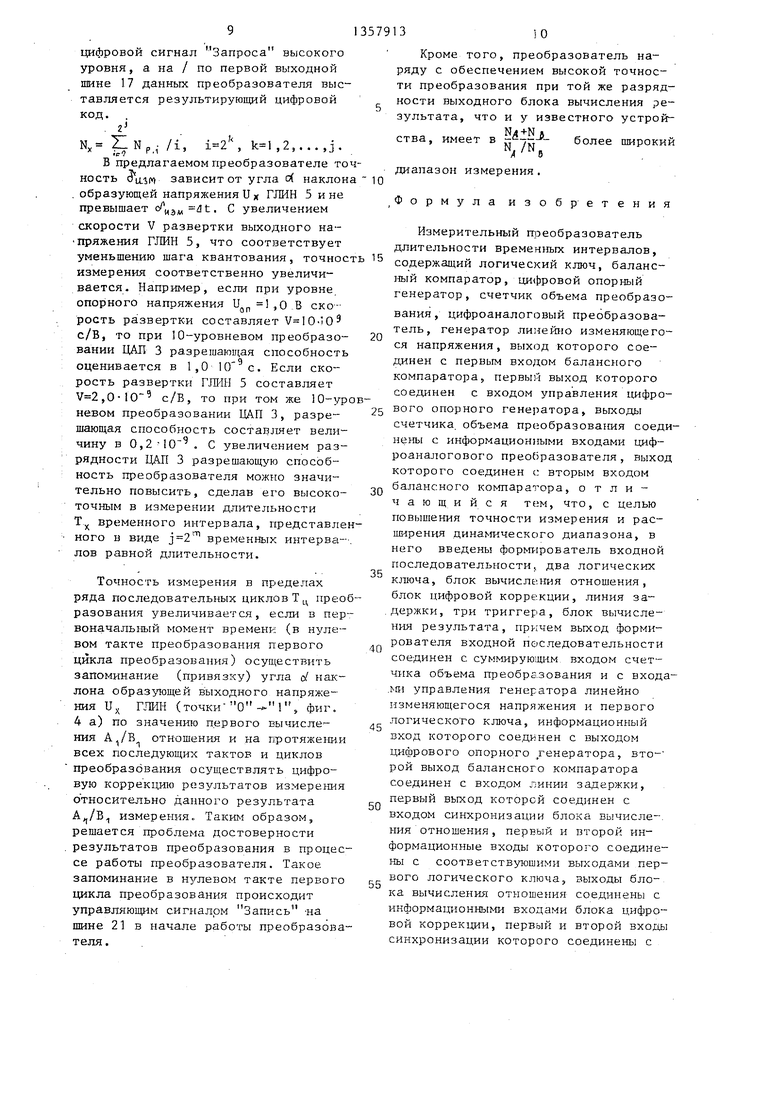

Блок 9 цифровой коррекции (фиг.2 содержит опоршлй регистр 22, основной регистр 23, цифровой компаратор 24, вычитатель 25, сумматор-вычита- тель 26, цифровой коммутатор 27.

Первый вход блоке. 9 цифровой коррекции соединен с входом синхронизации опорного регистра 22, информационные входы которого соединены с информацион Л1ми входами блока и информационными входами основного регистра 23, вход смихронизации которого соединен с вторым входом блока информационные выходы регистра 22 соединены с соответствующи ш первыми входами цифрового компаратора 24 и вычитателя 25, знаковый вход которого соединен с соответствуюыщ- ми входаш сумматора-вычитателя 26, цифрового коммутатора 27 и выходом цифрового компаратора 24, вторые информационные входы которого сое-.

динены с соответствующими выходами основного регистра 23 и соответствующими вторыми входами вычитателя 25, сумматора-вычитателя 26, цифрового коммутатора 27, информационные выходы вычитателя 25 соединены с соответствующими входами сумматора- вычитателя 26, информационные выходы которого соединены с соответствующими входами цифрового коммутатора 27, информационные выходы которого являются соответствующими выходами блока.

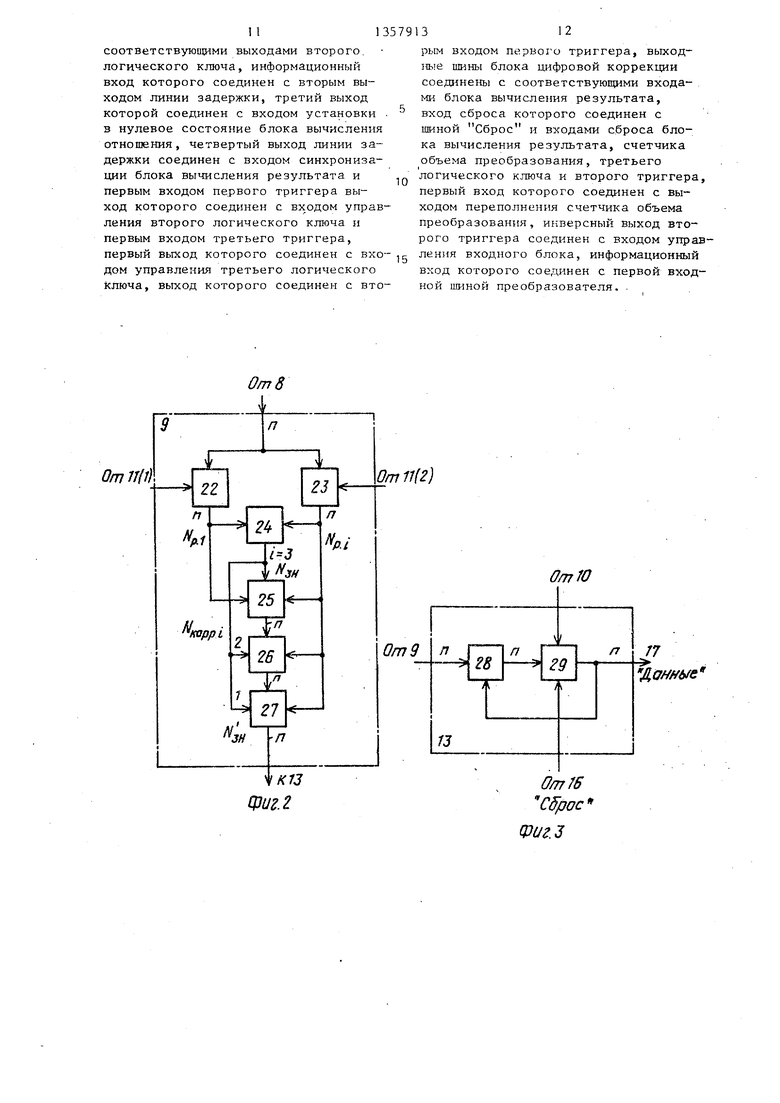

Блок 13 вычисления результата (фиг.З) содержит сумматор 28, ре- гистр 29 параллельного сдвига.Вход синхронизации блока. 13 Соединен с соответствующим входом регистра 29, вход сброса которого соединен с со- .ответствующим входом блока, информа- ционные выходы регистра 29 соединены с соответствующими выходами блока и сумматора 28, вторые входы которого соединены с соответствую- 1ЦИМИ входами блока, выход суммато- ра 28 соединен с соответствующим входом регистра 29.

Преобразователь работает следующим образом,

В исходном состоянии триггеры 12, 14 и 19 установлены в единичное состояние,, на иине 18 выставлен цифровой сигнал Запрос высокого уровня, а формирователь 1 заблокирован цифровым сигналом низкого уровня, поступающим с второго (инверсного)

выхода триггера 14 (фиг. 5 н). При поступлении по шине 21 сигнала Запись высокого уровня триггер 19 устанавливается в нулевое состояние который открывает логический ключ 20

В ответ на цифровой сигнал Запрос, воспринимаемый как готовност устройства к работе, по входной шин 16 управления устройства подается цифровой импульсный сигнал Сброс высокого уровня, по которому производится принудительная установка в исходное нулевое состояние счетчика 2 объема гфеобразования, блока 8 вычисления отношения, первого 12 и второго 14 триггеров и блока 13 вычисления результата. Перевод второго триггера 14 в нулевое состояние сопровождается снятием цифрового сигнала Запрос по выходной шине 18 запроса устройства и разблокировние формирователя 1, через который

-5 0

0 5

0

5

0

5

в этом случае могут проходить сигналы временных интервалов равной длительности (фиг. 1, фиг. 5 а-в). По цифровому управляющему сигналу низкого уровня первого триггера 12 осуществляется перевод второго логического ключа 11 в состояние, при котором цифровой импульсный сигнал .низкого уровня, поступающий на его первый информационный вход, проходит на его первый выход.

При поступлении цифрового сигнаипа временного интервала равной длительности Tj на шине 15 устройства на вход формирователя 1 на его выходе формируются цифровые сигналы временных интервалов равной длительности той же размерности, но с крутыми фронтами (логические перепады О и (фиг. 5 а-б). Так по переднему фронту цифрового сигнала временного интервала про1 зводится переключение счетчика 2 объема преобразования, при котором его содержимое увеличивается на единичн1)ГЙ квант (например, ...00 + ...01), что приводит к соответств ующему Изменению (уветшчению) опорного напряжения Np, формируемого на выходе ЦАП 3 и подаваемого на второй опорной вход балансного компаратора 4 с цифровым выходом. Кроме того, осуществляется пер еключение первого логического ключа 7, при котором цифровые информационные сигналы, поступающие на его информационный вход, проходят на его первый выход, и производится запуск ГЛИН 5, выполненного по схеме дв ухтактного интегратора. Как только его линейно возрастающее напряжение - пересечет уровень опорного напряжения (. )5 ИЗ- выходах балансного компаратора 4 формируются цифровые синфазные сигналы (фиг. 1 и. 5 Г5Д,л).

По переднему фронту цифрового сигнала, формируемого на первом (прямом) выходе балансного компаратора 4, осуществляется запуск прецизионного опорного генератора 6, цифровые импульсы которого проходят через первый логический ключ 7 на первый прямой счетный (с уммирующий) вход блока 8 вычисления отношения, формируя цифровой код N делимого (фиг. 1 и 5 г-ж,и).

По заднему фронту измеряемого временного интервала равной длительное5

ти Ту осуществляется обратное переключение первого логического ключа 7, при котором цифровые информационные сигналы по его входу могут проходит на его второй выход, а также осуществляется перевод ГЛИН 5 в режим второго этапа интегрирования (разряд). Теперь цифровые опорные

импульсы с выхода цифрового опорно

го генератора 6 проходят через первый логический ключ 7 на суммирующий вход блока 8 вычисления отношения, формируя цифровой код N. делителя (фиг. 5 г-е, з,к). Как только выход- кое линейно убывающее напряжение и ГЛШ 5 пересечет уровень опорного напряжения U ходах балансного компаратора 4 происходит смена полярности цифровых синфазных сигналов. Цифровой опорный генератор 6 останавливается.

С инверсного выхода балансного компаратора 4 цифровой сигнал (фиг. 5 л) пололсительного перепада () поступает на вход линии 10 заде15жки и задерживается соответственно по первому его выходу на

С (j,, -, ., , по второму - на

.-i , по третьему - на

о(з1 ; ;i

- .„ /il Q

, а по четвертому

на

10 (Ф)

где L; - время распрост

ранения информационного сигнала через цепи цифровых элементов. С первого выхода линии 10 задержки положительным фронтом () цифрового сигнала, поступающего на вход синхронизации блока 8 вычисления отношения, осуществляется его запуск (на фиг. 1 блок 8 не раскрыт). В блоке 8 вычисления отношения выполняется операция деления двоичных чисел по методу итерактивного вычитания делителя NJ; из делимого ,, т.е. Np.NдJ-Ngj, в результате которого получается промежуточный итоговый цифровой код.

Следовательно, выбирая соответст.вуюлще.значения огибающих линейно изменяющегося напряжения } ГЛИН 5 как Uy/iji 3/2 , где 1} - постоянная интегрирования разряда, может быть достигнуто максимальное быстродействие выполнения операции , итеiрационного деления (фиг. 1),

В следующий момент времени J g на выходах блока 8 вычисления отноше .ния выставляется Цифровой код Np результата деления, который переписы

36

вается в блок 9 цифровой коррекции - в его опорный регистр 22 (фиг. 2) по положительному фронту цифрового сигнала синхронизации, поступающего на его вход синхронизации через второй логический ключ 11 с второго выхода линии 10 задержки. В следующий момент

по положительному

0

-jg

25

0

30

35

40

50

55

фронту цифрового сигнала синхронизации по третьему выходу линии 10 задержки, поступающего на второй вход установки в нулевое состояние блока 8, производится установка в исходное состояние его буферных двоичных счетчиков делимого и делителя (данные счетчики сбрасываются в о Импульсным сигналом высокого уровня, который формируется в блоке 8 его формирователем коротких импульсов (не показано), подготавливая устройство к следующему такту преобразования (фиг. 1 и 5 а-с).

В блоке 9 цифровой коррекции (фиг. 2) выполняется комбинационная операция коррекции итогового результата преобразования текущего такта. Цифровой код Nр результата первого такта преобразования, зафиксированный в опорном регистре 22, поступает с его выходов на первые входы цифрового компаратора 24 и вы- читателя 25, на вторые их входы с выходов основного регистра 23 поступает цифровой код N р; (,3,...,j)

результата последующих тактов преобразования . В комбинационном вычита- теле 25 вычисляется цифровой код N корр; lNp, -Np;l коррекции результата с учетом знака N сравниваемых двоичных чисел. Следовательно, в рассматриваемом такте (первый такт) преобразования на выходах вычитате- ля 25 выставляется цифровой код Nj,,pp, |N р,-Np;l 1ХХ...ХХ-00, ..001 ХХ...XX, который проходит на первые информационные комбинационного сумматора-вычитателя 26. В зависимости от значения цифрового кода Njj знака (, если N р г N р,- , и , если .), поступающего на вход управления сумматора- вычитателя 26, в последнем выполняется дифференциальная операция коррекции результата. Например, если в результате i-ro такта преобразования формируется N,, означающий ,, то в результате цифровой коррекции имеем следующий итоговый

результата в данном такте преобразования: Npj . Когда при NP,:NP; , имеем М .- Np ;,, koppt +i

Скорректированный цифровой код

N

р- результата с выходов сумматоравычйтателя 26 поступает на первые ни формационные входы цифрового коммутатора 27, а на его вторые информацион ные входы поступает цифровой нескорректированный код с выходов основного регистра 23 во всех последующих тактах преобразования, кроме. первого такта преобразования. Одно- временно на управляющий вход цифрового коммутато1)а 27 поступает цифровой код коммутации, по которому организуется его работа. Например, при значениях N jn 100 и

(Np, Np- и Np,Np; ) производится переключение цифрового коммутатора 27 в состояние (режим), при котором его первые информационные входы коммутируются на его выходы, а при значении Nj 001 цифровой коммутатор 27 переводится в другое состояние (режим), при котором его вторые информационные входы коммутируются на его выходы (Np, Np.) Такой циф- ровой режим цифрового коммутатора 27 позволяет дифференцированно управлять итоговой цифровой информацией, формируя на выходах устройства достоверную измерительную информацию Таким образом, для первого такта преобразования скорректированный цифровой код N р, имеет следующее значение: N р, Np, +N корр,ХХ. . .XX+ +00. . .. . .XX и проходит с выхо- дов цифрового сумматора-вычитателя 26 через цифровой коммутатор 27 на его выходы (фиг. 2).

В следующий момент через время . на четвертом выходе линии 10 за- держки выставляется цифровой сигнал высокого уровня, по переднему фронту которого производится перепись скорректированного цифрового кода N „ результата с выходов блока 9 цифровой коррекции по суммирующему информационному входу в блок 13 вычисления результата, выполненного по схеме накапливающего сумматора на комбинационном сумматоре 28 и регистре 29 параллельного сдвига (фиг. 3), а также производится переключение в единичное состояние первого триггера 12, выходной цифровой сигнал высокого уровня которого производит переключение входов-выходов второго логического ключа 11 и установку в единичное исходное состояние триггера 19. Переключение ключа 11 в указанное состояние производится только в первом такте преобразования каждого последующего цикла преобразования, состоящих из тактов. С этого момента все цифровые сигналы синхронизации, поступающие в последующих тактах преобразования, проходят с входа второго логического ключа 11 на его второй выход. На этом первый такт преобразования за- вершается и преобразователь подготовлен к очередному такту преобразования (фиг. 1 и 5 а-с).

С приходом очередного цифрового сигнала временного интервала равной длительности Ту по первой входной информационной шине 15 устройства на вход формирователя 1 по его переднему фронту производится, как и в предыдущем такте преобразования, увеличение на единичный квант содержимого счетчика 2 объема преобразования, переключение первого логического ключа 7 и запуск ГЛИН 5. Увеличение содержимого счетчика 2 объема преобразования проводит к изменению (увеличению) опорного па- пряжения U|j на выходе ЦАП 3, что приводит к тому, что запуск цифрового опорного генератора 6 задерживаеся на интервал времени , где q - квант напряжения, соответствующий младшему разряду ЦАП 3; V - скорость изменения выходного -напряжения ГЛИН 5. Далее весь процесс преобразования повторяется аналогично.

Таким образом, за полный цикл преобразования, задаваемого счетчика 2 объема преобразования 2 Тр, где Т f. - длительность развертки ГЛИН 5; га - разрядность счетчика 2 объема преобразования, на его втором выходе формируется цифровой сигнал Цикл высокого уровня., по .. .переднему фронту которого переводится второй триггер 14. Цифровой сигнал низкого ТТЛ-уровня по второму (инверсному) выходу этого триггера блокирует формирователь 1, а по его первому (прямому) выходу |Противофазный цифровой сигнал поступает на вторую выходную щину 18 запроса устройства и формирует

цифровой сигнал Запроса высокого уровня, а на / по первой выходной шине 17 данных преобразователя выставляется результирующий цифровой код. . 2 N, |1 NP,. /i, ,2,...,j.

В предлагаемом преобразователе тоность ou. iM зависит от угла сХ наклон

. образующей напряжения Ux ГЛИН 5 и не превышает С увеличением скорости V развертки выход 1ого на пряжения ГЛИН 5, что соответствует уменьшению шага квантования, точнос измерения соответственно увеличивается. Например, если при уровне опорного напряжения Ugj,l,0,B скорость развертки составляет V 10)О с/В, то при 0-уровневом преобразо- вании ЦДЛ 3 разрешающая способность оценивается в 1,0 . Если скорость развертки ГЛИН 5 составляет , с/В, то при том же 10-ур невом преобразовании ЦАП 3, разрешающая способность составляет величину в 0,2 -10 . С увеличением разрядности ЦДЛ 3 разрешающую способность преобразователя можно значительно повысить, сделав его высоко- точным в измерении длительности T-j временного интервала, представленого в виде временных интервалов равной длительности.

Точность измерения в пределах

ряда последовательных циклов Т преоразования увеличивается, если в первоначальный момент времени (в нулевом такте преобразования первого цикла преобразования) осуществить запоминание (привязку) угла с/ наклона образующей выходного напряже

ния Uj ГЛИН (точки- О - 1, фиг, 4 а) по значению первого вычисле- ния отношения и на гфотяже1ш.и всех последующих тактов и циклов преобразования осуществлять цифровую коррекцию результатов измерения относительно данного результата , измерения., Такиь образом, решается проблема достоверности результатов преобразования в процессе работы преобразователя. Такое запоминание в нулевом такте первого цикла преобразования происходит управляющим сигналом Запись -на шине 21 в начале работы преобразователя.

Кроме того, преобразователь наряду с обеспечением высокой точности преобразования при той же разрядности выходного блока вычисления результата, что и у известного устрой- N(lNj

ства, имеет в ,-т--

диапазон измерения.

более широкий

0

5

0

5

5 g g

Формула изобретения

Измерительный треобразователь длительности apeMeHiaix интервалов, содержащий логический ключ, баланс- ый компаратор, цифровой опорный генератор, счетчик объема преобразования, цифроаналоговый преобразователь, генератор линейно изменяющегося напряжения, выход которого соединен с первым входом балансного компаратора, первый выход которого соединен с входом управления цифрового опорного генератора, выходы счетчика, объема преобразования соединены с информационными входами циф- роаналогового преобразователя, выход которого соединен с вторым входом балансного компаратора, отличающийся тем, что, с целью повышения точности измерения и расширения динамического диапазона, в него введены формирователь входной последовательности; два логических ключа, блок вычисления отношения, блок цифровой коррекции, линия задержки, три триггера, блок вычисления результата, причем выход формирователя входной последовательности соединен с суммирующим входом счетчика объема преобразования и с входа- ш управления генератора линейно изменяющегося напряжения и первого логического ключа, информационный вход которого соединен с выходом цифрового опорного генератора, вто- рой выход балансного компаратора соединен с входом линии задержки, первый выход которой соединен с входом синхронизации блока вычисле-. ния отношения, первый и второй информационные входы которого соединены с соответствующими выходами первого логического ключа, выходы блока вычисления отношения соединены с информационными входами блока цифровой коррек1дии, первый и второй входы синхронизации которого соединены с

1113

соответствуюихими выходами второго. логического ключа, информационный вход которого соединен с вторым выходом линии задержки, третий выход которой соединен с входом установки в нулевое состояние блока вычисления отношения, четвертый выход линии задержки соединен с входом синхронизации блока вычисления результата и первым входом первого триггера выход которого соединен с управления второго логического ключа и первым входом третьего триггера, первый выход которого соединен с входом управления третьего логического ключа, выход которого соединен с втоОт /////

312

рым входом первох о триггера, выходные шины блока ц фровой коррекции соед1 нены с соответствующими входами блока вычисления результата, вход сброса которого соединен с шиной Сброс и входами сброса блока вычисления результата, счетчика объема преобразования, третьего логического ключа и второго триггера первый вход которого соединен с выходом переполнения счетчика объема преобразования, инверсный выход второго триггера соединен с входом управления входного блока, информационный вход которого соединен с первой входной шиной преобразователя. .

Ланные

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь линейного перемещения в код | 1984 |

|

SU1274156A1 |

| Измерительный преобразователь длительности временных интервалов | 1988 |

|

SU1651268A1 |

| УЛЬТРАЗВУКОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЙ | 1991 |

|

RU2035692C1 |

| УЛЬТРАЗВУКОВОЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА НАКЛОНА | 1991 |

|

RU2075728C1 |

| Ультразвуковой измеритель перемещений | 1989 |

|

SU1619027A1 |

| УЛЬТРАЗВУКОВОЙ ПРЕОБРАЗОВАТЕЛЬ ЛИНЕЙНЫХ ПЕРЕМЕЩЕНИЙ | 1991 |

|

RU2011294C1 |

| Цифровой преобразователь для измерения частоты следования импульсов | 1985 |

|

SU1298677A1 |

| Ультразвуковой измерительный преобразователь параметров движения | 1988 |

|

SU1613855A1 |

| Ультразвуковой измеритель линейных перемещений | 1989 |

|

SU1645812A1 |

| Цифровой измеритель длительности временных интервалов | 1985 |

|

SU1381419A1 |

Изобретение относится к импульсной технике в частности к устройствам для измерения временных интервалов. Цель изобретения - повышение точности измерений и расширение динамического диапазона. Цель достигается за счет введения в устройство формирователя 1 выходной последовательности, двух логических ключей 7 и 1 I, блока 8 вычисления отношения , „Наклон А rff15 С5pa с BpefieHHOi} интервал „Цикл „ 2Г-- :, 18 „Запрос блока 9 цифровой коррекции, линии 10 задержки, триггеров 12, 14 и 19 и блока 13 вычисления результата. Кроме того, устройство содержит счетчик 2 объема преобразования, цифроаналоговый преобразователь 3, балансный компаратор 4, генератор 5 линейно изменяющегося напряжения, цифровой опорный генератор 6, входную шину 15, шину 16 Сброс, п - выходных шин 17 Данные, шину 18 Запрос, логический ключ 20, шину 2 Запись. В устройстве обеспечивается получение достоверных результатов преобразования в процессе работы. Кроме того, при той же разрядности выходного блока вычисления результата, что и в прототипе, устройство обеспечивает более широкий диапазон измерений. 5 ил. а s (Л / / т оо ел со со : f /7 / /7 Ц 77 .Данные (ригЛ

| Измеритель временных интервалов | 1982 |

|

SU1034011A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-12-07—Публикация

1985-08-09—Подача