Изобретение относится к измерительной технике и может быть использовано в системах преобразования информации .

Цель изобретения - упрощение преобразователя.

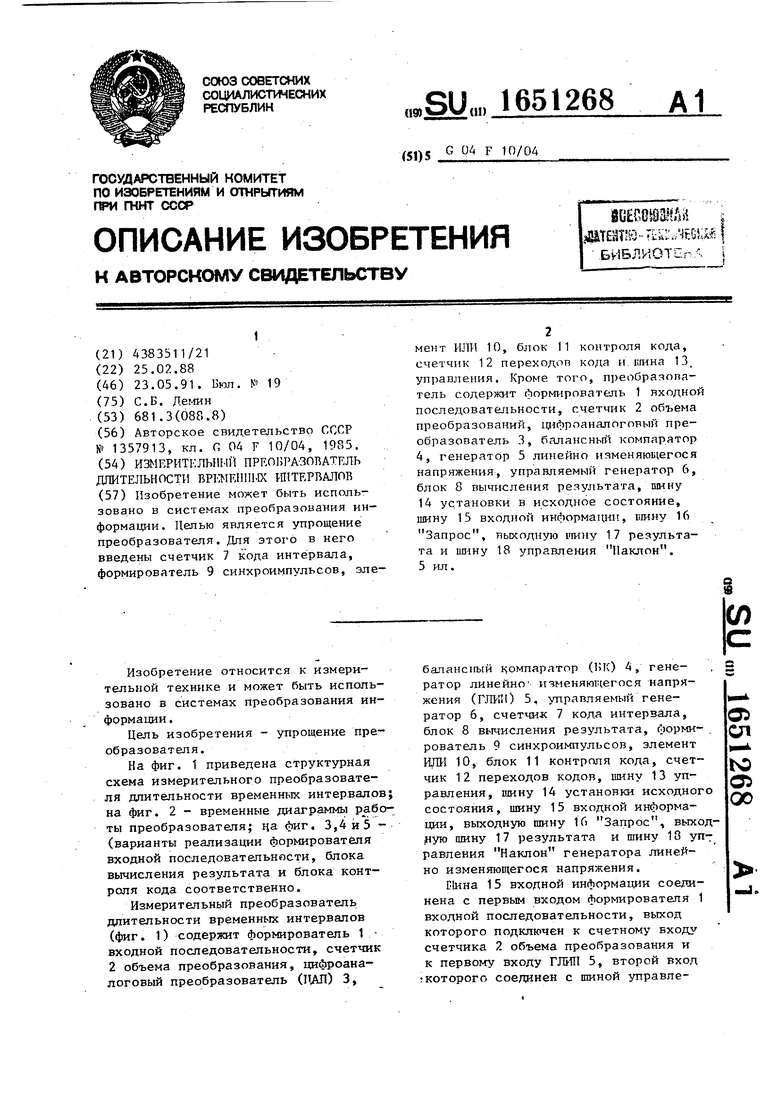

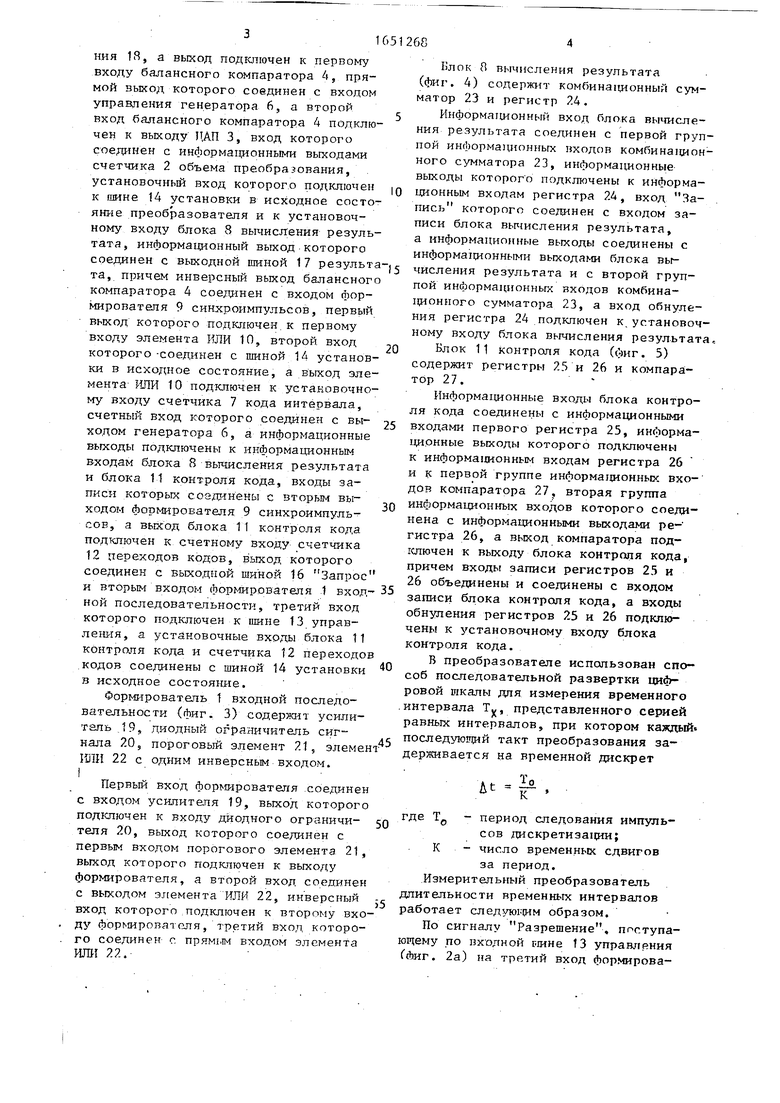

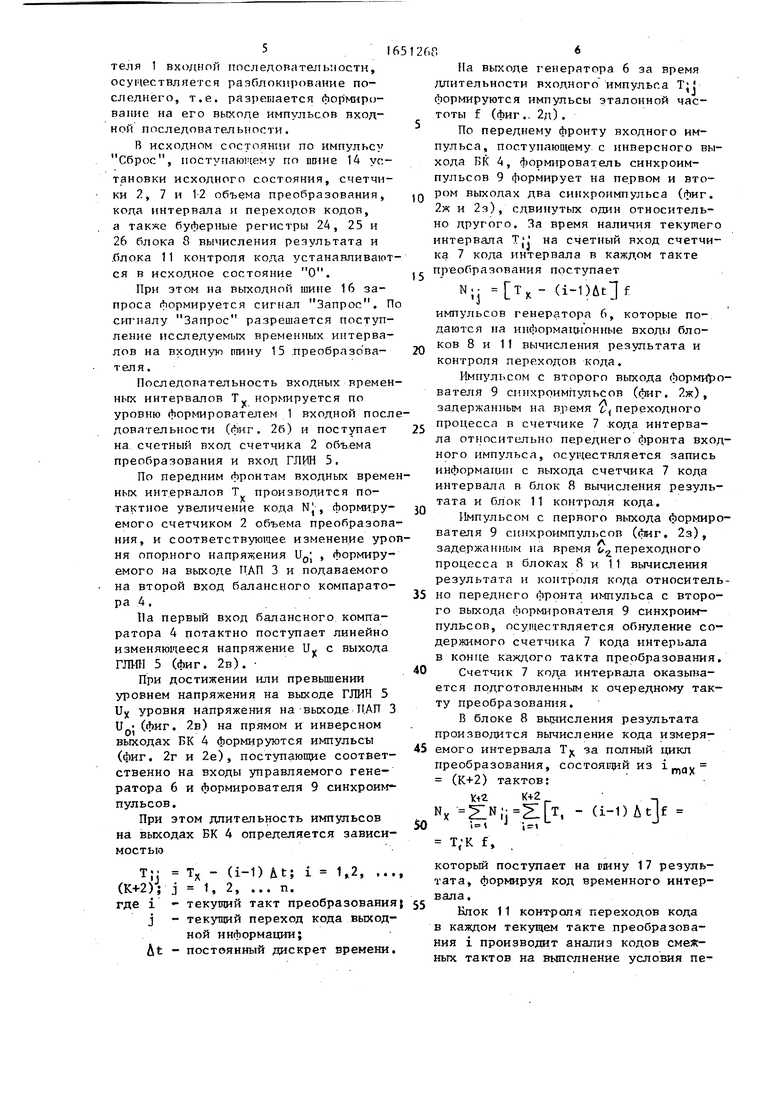

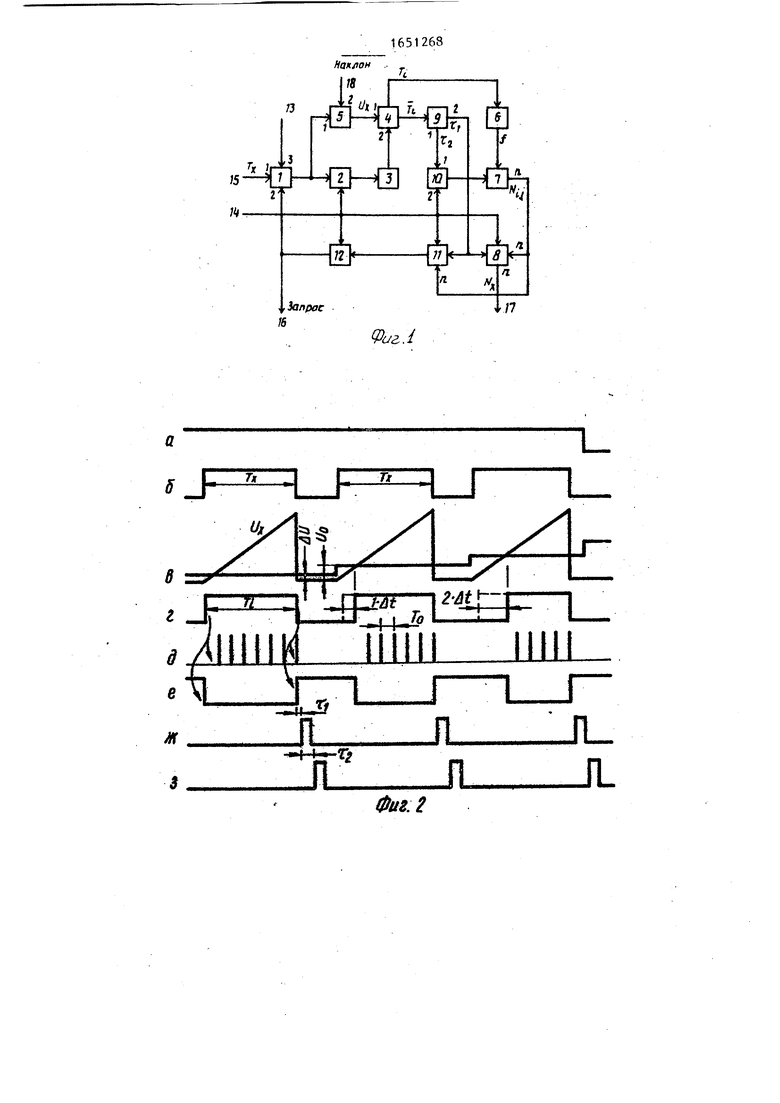

На фиг. 1 приведена структурная схема измерительного преобразователя длительности временных интервалов; на фиг. 2 - временные диаграммы работы преобразователя; ца фиг. 3,4 и 5 - (варианты реализации формирователя входной последовательности, блока вычисления результата и блока контроля кода соответственно.

Измерительный преобразователь длительности временных интервалов (фиг. 1) содержит формирователь 1 - входной последовательности, счетчик 2 объема преобразования, цифроаналоговый преобразователь (ПДП) 3,

баланс гый компаратор (15К) 4, генератор линейно1 изменяющегося напряжения (ГЛИН) 5. управляемый генератор 6, счетчи-к 7 кода интерзала, блок 8 вычисления результата, формирователь 9 синхроимпульсов, элемент ИЛИ 10, блок 11 контроля кода, счетчик 12 переходов кодов, шину 13 управления, шину 14 установки исходного состояния, шину 15 входной информации, выходную шину 1C) Запрос, выход- рую шину 17 результата и шину 18 уп-: равления Наклон генератора линейно изменяющегося напряжения.

Иина 15 входной информации соединена с первым входом формирователя 1 входной последовательности, выход которого подключен к счетному входу счетчика 2 объема преобразования и к первому входу ГЛИН 5, второй вход которого соединен с шиной управле05

ел ю

СП) 00

J1

ния , а выход подключен к первому входу балансного компаратора 4, прямой выход которого соединен с входом управления генератора 6, а второй вход балансного компаратора 4 подключен к выходу ЦАП 3, вход которого соединен с информационными выходами счетчика 2 объема преобразования, установочный вход которого подключен к шине 14 установки в исходное состояние преобразователя и к установочному входу блока 8 вычисления результата , информационный выход которого

Информационный вход блока вычисле ния результата соединен с первой гру пой информационных входов комбинацио ного сумматора 23, информационные выходы которого подключены к информа ционным входам регистра 24, вход За пись которого соединен с входом записи блока вычисления результата, а информационные выходы соединены с информационными выходами блока высоединен с выходной шиной 17 результа-(5 числения результата и с второй груп20

25

30

та, причем инверсный выход балансного компаратора 4 соединен с входом формирователя 9 синхроимпульсов, первый выход которого подключен к первому входу элемента ИЛИ 10, второй вход которого-соединен с шиной 14 установки в исходное состояние, а выход элемента ИЛИ 10 подключен к установочному входу счетчика 7 кода интервала, счетный вход которого соединен с выходом генератора 6, а информационные выходы подключены к информационным входам блока 8 вычисления результата и блока 11 контроля кода, входы записи которых соединены с вторым выходом формирователя 9 синхроимпульсов, а выход блока 1I контроля кода подключен к счетному входу счетчика 12 переходов кодов, выход которого соединен с выходной шиной 16 Запрос и вторым входом формирователя 1 вход- 35 ной последовательности, третий вход которого подключен к шине 13 управления, а установочные входы блока 11 контроля кода и счетчика 12 переходов кодов соединены с шиной 14 установки в исходное состояние.

Формирователь 1 входной последовательности (фиг. 3) содержит усилитель 19, диодный ограничитель сигнала 20, пороговый элемент 21, элемент 1ШИ 22 с одним инверсным входом

40

„45

пой информационных входов комбинационного сумматора 23, а вход обнуле ния регистра 24 подключен к,установо ному входу блока вычисления результа

Блок 11 контроля кода (фиг. 5) содержит регистры 25 и 26 и компаратор 27.

Информационные входы блока контроля кода соединены с информационными входами первого регистра 25, информационные выходы которого подключены к информационным входам регистра 26 и к первой группе информационных входов компаратора 27, вторая группа информационных входов которого соеди- иена с информационными выходами регистра 26, а выход компаратора подключен к выходу блока контроля кода, причем входы записи регистров 25 и 26 объединены и соединены с входом записи блока контроля кода, а входы обнуления регистров 25 и 26 подключены к установочному входу блока контроля кода.

В преобразователе использован способ последовательной развертки цифровой шкалы для измерения временного интервала Ту, представленного серией равных интервалов, при котором каждый последуюищй такт преобразования задерживается на временной дискрет

At - Iu At R ,

Первый вход формирователя соединен с входом усилителя 19, выход которого подключен к входу диодного ограничи- теля 20, выход которого соединен с первым входом порогового элемента 21, выход которого подключен к выходу формирователя, а второй вход соединен с выходом элемента ИЛИ 22, инверсный вход которого подключен к второму входу формирователя, третий вход которого соединен с прямым входом элемента ИЛИ 22.

15лок 8 вычисления результата (фиг. 4) содержит комбинационный сумматор 23 и регистр 24.

Информационный вход блока вычисления результата соединен с первой группой информационных входов комбинационного сумматора 23, информационные выходы которого подключены к информационным входам регистра 24, вход Запись которого соединен с входом записи блока вычисления результата, а информационные выходы соединены с информационными выходами блока вычисления результата и с второй груп0

5

0

5

0

5

0

пой информационных входов комбинационного сумматора 23, а вход обнуления регистра 24 подключен к,установочному входу блока вычисления результата,

Блок 11 контроля кода (фиг. 5) содержит регистры 25 и 26 и компаратор 27.

Информационные входы блока контроля кода соединены с информационными входами первого регистра 25, информационные выходы которого подключены к информационным входам регистра 26 и к первой группе информационных входов компаратора 27, вторая группа информационных входов которого соеди- иена с информационными выходами регистра 26, а выход компаратора подключен к выходу блока контроля кода, причем входы записи регистров 25 и 26 объединены и соединены с входом записи блока контроля кода, а входы обнуления регистров 25 и 26 подключены к установочному входу блока контроля кода.

В преобразователе использован способ последовательной развертки цифровой шкалы для измерения временного интервала Ту, представленного серией равных интервалов, при котором каждый последуюищй такт преобразования задерживается на временной дискрет

At - Iu At R ,

где Т0 - период следования импульсов дискретизации; К - число временных сдвигов

за период.

Измерительный преобразователь длительности временных интервалов работает следующим образом.

По сигналу Разрешение, поступающему по входной шине 13 управления (Лиг. 2а) на третий вход Формирова516

теля 1 входной последовательности, осуществляется разблокирование последнего, т.е. разрешается формирование на его выходе импульсов входной последовательности.

R исходном состоянии по импульсу Сброс, поступающему по шине 14 установки исходного состояния, счетчики 2, 7 и 12 объема преобразования, кода интервала и переходов кодов, а также буферные регистры 24, 25 и 26 блока 8 вычисления результата и блока 11 контроля кода устанавливаются в исходное состояние О.

При этом на выходной шине 16 запроса Нормируется сигнал Запрос. П сигналу Запрос разрешается поступление исследуемых временных интервалов на входную шину 15 преобразователя.

Последовательность входных временных интервалов Т„ нормируется по уровню формирователем 1 входной послдовательности (фиг. 26) и поступает на счетный вход счетчика 2 объема преобразования и вход ГЛИН 5.

По передним фронтам входных временых интервалов Т производится по- тактное увеличение кода N, формируемого счетчиком 2 объема преобразования, и соответствующее изменение уроня опорного напряжения U0j , формируемого на выходе ПАП 3 и подаваемого на второй вход балансного компаратора 4.

На первый вход балансного компаратора 4 потактно поступает линейно изменяющееся напряжение U с выхода ГЛИН 5 (фиг. 2в).

При достижении или превышении уровнем напряжения на выходе ГЛИН 5 Uj( уровня напряжения на выходе ПАП 3 U (Фиг. 2в) на прямом и инверсном выходах БК 4 формируются импульсы (фиг. 2г и 2е), поступающие соответственно на входы управляемого генератора 6 и Формирователя 9 синхроимпульсов.

При этом длительность импульсов на выходах БК 4 определяется зависимостью

TJJ (K+2)J; j

Тх - (i-1) &t; i 1,2, 1, 2, ... n.

где i - текущий такт преобразования; j - текущий переход кода выходной информации; At - постоянный дискрет времени.

0

5

0

268

На выходе генератора 6 за время длительности входного импульса Т;{ формируются импульсы эталонной частоты f (фиг. 2д).

По переднему фронту входного импульса, поступающему с инверсного выхода ПК 4, формирователь синхроимпульсов 9 формирует на первом и втором выходах два синхроимпульса (фиг. 2ж и 2з), сдвинутых один относительно другого. За время наличия текущего интервала Tjj на счетный вход счетчика 7 кода интервала в каждом такте преобразования поступает

Nlj CTx- (i-1) импульсов генератора 6, которые подаются на информационные входы блоков 8 и 11 вычисления результата и контроля переходов кода.

Импульсом с второго выхода формирователя 9 синхроимпульсов (фиг. 2ж), задержанным на время с(переходного процесса в счетчике 7 кода интервала относительно переднего фронта входного импульса, осуществляется запись информации с выхода счетчика 7 кода интервала в блок 8 вычисления результата и блок 11 контроля кода.

Импульсом с первого выхода формирователя 9 синхроимпульсов (фиг. 2з), задержанным на время С2переходного процесса в блоках 8 и 11 вычисления результата и контроля кода относитель5 но переднего фронта импульса с второго выхода формирователя 9 синхроимпульсов, осуществляется обнуление содержимого счетчика 7 кода интерьала в конце каждого такта преобразования.

0 Счетчик 7 кода интервала оказывается подготовленным к очередному такту преобразования.

В блоке 8 вычисления результата производится вычисление кода измеря5 емого интервала Т за полный цикл преобразования, состоящий из i Оу (К+2) тактов: Vi2 К+2.

5

0

0

5

1ЛЈ. .

NX -ZNjj-ZLT, - (i-DAtJf

J

T;K f, ,

который поступает на щину 17 результата, формируя код временного интервала.

Блок 11 контроля переходов кода в каждом текущем такте преобразования i производит анализ кодов смежных тактов на выполнение условия перехода по его числовому значению

N

1,J +

1, 2

Число переходов кодов j регистрируется счетчиком 12 переходов кодов при достижении значения

n j 2

на соответствующем выходе счетчика 12 формируется импульс, которым по второму входу блокируется вход формирователя 1 входной последовательности.

При этом процесс преобразования прекращается и режим измерения считается завершенным.

По шинам 17 и 16 будут выставлены результирующий код Nx., пропорциональный длительности измеряемого интервала, и импульс Запрос соответственно.

Преобразователь оказывается в режи- ме ожидания и может быть запущен с приходом очередного импульса Сброс по шине 14 установки исходного состояния и поступлением входного временного интервала по шине 15 входной информации. Далее процесс измерения осуществляется в соответствии с изложенным алгоритмом.

Преобразователь может быть принудительно остановлен при.снятии сигнала Разрешение, поступающего по шине 13 управления.

С целью регулирования величины временного дискрета задержки &t по иине 18 управления на вход генератора 5 линейно изменяющегося напряжения подается сигнал Наклон, позволющий устанавливать необходимую скорость v нарастания линейно изменяющегося напряжения .Uy.

Изобретение позволяет решать поставленную задачу с использованием меньших аппаратурных затрат.

Формула изобретения

Измерительный преобразователь длительности временных интервалов, содержащий формирователь входной последовательности, счетчик объема преобразований, цифроаналоговый преобразователь, балансный компаратор, генератор линейно изменяющегося на пряжения, управляемый генератор, бпм вычисления результата, выходную шину результата, ггину Запрос1, тину ус

5

0

5

тановки в исходное состояние, шину управления Наклон генератора линейно изменяющегося напряжения, шину входной информации, соединенную с первым входом формирователя входной последовательности, выход которого подключен к счетному входу счетчика объема преобразования и к первому входу генератора линейно изменяющегося напряжения, второй вход которого соединен с шиной управления, а выход подключен к первому входу балансного компаратора, первый выход которого соединен с входом управления управляемого генератора, а второй вход балансного компаратора подключен к выходу цифроанапогового преобразователя, вход которого соединен с информационными выходами счетчика объема преобразования, установочный вход которого подключен к шине установки в исходное состояние преобразователя и установочному входу блока вычисления результата, информационный выход которого соединен с выходной шиной результата, отличающийся тем, что, с целью упрощения преобразователя, в него дополнительно введены счетчик кода интервала, формирователь синхроимпульсов, элемент ИЛИ, блок контроля кода, счетчик переходов кода и шина управления, причем выход балансного компаратора соединен с входом формирователя синхроимпульсов, первый выход которого подключен к первому входу элемента ИЛИ, второй вход которого соединен с шиной установки в исходное состояние преобразователя, а выход элемента ИЛИ подключен к установочному входу счетчика кода интервала, счетный вход которого соединен с выходом управляемого генератора, а информационные выходы подключены к ин- 5 формационным входам блока вычисления результата и блока контроля кода, входы записи которых соединены с вторым выходом формирователя синхроимпульсов, а выход блока контроля кода подключен к счетному входу счетчика переходов кодов,выход которого соединен с выходной шиной Запрос и вторым входом формирователя входной последовательности, третий вход которого подключен к иине управления, а установочные входы блока контроля кода и счетчика переходов кодов соединены с шиной установки в исходное состояние.

0

5

0

0

5

Наклон

| название | год | авторы | номер документа |

|---|---|---|---|

| Измерительный преобразователь длительности временных интервалов | 1985 |

|

SU1357913A1 |

| Преобразователь линейного перемещения в код | 1984 |

|

SU1274156A1 |

| Преобразователь скорости линейного перемещения | 1986 |

|

SU1437998A1 |

| УЛЬТРАЗВУКОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЙ | 1991 |

|

RU2035692C1 |

| Цифровой измеритель длительности временных интервалов | 1985 |

|

SU1381419A1 |

| УЛЬТРАЗВУКОВОЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА НАКЛОНА | 1991 |

|

RU2075728C1 |

| Ультразвуковой измеритель перемещений | 1989 |

|

SU1619027A1 |

| Преобразователь линейных перемещений (его варианты) | 1985 |

|

SU1285631A1 |

| Измерительный преобразователь линейных перемещений | 1987 |

|

SU1504507A1 |

| УЛЬТРАЗВУКОВОЙ ПРЕОБРАЗОВАТЕЛЬ ЛИНЕЙНЫХ ПЕРЕМЕЩЕНИЙ | 1991 |

|

RU2011294C1 |

Изобретение может быть использовано в системах преобразования информации. Целью является упрощение преобразователя. Для этого в него введены счетчик 7 кода интервала, формирователь 9 синхроимпульсов, элемент ИЛИ 10, блок 11 контроля кода, счетчик 12 переходов кода и шина 13, управления. Кроме того, преобразопа- тель содержит формирователь 1 входной последовательности, счетчик 2 объема преобразований, цифроаналоговый преобразователь 3, балансный компаратор 4, генератор 5 линейно изменяющегося напряжения, управляемый генератор 6, блок 8 вычисления результата, шину 14 установки в исходное состояние, шину 15 входной информации, шину 16 Запрос, выходную тину 17 результата и шину 18 управления Наклон. 5 ил.

L

Ь

ч

жй

ЈЕШ-р41Ј:

I I /Q II

-И

illill

Ж

JT1

-Z&-3

n

3

П

ФигА

Ш-р41Ј:

I I /Q II

-И

illill ilHI

Jl

JL

Фиг. 2

Фиг.З

ФигЛ

Редактор О. Стенина

Составитель Ю. Шишкин

Техред М.ДидьжКорректор Л. Патай

Заказ 1901

Тираж 274

ВИНИЛИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Lli

-f

Фиг. 5

Подписное

| Измерительный преобразователь длительности временных интервалов | 1985 |

|

SU1357913A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-05-23—Публикация

1988-02-25—Подача