7/

74

(Л

Изобретение относится к измерительным преобразователям временных интервалов в цифровой код и может быть использовано в цифровых системах преобразования формы информации. Изобретение позволяет повысить точность и быстродействие выполняемых измерений. Для этого в цифровой измеритель, содержащий многоканальный генератор 2, регистры 7 и 8, триггер 10 управления, шину 11 запуска устройства, выходную шину 12 запроса, входную шину 13 управления, входную шину 14 и выходные шины данных 15 и блокирования записи 16, дополнительно введе.чы входной блок 1, регистры 3 и 4, сумматор 5, элемент 6 задержки и цифровой компаратор 9. Работа устройства может быть принудительно прекра щепа при снятии цифрового сигнала «Разрешение на шине управления устройства. I ил.

со 00

Изобретение относится к измерительной и вычислительной технике, а именно к измерительным преобразователям временных интервалов в цифровой код, и может быть использовано в цифровых системах преобразования формы информации.

Цель изобретения - повышение точности быстродействия измерений.

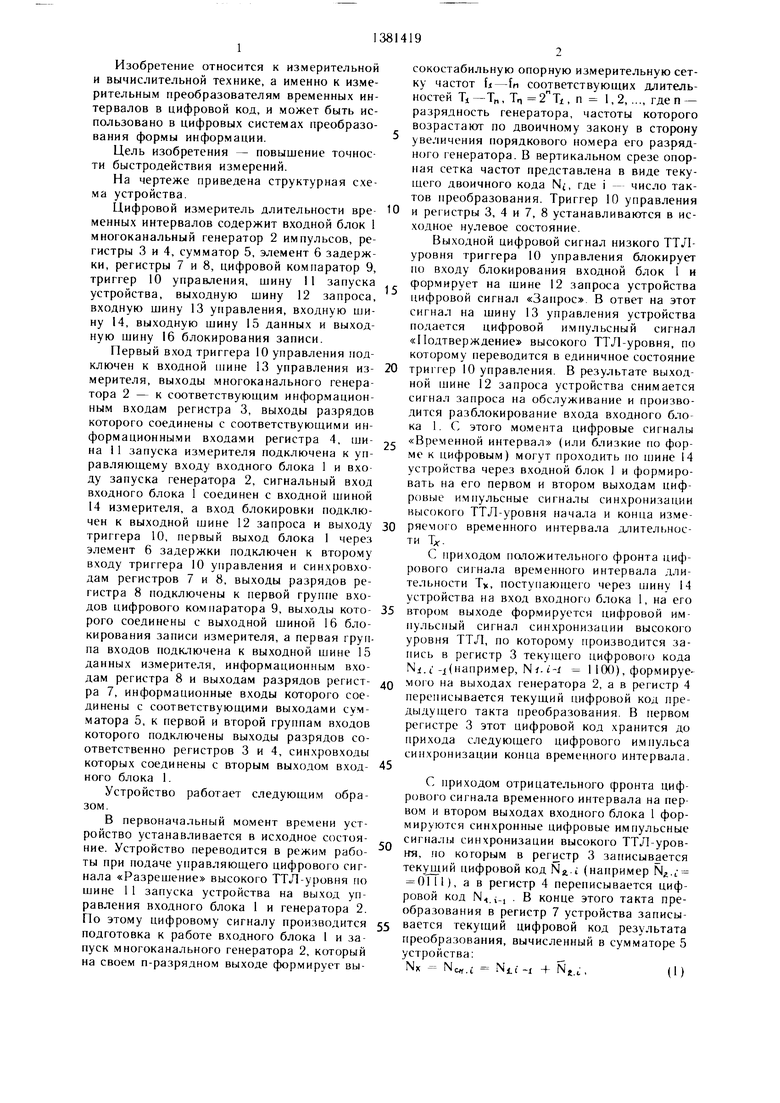

На чертеже приведена структурная схема устройства.

Цифровой измеритель длительности вре- менных интервалов содержит входной блок 1 многоканальный генератор 2 импульсов, регистры 3 и 4, сумматор 5, элемент 6 задержки, регистры 7 и 8, цифровой компаратор 9, триггер 10 управления, шину 11 запуска устройства, выходную шину 12 запроса, входную шину 13 управления, входную шину 14, выходную шину 15 данных и выходную шину 16 блокирования записи.

Первый вход триггера 10 управления подключен к входной шине 13 управления из- мерителя, выходы многоканального генератора 2 - к соответствуюшим информационным входам регистра 3, выходы разрядов которого соединены с соответствуюш.ими информационными входами регистра 4, ши- на 11 запуска измерителя подключена к уп- равляюшему входу входного блока 1 и входу запуска генератора 2, сигнальный вход входного блока 1 соединен с входной шиной 14 измерителя, а вход блокировки подключен к выходной шине 12 запроса и выходу триггера 10, первый выход блока I через элемент 6 задержки подключен к второму входу триггера 10 управления и синхровхо- дам регистров 7 и 8, выходы разрядов регистра 8 подключены к первой группе входов цифрового компаратора 9, выходы кото- рого соединены с выходной шиной 16 блокирования записи измерителя, а первая группа входов нoдKv Iючeнa к выходной шине 15 данных измерителя, информационным входам регистра 8 и выходам разрядов регист- ра 7, информационные входы которого соединены с соответствуюшими выходами сумматора 5, к первой и второй группам входов которого подключены выходы разрядов соответственно регистров 3 и 4, синхровходы которых соединены с вторым выходом вход- ного блока 1.

Устройство работает следующим образом.

В первоначальный момент времени устройство устанавливается в исходное состояние. Устройство переводится в режим рабо- ты при подаче управляющего цифрового сигнала «Разрешение высокого TT/I-уровня по щине 1 1 запуска устройства на выход управления входного блока 1 и генератора 2. Цо этому цифровому сигналу производится подготовка к работе входного блока I и запуск многоканального генератора 2, который на своем п-разрядном выходе формирует высокостабильную опорную измерительную сетку частот ii-ffi соответствующих длительностей TI -Тр, Тп , п 1,2, ..., где п - разрядность генератора, частоты которого возрастают по двоичному закону в сторону увеличения порядкового номера его разрядного генератора. В вертикальном срезе опорная сетка частот представлена в виде текущего двоичного кода Nj, где i - число тактов преобразования. Триггер 10 управления и регистры 3, 4 и 7, 8 устанавливаются в исходное нулевое состояние.

Выходной цифровой сигнал низкого ТТЛ- уровня триггера 10 управления блокирует по в.ходу блокирования входной блок 1 и формирует на шине 12 запроса устройства цифровой сигнал «Запрос. В ответ на этот сигнал на щину 13 управления устройства подается цифровой импульсный сигнал «Подтверждение высокого ТТЛ-уровня, по которому переводится в единичное состояние триггер 10 управления. В результате выходной шине 12 запроса устройства снимается сигнал запроса на обслуживание и производится разблокирование входа входного блока 1. С этого момента цифровые сигналы «Временной интервал (или близкие по форме к цифровым) могут проходить по шине 14 устройства через входной блок 1 и формировать на его первом и втором выходам цифровые импульсные сигналы синхронизации высокого ТТЛ-уровня начала и конца изме- ряе 101 о временного интервала длительности TXС приходом патожителыюго фронта цифрового сигнала временного интервала длительности Ту, поступающего через шину 14 устройства на вход вxoднoг(J блока 1, на его втором выходе формируется цифровой импульсный сигнал син.хронизации высокого уровня ТТЛ, по которо.му производится запись в регистр 3 текушего цифрового кода Ni. t-(например, N. i-i 1 10()), формируемою на выходах генератора 2, а в регистр 4 переписывается текущий цифровой код предыдущего такта преобразования. В первом регистре 3 этот цифровой код хранится до прихода следующего цифрового импульса синхронизации конца временного интервала.

С приходом отрицательного фронта цифрового сигнала временного интервала на первом и втором выходах входного блока 1 формируются синхронные цифровые импульсные сигналы синхронизации высокого ТТЛ-уров- ня, по когорым в регистр 3 записывается текущий цифровой код N.i (например Ыд.

0111), а в регистр 4 переписывается цифровой код N.i-i . В конце этого такта преобразования в регистр 7 устройства записывается текущий цифровой код результата преобразования, вычисленный в сумматоре 5 устройства:

NX NC«. Li-i + Nj.,,(1)

где N art.i; - цифровой код преобразования на выходах сумматора 5 устройства.

В регистр 8 одновременно переписывается текущий цифровой код N результата предыдущего такта преобразования. С выходов регистров 7 и 8 цифровые коды Nn и ч; поступают на соответствующие входы цифрового компаратора 9, в котором выполняется анализ на их равенство, при котором на его выходе равенства формируется цифровой сигнал «Блокирование записи высокого ТТЛ-уровня, проходящий на тину 16 блокирования записи устройства.

С выходов регистра 7 текущий цифровой код N lf результата преобразования поступает на щину 15 данных устройства, формируя выходную цифровую информацию «Данные В конце данного текущего такта преобразования осуществляется перевод триггера 10 управления в исходное нулевое состояние, что приводит к формированию на тине 12 запроса устройства цифрового сигнала «Запрос и блокированию входа вход ного блока 1 устройства. На этом цикл преобразования заканчивается. Устройство го- тово к очередному циклу преобразования, который выполняется аналогично рассмотренному и согласно (1). Частота регенера ии выходной цифровой информации на интерфейсных шинах устройства определяется частотой следования цифровых сигналов временных интервалов длительности Т и быстродействием внещнего устройства управления.

Наличие элемента 6 задержки в устройстве позволяет в пределах текущего такта преобразования осуществить формирование итоговой цифровой информа ши на выходах устройства. При этом величина задержки элемента 6 задержки выбирается из условия l l t+tf, гдеГч.Саг - время задержки распространения информационного сигнала че- рез цепи регистра 4 и сумматора 5 устройства.

Работа устройства может быть принудительно остановлена при снятии цифрового

сигнала «Разрещение на ления устройства.

тине 14 управ0

0

5 5 ,,

с 0

Формула изобретения

Цифровой измеритель длительности временных интервалов, содержащий триггер управления, первый вход которого подключен к входной щине управления измерителя, мно гоканальный генератор и.мпульсов, выходы которого подключены к соответствующим информационным входам первого регистра, выходы разрядов которого подключены к соответствующим информационным входам второго регистра, отличающийся тем, что, с целью повышения точности и бысгродей- ствия измерений, в него введены третий и четвертый регистры, сумматор, входной блок, элемент задержки и цифровой компаратор, причем щина запуска измерителя подключена к управляющему входу входного блока и входу запуска многоканального генератора импульсов, выходы которого подключены к инф(фмационным входам второго регистра, выходы разрядов первого и второго регистров подключены соответственно к первой и второй группам входов сумматора, выход1ы которого подключены к соответствующим информационным входам трет1)его регистра, разрядов которого соединены с соответствующими инфор.мационными входами четвертого регистра, выходной тиной данных измерителя и первой группой входов цифрового компаратора, вторая группа входов которого соединена с соответствующими выходами разрядов четверто1() регистра, а вьгход -- с П1ИНОЙ блокирования записи измерителя, входная щина которого соединена с сигна.тьным входом входного блока, вход блокировки KOTOpoi o подключен к выходной щине запроса измер)1теля и В1 гходу триггера управления, синхровход первого регистра подключен к первому выходу входного блока, второй выход которого подключен непосредственно к синхровходу второго регистра и через элемент задержки к синхро- входам третьего и четвертого регистров и второму входу триггера управления.

| Шляндин В | |||

| М | |||

| и др | |||

| ПРИБОР ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЗВУКОВ | 1923 |

|

SU1974A1 |

| Способ приготовления строительного изолирующего материала | 1923 |

|

SU137A1 |

| Авторское свидетельство СССР № 913325,, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Цифровые элек- - М.: Энергия, | |||

Авторы

Даты

1988-03-15—Публикация

1985-09-23—Подача