которых могут использоваться расширители арифметики, функциональные расширители, периферийные процессоры за счет сопряжения процессора одновременно с несколькими функциональными расширителями такого типа которым для работы требуется организация записи, и считывания более двух операндов. Целью изобретения является расширение класса решаемых задач. Это достигается тем, что в устройство, позволяющее осуществить загрузку операндов с общей шины в функциональные расширители

1

Изобретение относится к вычислительной технике, может быть исползовано в устройствах обработки инфомации для подключения функциональ- ных расширителей (ФР), например арифметических, к электронно-вычислительной машине (ЭВМ), и .является усовершенствованием устройства по основному авт.св. № 1182529.

Цель изобретения - расширение класса решаемых задач за счет обеспечения возможности подключения гру пы расширителей.

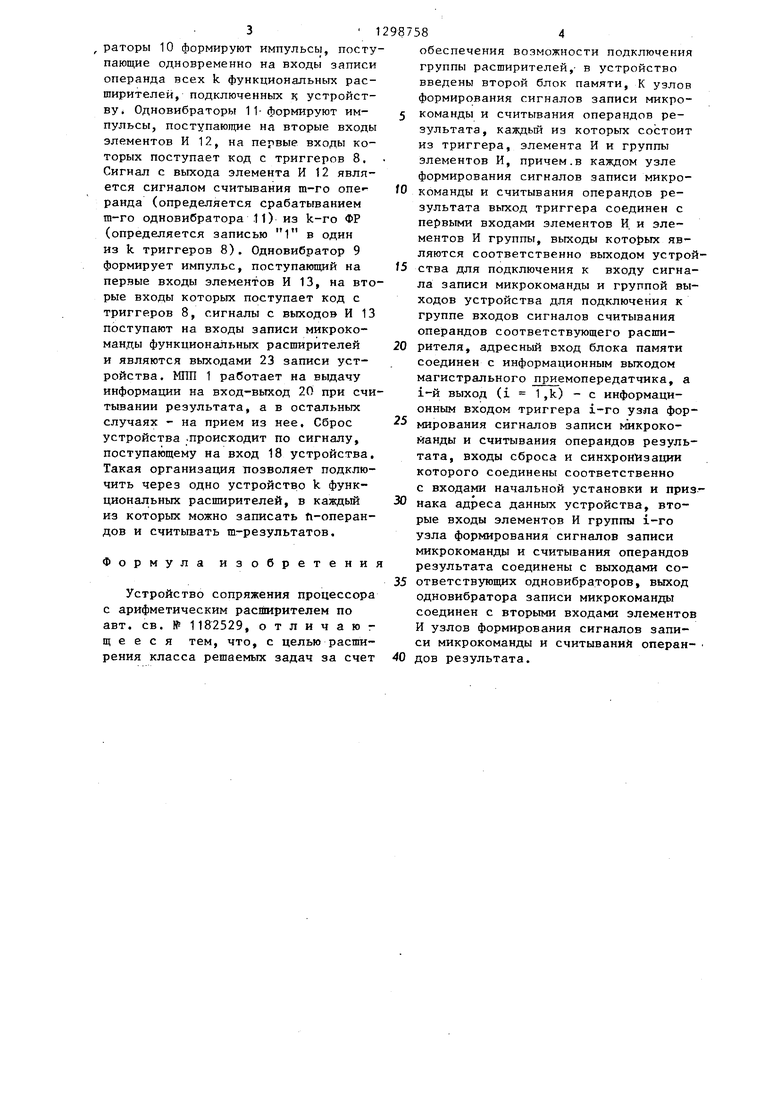

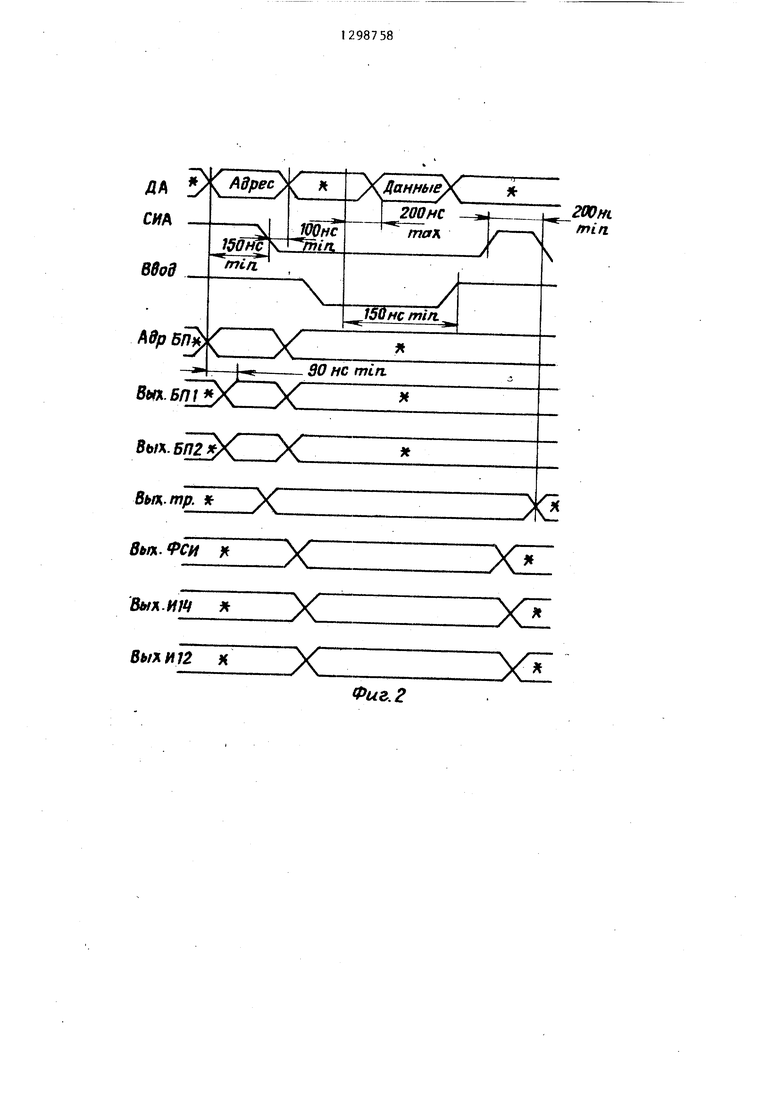

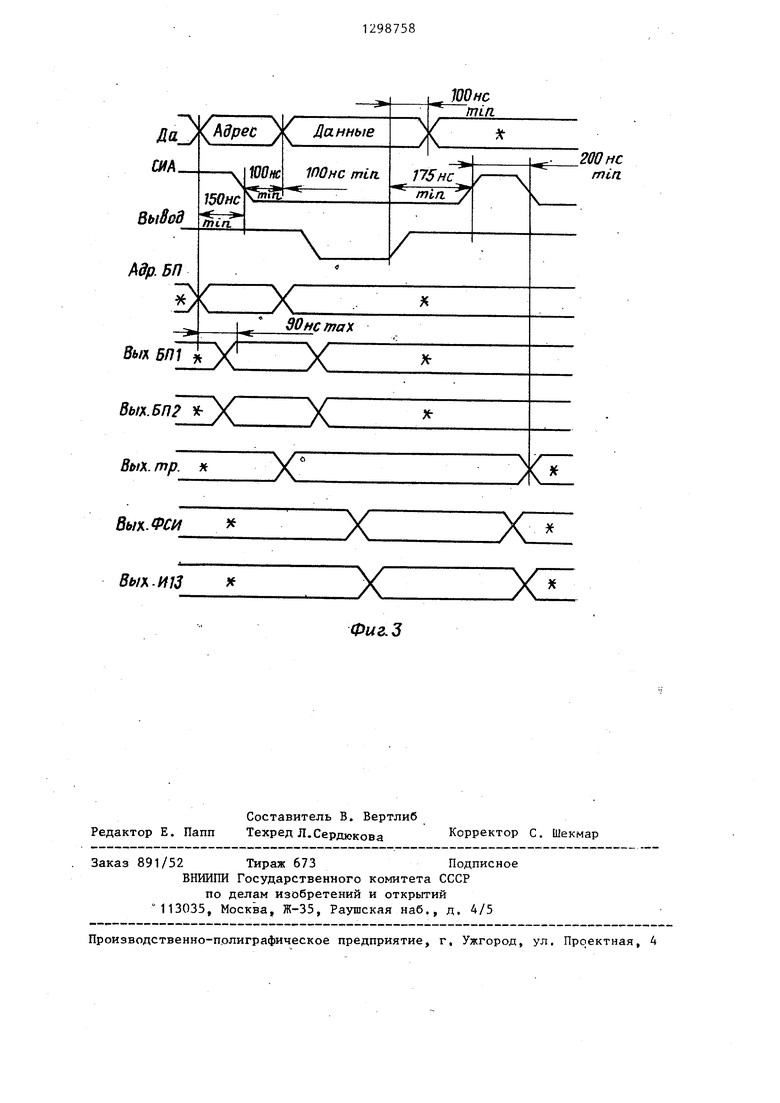

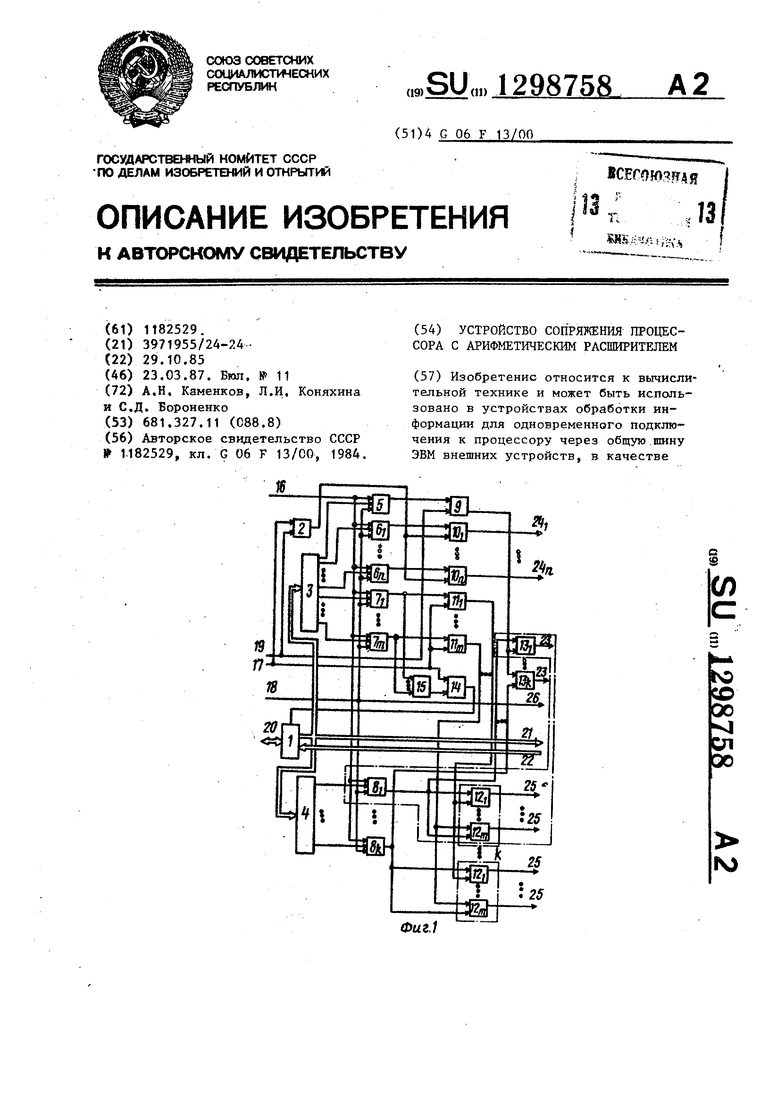

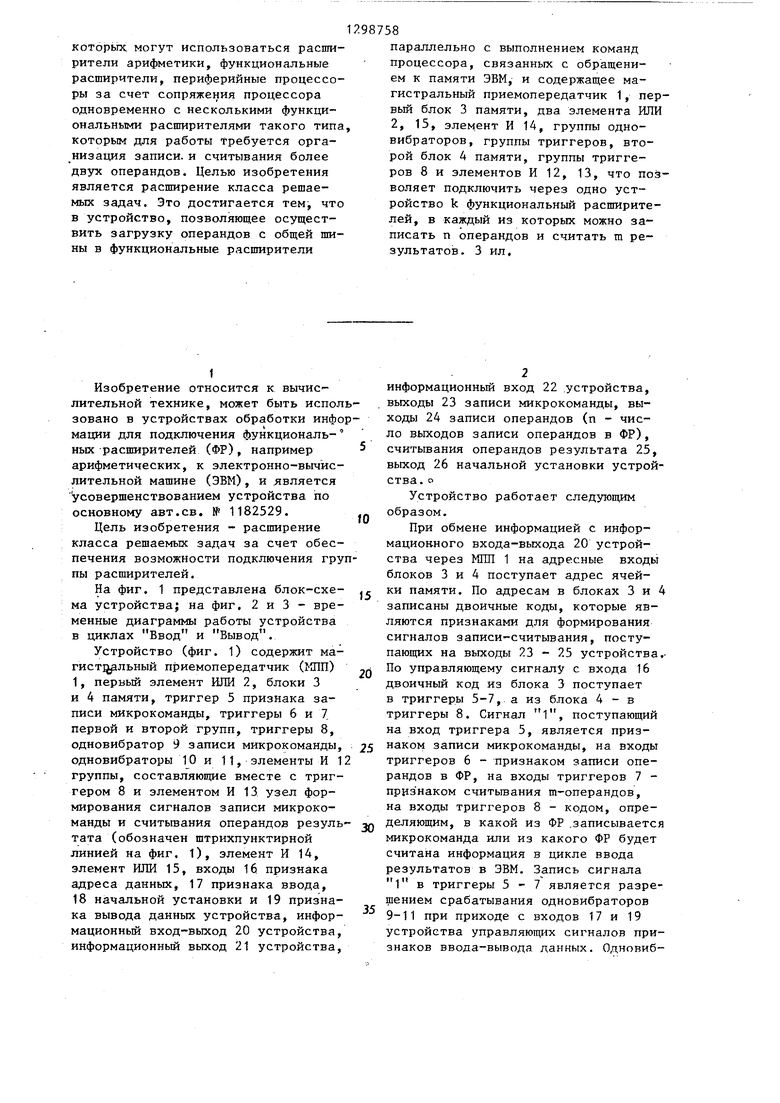

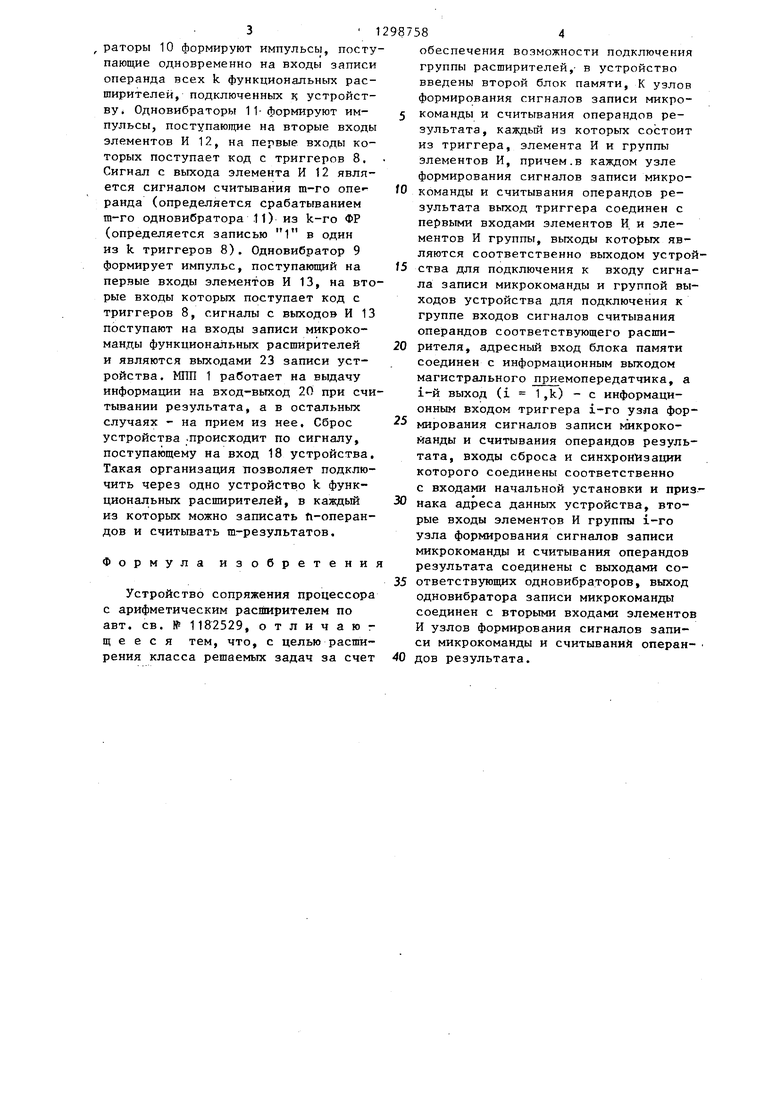

На фиг. 1 представлена блок-схема устройства; на фиг, 2 и 3 - временные диаграммы работы устройства в циклах Ввод и Вывод.

Устройство (фиг. 1) содержит ма- гист льный приемопередатчик (ШП) 1, первый элемент ИЛИ 2, блоки 3 и 4 памяти, триггер 5 признака записи микрокоманды, триггеры 6 и 7 первой и второй групп, триггеры 8, одновибратор 9 записи микрокоманды, одновибраторы и 11, элементы И 1 группы, составляющие вместе с триггером 8 и элементом И 13 узел формирования сигналов записи микрокоманды и считьгаания операндов результата (обозначен штрихпунктирной линией на фиг, 1), элемент И 14, элемент ИЛИ 15, входы 16 признака адреса данных, 17 признака ввода, 18 начальной установки и 19 признака вывода данных устройства, информационный вход-выход 20 устройства, информационный выход 21 устройства,

98758

параллельно с выполнением команд процессора, связанных с обращением к памяти ЭВМ, и содержащее магистральный приемопередатчик 1, первый блок 3 памяти, два элемента ИЛИ 2, 15, элемент И 14, группы одно- вибраторов, группы триггеров, второй блок 4 памяти, группы триггеров 8 и элементов И 12, 13, что позволяет подключить через одно устройство k функциональный расширителей, в каждый из которых можно записать п операндов и считать m результатов. 3 ил.

5

0

5

0

35

информационный вход 22 .устройства, выходы 23 записи микрокоманды, выходы 24 записи операндов (п - число выходов записи операндов в ФР), считывания операндов результата 25, выход 26 начальной установки устройства, о

Устройство работает следующим образом.

При обмене информацией с информационного входа-выхода 20 устройства через МГШ 1 на адресные входы блоков 3 и 4 поступает адрес ячейки памяти. По адресам в блоках 3 и 4 записаны двоичные коды, которые являются признаками для формирования сигналов записи-считывания, поступающих на выходы 23 - 25 устройства.- По управляющему сигналу с входа 16 двоичный код из блока 3 поступает в триггеры 5-7, а из блока 4 - в триггеры 8. Сигнал 1, поступающий на вход триггера 5, является признаком записи микрокоманды, на входы триггеров 6 - признаком записи операндов в ФР, на входы триггеров 7 - приз наком считьшания т-операндов, на входы триггеров 8 - кодом, определяющим, в какой из ФР .записывается микрокоманда или из какого ФР будет считана информация н цикле ввода результатов в ЭВМ. Запись сигнала 1 в триггеры 5-7 является разрешением срабатывания одновибраторов 9-11 при приходе с входов 17 и 19 устройства управляющих сигналов признаков ввода-вывода данных, Одновиб3 1

раторы Ю формируют импульсы, поступающие одновременно на входы записи операнда всех k функциональных расширителей, подключенных к устройству Одновибраторы 11-формируют им- пульсы, поступающие на вторые входы элементов И 12, на первые входы которых поступает код с триггеров 8. Сигнал с выхода элемента И 12 является сигналом считывания т-го one-- ранда (определяется срабатыванием тп-го одновибратора 11) из k-ro ФР (определяется записью 1 в один из k триггеров 8). Одновибратор 9 формирует импульс, поступающий на первые входы элементов И 13, на вторые входы которых поступает код с триггеров 8, сигналы с выходов И 13 поступают на входы записи микрокоманды функциональных расширителей и являются выходами 23 записи устройства. МПП 1 работает на выдачу информации на вход-выход 20 при считывании результата, а в остальных случаях - на прием из нее. Сброс устройства .происходит по сигналу, поступающему на вход 18 устройства. Такая организация позволяет подключить через одно устройство k функциональных расширителей, в каждый из которых можно записать п-операн- дов и считывать т-результатов.

Формула изобретения

Устройство сопряжения процессора с арифметическим расширителем по авт. св. № 1182529, отличают щ е е с я тем, что, с целью расширения класса решаемых задач за счет

5 0 5 0

5

0

584

обеспечения возможности подключения группы расширителей,- в устройство введены второй блок памяти, К узлов формирования сигналов записи микрокоманды и считывания операндов результата, каждый из которых состоит из триггера, элемента И и группы элементов И, причем.в каждом узле формирования сигналов записи микрокоманды и считывания операндов результата выход триггера соединен с первыми входами элементов И и элементов И группы, выходы которых являются соответственно выходом устройства для подключения к входу сигнала записи микрокоманды и группой выходов устройства для подключения к группе входов сигналов считывания операндов соответствующего расширителя, адресный вход блока памяти соединен с информационным выходом магистрального приемопередатчика, а i-й выход (i 1,k) - с информационным входом триггера i-ro узла формирования сигналов записи шкpoкo- Манды и считывания операндов результата, входы сброса и синхронизации которого соединены соответственно с входами начальной установки и признака адреса данных устройства, вторые входы элементов И группы i-ro узла формирования сигналов записи микрокоманды и считывания операндов результата соединены с выходами соответствующих одновибраторов, выход одновибратора записи микрокоманды соединен с вторыми входами элементов И узлов формирования сигналов записи микрокоманды и считываний операндов результата.

ЛА Адресу СИЛ л.

1SOHC

ввод

/rti/i

Affp 5/7

п

г1Я7/У mi/z

ewx.5/7;

ВьП.бпГ Bifin.mp. Х

. Г// X

X

ВМА.ИШ

X

5 /xff72 X

X

хи :xL

2XZ

Фиг. 2

Фиг.3

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство сопряжения процессора с арифметическим расширителем | 1985 |

|

SU1309031A2 |

| Микропрограммный процессор | 1981 |

|

SU980095A1 |

| Перестраиваемый микропрограммный процессор | 1981 |

|

SU983713A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1030801A1 |

| Процессорный модуль | 1985 |

|

SU1343421A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Периферийный процессор для обработки сигналов | 1985 |

|

SU1368889A1 |

| Электронная вычислительная машина | 1988 |

|

SU1520533A1 |

| Микро-ЭВМ | 1982 |

|

SU1124316A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах обработки информации для одновременного подключения к процессору через общую.шину ЭВМ внешних устройств, в качестве t Л § (Л to 00 СП 00 IV) Фиг./

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-03-23—Публикация

1985-10-29—Подача