00 00

00

ляет обменом в канале расширения блок 8 управления с помощью специальных микрокоманд. Если данный процессор готов к обмену, он генерирует активный уровень сигнала с выхода 28 и одновременно анализирует его. Сигнал с выхода 28 объединяется по проводному ИЛИ с аналогичными сигналами других процессоров и поэтому его активный уровень может быть только в случае готовности всех процессоров. Выполнение микрокоманды обмена задерживается до появления активного уровня сигнала с выхода 28. 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Система для обмена информацией | 1980 |

|

SU980087A1 |

| Устройство для сопряжения ЭВМ с линиями связи | 1991 |

|

SU1784989A1 |

| Устройство для обмена информацией междуэлЕКТРОННОй ВычиСлиТЕльНОй МАшиНОй(эВМ) и уСТРОйСТВАМи ВВОдА и ВыВОдА | 1979 |

|

SU809140A1 |

| Устройство для сопряжения ЭВМ с линиями связи | 1988 |

|

SU1536393A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Устройство для сопряжения процессора с внешними устройствами | 1990 |

|

SU1839253A1 |

| Специализированный процессор | 1990 |

|

SU1705834A1 |

| Устройство для сопряжения двух магистралей | 1984 |

|

SU1241249A1 |

| Устройство для обмена данными в многопроцессорной вычислительной системе | 1983 |

|

SU1136143A1 |

| Устройство для обмена информацией между процессором и абонентами | 1987 |

|

SU1444792A1 |

Изобретение относится к микроэлектронике и вычислительной технике и может быть использовано в составе информационно-измерительных систем на базе ЭВМ. Целью изобретения является повышение быстродействия периферийного процессора и точности обработки данных. Периферийный процессор для обработки сигналов подключен к каналу 1 ЭВЬ с унифицированным интерфейсом. Процессор содержит блоки 2-13 коммутации, блок 3 сопряжения, синхронизатор обмена 4, регистр 5 адреса, блок 6 управления матричным обменом, блок 7 коммутации адреса, блок 8 управления, блоки 9 и 10 памяти и арифметический блок 11. Для повышения производительности вычислительной системы ЭВМ - периферийный процессор имеется возможность подключения нескольких периферийных процессоров к каналу 1 ЭВМ. Для организации межпроцессорного обмена данными предназначены входы и выходы 29-32 канала расширения процессора. Управi (Л

1

Изобретение относится к микроэлектронике и вычислительной технике и может быть использовано в составе информационно-измерительных систем на базе ЭВМ.

Целью изобретения является повышение быстродействия периферийного процессора и точности обработки данных .

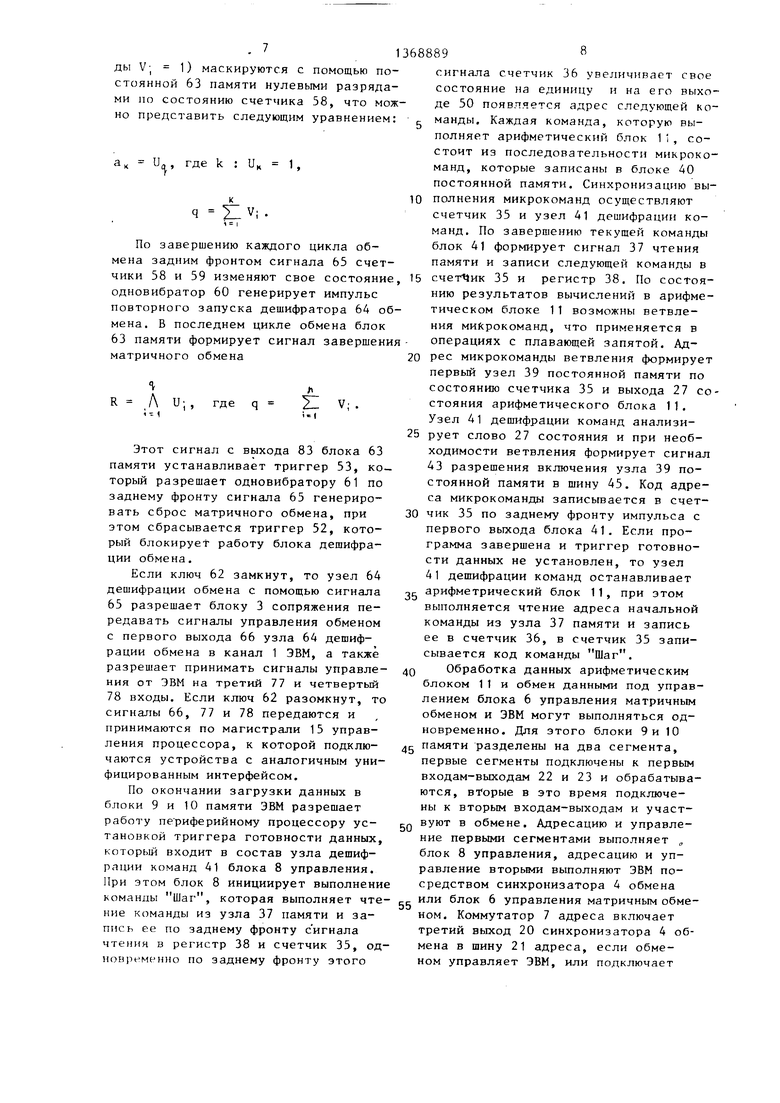

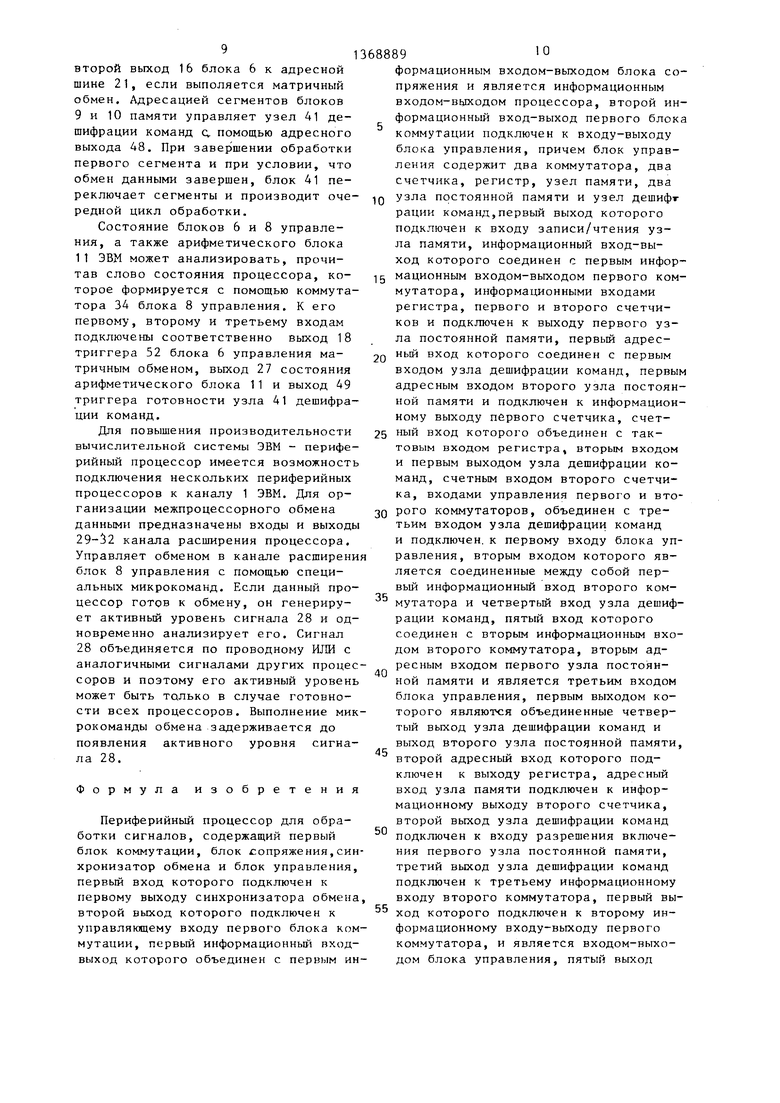

На фиг.1 представлена функциональная схема периферийного процессора; на фиг.2 - функциональная схема блока управления; на фиг.З - функциональная схема блока управления матричным обменом.

Периферийный процессор для обработки сигналов (фиг.1) подключен к каналу 1 ЭВМ с унифицированным интерфейсом. Процессор содержит первый блок 2 коммутации, блок 3 сопряжения, синхронизатор А обмена, регистр

5адреса, блок 6 управления матричным обменом, блок 7 коммутации адреса, блок 8 управления, первый 9 и второй 10 блоки памяти, арифметический блок 11, второй 12 и третий

13 блоки коммутации.

Первые входы-вьгходы первого блока -2 коммутации и блока 3 сопряжения подключены к каналу 1 ЭВМ, второй вход-выход первого блока 2 коммутации соединен с шиной 14 адреса данных процессора, к которой подключены информационные вход и выход регистра 5 адреса, входы-выходы блока

6управления матричным обменом, блока 8 управления, вторые входы-выходы блоков 9 и 10 памяти, первые входы управления которых подключены

к магистрали 15 управления процессора, к которой подключены второй вход выход блока 3 сопряжения, вход и первый выход синхронизатора А обмена.

первые входы и выход и второй вход блока 6 управления матричным обменом, первый вход блока 8 управления и вход управления блока 7 коммутации адреса, первый вход 16 которого подключен к второму выходу блока 6, третий 17 и четвертый 18 выходы которого подключены соответственно к входу синхронизации блока 3 сопряжения и второму входу блока 8 управления, пятый выход 19 соединен с входами синхронизации регистра 5 адреса и управления первого блока 2 коммутации и соединен с вторым выходом синхронизатора 4 обмена, третий выУод 20 которого соединен с вторым входом блока

7коммутации адреса, выход 21 которого соединен с первыми адресными входами блоков 9 и 10 памяти, первые входы-выходы которых подключены соответственно к первому 22 и второму 23 входам-выходам операндов арифметического блока 11, первый 24 и второй

25 входы-выходы результатов которого соединены с входами-выходами блоков 12 и 13 коммутации соответственно, входы управления которых соединены с первым выходом 26 блока 8 управления и с вторыми адресными и управля-: ющими входами блоков 9 и 10 памяти, с входом синхронизации арифметического блока 11, выход 27 состояния которого соединен с третьим входом блока

8управления, второй выход 28 которого является выходом синхронизации канала расширения процессора, первым 29 и вторым 30 информационными выходами которого являются выходы второго 12 и третьего 13 блоков коммутации , входы 31 и 32 которых авляются первьм и вторьм инфор- мационньми входами канала расширения.

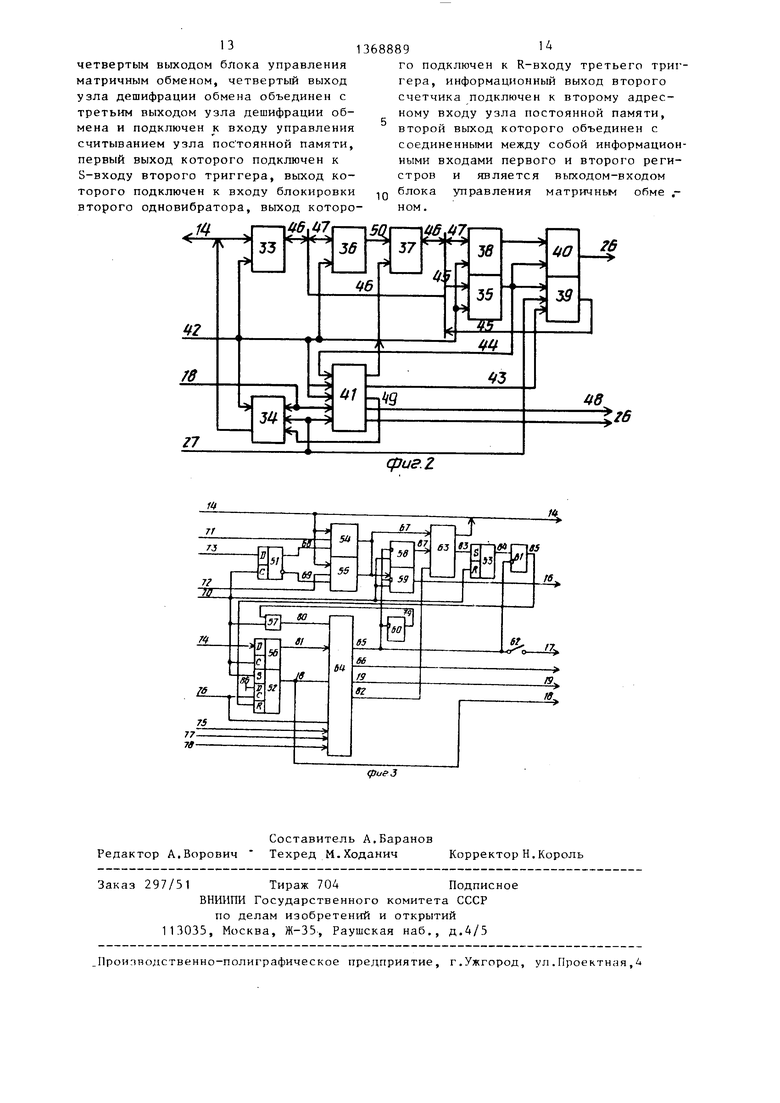

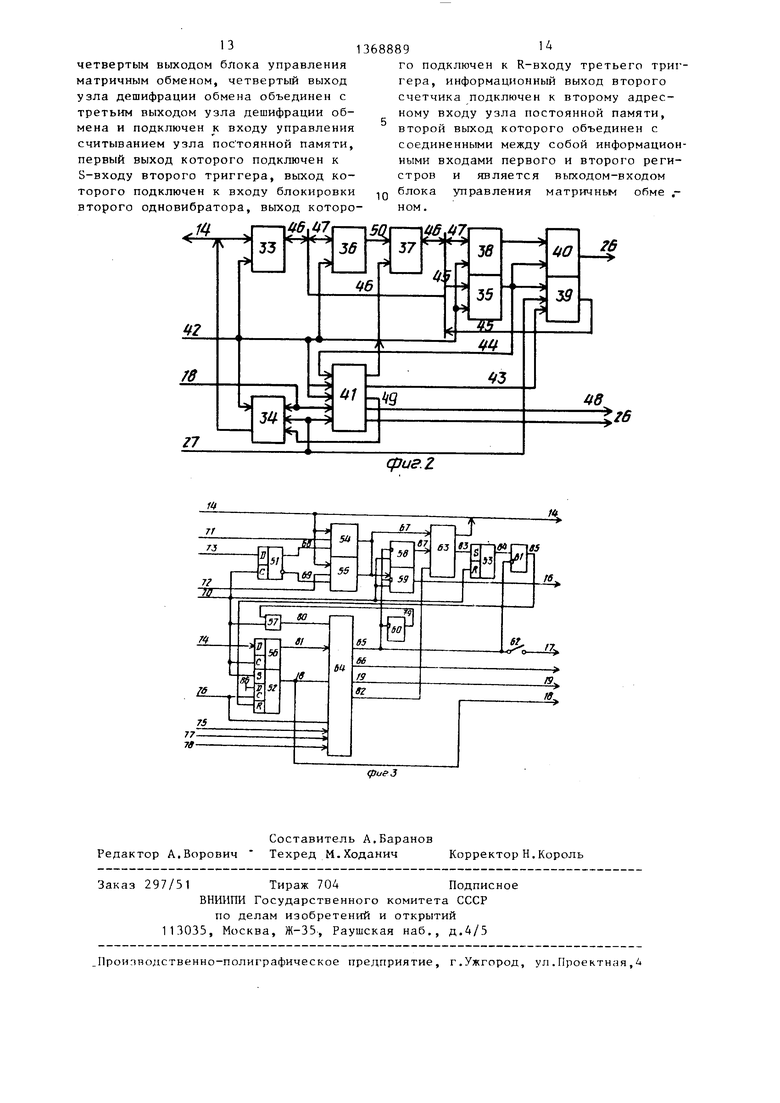

Блок 8 управления (фиг.2) содержит первый 33 и второй 34 коммутаторы, первый 35 и второй 36 счетчики, узел 37 памяти, регистр 38, первьй 39 и второй 40 узлы постоянной памяти и узел 41 дешифрации команд, первый выход которого соединен с входами управления коммутаторов 34 и 33, счетчиков 35 и 36, узла 37 памяти, регистра 38, объединен с вторым и третьим входами узла 41 дешифрации команд и подключен к первому входу 42 блока 8 управления, второй вход которого соединен с первым входом второго коммутатора 34 и четвертым входом узла 41 дешифрации команд, второй выход 43 которого соединен с входом разрешения включения узла 39 постоянной памяти, первый адресный вход которого соединен с первым адресным входом второго узла 40 постоянной памяти, первым входом узла 41 дешифрации команд и подключен к выходу 44 первого счетчика 35, информационный вход которого соединен с выходом первого узла 39 постоянной памяти и подключен к старшей части 45 шины 46 данных блока 8 управления которая соединяет первый вход-выход коммутатора 33 и вход-выход узла 37 памяти, младшая часть 47 шины 46 подключена к информационным входам счетчика 36 и регистра 38, выход которого подключен к второму адресному входу блока 40 постоянной памяти, выход 26 которого, объединенный с четвертым выходом 48 узла 41 дешифрации команд, является первым выходом блока управления, третий вход 27 которого соединен с вторым информационным входом коммутатора 34, вторым адресным входом блока 39 постоянной памяти и, пятым входом узла 41 дешифрации команд, третий выход 49 которого соединен с третьим входом коммутатора 34, информационньй выход которого соединен с вторым входом-выходом коммутатора 33 и с входом-выходом блока 8 управления, вторым выходом 28 которого является пятый выход узла 41 дешифрации команд, выход 50 второго счет- чикз 36 соединен с адресным входом узла 37 памяти.

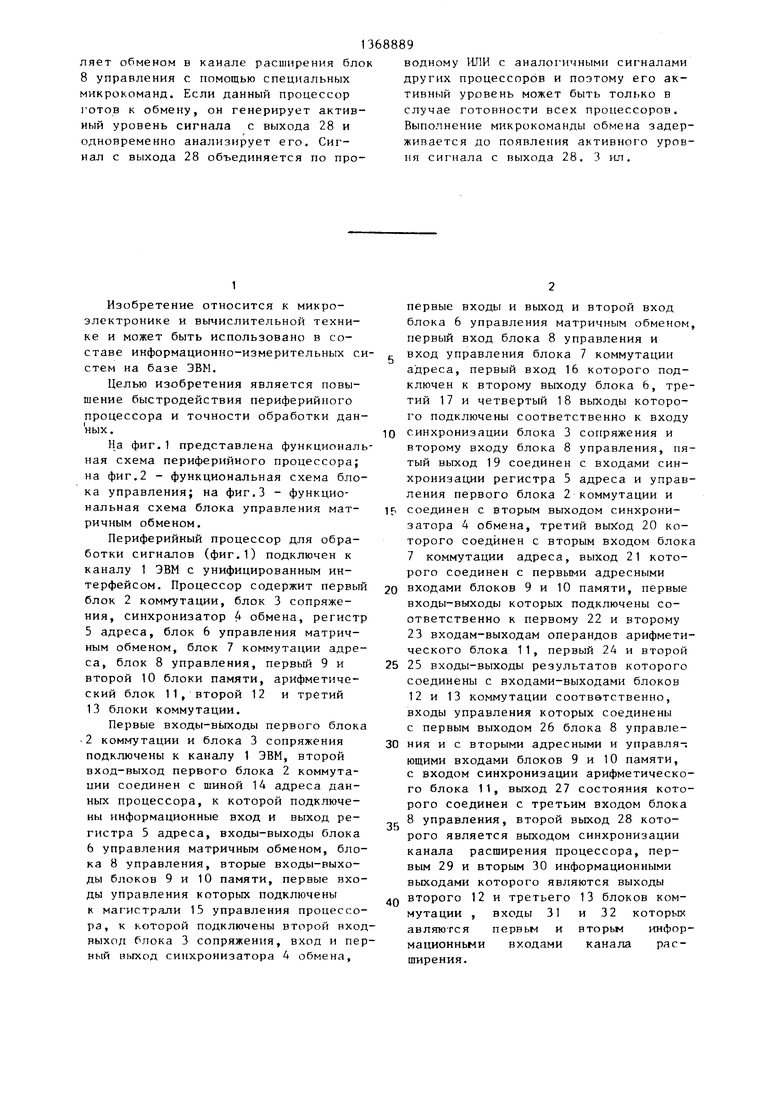

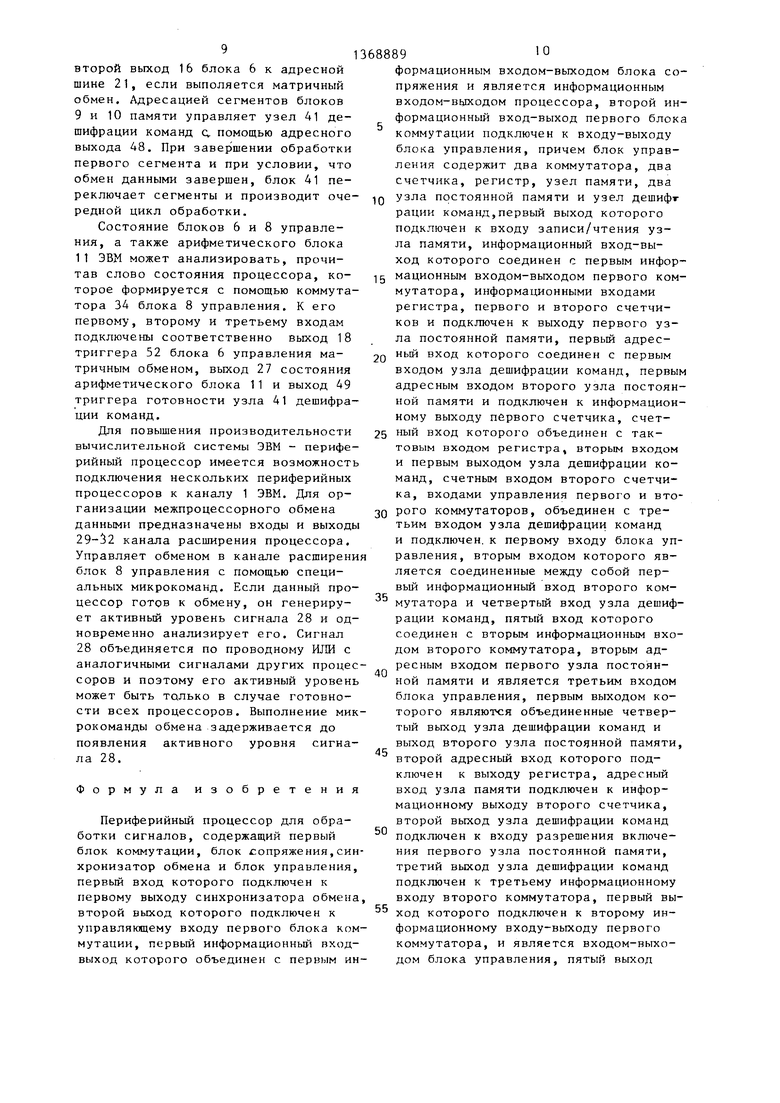

Блок b управления матричным обменом (фиг.З) содержит три триггера 51-53, три регистра 54-56, элемент ИЛИ 57, два счетчика 58 и 59, два одновибратора 60 и 61, ключ 62, узел

68889

63 постоянной памяти и узел 64 дешифрации обмена, первый выход 65 которого подключен к счетным входам счетчиков 58 и 59, синхровходам одноииб- раторов 60 и 61 и информационному входу ключа 62, выход которого является третьим выходом 17 блока 6 управления, матричным обменом, первым вы- 1Q ходом которого является второй выход 66 узла 64 дешифрации обмена, третий выход которого является пяуым выходом 19 блока 6 управления матричным обменом, вторым выходом 16 которого яв- 15 ляется выход счетчика 59, информационный вход которого соединен с первым адресным входом 67 узла 63 постоянной памяти и подключен к выходам регистров 54 и 55, входы разрешения 2Q чтения которых подключены соответственно к прямому 68 и инверсному 69 выходам триггера 51, тактовый вход 70 которого соединен с установочными входами счетчиков 58 и 59, R-входом триг- 25 гера 53, первым входом элемента ИЛИ 57, тактовым входом регистра 56, S- входом триггера 52, объединен с тактовыми входами 71 и 72 регистров 54 и 55 соответственно, D-входом 73 30 триггера 51, информационным входом 74 регистра 56, первым входом 75 узла 64 дешифрации обмена, соединенными между собой вторым входом узла 64 дешифрации обмена и тактовым входом 76 триггера 52 и является первым входом блока 6 управления матричным обменом, вторым входом которого являются объединенные третий 77 и четвертый 78 входы узла дешифрации обмена 64, вы35

0

5

ход 79 первого одновибратора 60 подключен к второму входу элемента ИЛИ 57, выход 80 которого подключен к пятому входу узла 64 дешифрации обмена, шестой вход 81 которого подключен к выходу регистра 56, выход триггера 52 подключен к седьмому входу узла 64 дешифрации обмена и является четвертым выходом 18 блока 6 управления матричным обменом, четвертьй выход 82 узла 64 дешифрации обмена объединен с третьим выходом 19 узда 64 дешифрации обмена и подключен к входу управления считыванием узла 63 постоянной памяти, первый выход 83 которого подключен к S-входу триггера 53, выход 84 которого подключен к входу блокировки одновибратора 61, выход 85 которого подключен к R-входу триггера 52, информацион0

ный вход 86 которого соединен с общим, информационный выход 87 счетчика 58 подключен к второму адресному входу узла 63 постоянной памяти, второй выход которого объединен с соединенными между собой информационными входами регистров 54 и 55 и является входом-выходом блока 6 управлния матричным обменом, который подключен к шине 14 адреса данных процессора .

Блок 2 коммутации предназначен для подключения канала 1 ЭВМ к шине 14 адреса данных процессора.

Блок 3 сопряжения предназначен для согласования сигналов управления обменом данных канала 1 ЭВМ с сигналами управления магистрали 15 процессора.

Синхронизатор 4 обмена предназначен для формирования сигналов управления узлами процессора при обращении к ним ЭВМ,

Периферийный процессор работает следующим образом.

Включение питания приводит синхронизатор 4 обмена и блоки 6 и 8 управления в исходное состояние, арифметический блок 11 - в состояние Стоп. Процессор может работать в двух режимах,В первом режиме он обрабатывает данные, которые находятся в памяти ЭВМ, В этом режиме ключ 62 блока 6 управления матричным обменом замкнут. Во втором режиме процессор обрабатывает данные, которые находятся в периферийной части, подключенной к шине 14 адреса данных процессора, В этом режиме ключ 62 разомкнут. Перед началом работы необходимо в узел 37 ламяти блока 8 управления записать программу работы арифметического блока 11, в счетчик 35 записывается код микрокоманды Шаг, в счетчик 36 - адрес начальной команды, ключ 62 устанавливается в необходимое положение, блок 6 управления программируется для выполнения функции обмена данными.

Процессор обрабатывает сегменты данных, которые состоят из двух слов и имеют матричную структуру, т,е. все слова сегмента расположены в ячейках памяти по адресам, которые можно представить в виде

ZL и;Н;,

где А - адрес первого слова; U;

0,1; Н; ; т, Р. - целые числа, Р; - Р .

Для организации матричного обмена необходимо определить вектор маски М, определяющий структуру сегмента и физический адрес сегмента А так, чтобы все его разряды, соответствующие Р- были равны единице. Например, это можно выполнить с помощью га рекуррентных преобразований вида

А.

+ А

(Н, - 1)15

20

4Н, (k 1, 2,,,., m).

некоторого логического адреса А, торый определяет номер сегмента и его расположение в адресном пространстве ЭВМ. Вектор маски равен

М

25

5

0

Блок 6 управления матричным обменом позволяет использовать для адресации сегментов данных один из двух

0 векторов маски М или М, которые записываются в регистры 54 л 55, адрес сегмента А записывается в регистре адреса 5 процессора. Матричный обмен инициируется ЭВМ с помощью синхронизатора 4 обмена. При этом синхронизатор 4 обмена генерирует сигналы 73 - код вектора маски, 74 - код функции и 70 - сигнал синхронизации обмена, который записывает сигналы 73 и 74 соответственно в триггер 51 и регистр 56, устанавливает триггер 52, счетчики 58 и 59, сбрасывает триггер 53 и через элемент ИЛИ 57 запускает дешифратор 64 обмена, который в соответствии с кодом функции 81 генерирует циклы ввода шти вывода данных, В каждом цикле обмена блок 6 управления матричным обменом с помощью одного из векторов маски, блока 63 постоянной памяти и адреса А по состоянию счетчика 58 формирует адрес ячейки сегмента данных, Обозначим разряды вектора маски как V, У,,..,У„, разряды счетчика 58 - и, и,.,,,и и разряды ад реса а,, а,,.,,а, где п - число разрядов. В процессе обмена единичные разряды адреса, указанные вектором маски (соответствующие разря5

0

ды V; 1) маскируются с помощью постоянной 63 памяти нулевыми разрядами по состоянию счетчика 58, что можно представить следующим уравнением:

и. , где k : UK 1,

Г

q V;

По завершению каждого цикла обмена задним фронтом сигнала 65 счетчики 58 и 59 изменяют свое состояние, одновибратор 60 генерирует импульс повторного запуска дешифратора 64 обмена. В последнем цикле обмена блок 63 памяти формирует сигнал завершения матричного обмена

V

Л J-1

1

где

л

Г

(

V; .

Этот сигнал с выхода 83 блока 63 памяти устанавливает триггер 53, который разрешает одновибратору 61 по заднему фронту сигнала 63 генерировать сброс матричного обмена, при этом сбрасывается триггер 52, который блокирует работу блока дешифрации обмена.

Если ключ 62 замкнут, то узел 64 дешифрации обмена с помощью сигнала 65 разрешает блоку 3 сопряжения передавать сигналы управления обменом с первого выхода 66 узла 64 дешифрации обмена в канал 1 ЭВМ, а также разрешает принимать сигналы управления от ЭВМ на третий 77 и четвертый 78 входы. Если ключ 62 разомкнут, то сигналы 66, 77 и 78 передаются и принимаются по магистрали 15 управления процессора, к которой подключаются устройства с аналогичным унифицированным интерфейсом.

По окончании загрузки данных в блоки 9 и 10 памяти ЭВМ разрешает работу пе риферийному процессору установкой триггера готовности данных, которьш входит в состав узла дешифрации команд 41 блока 8 управления. При этом блок 8 инициирует выполнени команды Шаг, которая выполняет чтение команды из узла 37 памяти и запись ее по заднему фронту с игнала чтения в регистр 38 и счетчик 35, одновременно по заднему фронту этого

0

5

0

5

сигнала счетчик 36 уве;п1чивает свое состояние на единицу и на его выходе 50 появляется адрес следующей команды. Каждая команда, которую выполняет арифметический блок 11, состоит из последовательности микрокоманд, которые записаны в блоке 40 постоянной памяти. Синхронизацию выполнения микрокоманд осуществляют счетчик 35 и узел 41 дешифрации команд. По завершению текущей команды блок 41 формирует сигнал 37 чтения памяти и записи следующей команды в счетЧик 35 и регистр 38. По состоянию результатов вычислений в арифметическом блоке 11 возможны ветвления микрокоманд, что применяется в операциях с плавающей запятой. Адрес микрокоманды ветвления формирует первый узел 39 постоянной памяти по состоянию счетчика 35 и выхода 27 состояния арифметического блока 11. Узел 41 дешифрации команд анализирует слово 27 состояния и при необходимости ветвления формирует сигнал 43 разрешения включения узла 39 постоянной памяти в шину 45. Код адреса микрокоманды записывается в счетчик 35 по заднему фронту импульса с первого выхода блока 41. Если программа завершена и триггер готовности данных не установлен, то узел 41 дешифрации команд останавливает с арифметрический блок 11, при этом выполняется чтение адреса начальной команды из узла 37 памяти и запись ее в счетчик 36, в счетчик 35 записывается код команды Шаг. Q Обработка данных арифметическим блоком 11 и обмен данными под управлением блока 6 управления матричным обменом и ЭВМ могут выполняться одновременно. Для этого блоки 9 и 10 с памяти разделены на два сегмента, первые сегменты подключены к первым входам-выходам 22 и 23 и обрабатываются, вторые в это время подключены к вторым входам-выходам и участвуют в обмене. Адресацию и управление первыми сегментами выполняет „ блок 8 управления, адресацию и управление вторыми выполняют ЭВМ посредством синхронизатора 4 обмена или блок 6 управления матричным обменом. Коммутатор 7 адреса включает третий выход 20 синхронизатора 4 обмена в шину 21 адреса, если обменом управляет ЭВМ, или подключает

0

0

5

второй выход 16 блока 6 к адресной шине 21, если выполяется матричный обмен. Адресацией сегментов блоков 9 и 10 памяти управляет узел 41 дешифрации команд Q. помощью адресного выхода 48. При завершении обработки первого сегмента и при условии, что обмен данными завершен, блок 41 переключает сегменты и производит очередной цикл обработки.

Состояние блоков 6 и 8 управления, а также арифметического блока 11 ЭВМ может анализировать, прочитав слово состояния процессора, которое формируется с помощью коммутатора 34 блока 8 управления. К его первому, второму и третьему входам подключены соответственно выход 18 триггера 52 блока 6 управления матричным обменом, выход 27 состояния арифметического блока 11 и выход 49 триггера готовности узла 41 дешифрации команд.

Для повышения производительности вычислительной системы ЭВМ - периферийный процессор имеется возможность подключения нескольких периферийных процессоров к каналу 1 ЭВМ. Для организации межпроцессорного обмена данными предназначены входы и выходы 29-52 канала расширения процессора. Управляет обменом в канале расширени блок 8 управления с помощью специальных микрокоманд. Если данный процессор готов к обмену, он генерирует активный уровень сигнала 28 и одновременно анализирует его. Сигнал 28 объединяется по проводному ИЛИ с аналогичными сигналами других процессоров и поэтому его активный уровень может быть только в случае готовности всех процессоров. Выполнение микрокоманды обмена задерживается до появления активного уровня сигнала 28.

Формула изобретения

Периферийный процессор для обработки сигналов, содержащий первый блок коммутации, блок сопряжения,синхронизатор обмена и блок управления, первьш вход которого подключен к первому выходу синхронизатора обмена второй выход которого подключен к управляющему входу первого блока коммутации, первый информационный вход- выход которого объединен с первым иня

, 368889 О

формационным входом-выходом блока сопряжения и является информационным входом-выходом процессора, второй информационный вход-выход первого блока коммутации подключен к входу-выходу блока управления, причем блок управления содержит два коммутатора, два счетчика, регистр, узел памяти, два узла постоянной памяти и узел дешифг

10

15

20

25

30

35

40

45

50

55

рации команд,первый выход которого подключен к входу записи/чтения узла памяти, информационный вход-выход которого соединен с первым информационным входом-выходом первого коммутатора, информационными входами регистра, первого и второго счетчиков и подключен к выходу первого узла постоянной памяти, первьш адресный вход которого соединен с первым входом узла дешифрации команд, первым адресным входом второго узла постоянной памяти и подключен к информационному выходу первого счетчика, счетный вход которого объединен с тактовым входом регистра, вторым входом и первым выходом узла дешифрации команд, счетным входом второго счетчика, входами управления первого и второго коммутаторов, объединен с третьим входом узла дешифрации команд и подключен, к первому входу блока управления, вторым входом которого является соединенные между собой первый информационный вход второго коммутатора и четвертый вход узла дешифрации команд, пятый вход которого соединен с вторым информационным входом второго коммутатора, вторым адресным входом первого узла постоянной памяти и является третьим входом блока управления, первым выходом которого являются объединенные четвертый выход узла дешифрации команд и выход второго узла постоянной памяти, второй адресный вход которого подключен к выходу регистра, адресный вход узла памяти подключен к информационному выходу второго счетчика, второй выход узла дешифрации команд подключен к входу разрешения включения первого узла постоянной памяти, третий выход узла дешифрации команд подключен к третьему информационному входу второго коммутатора, первый выход которого подключен к второму информационному входу-выходу первого коммутатора, и является входом-выходом блока управления, пятый выход

узла дешифрации команд является вторым выходом блока управления, отличающийся тем, что, с целью повышения быстродействия, в него введены регистр адреса, блок управления матричным обменом, первый и второй блоки памяти, арифметический блок, второй и третий блоки коммутации и блок коммутации адреса, выход которого подключен к адресным входам первого и второго блоков памяти, первые информационные входы- выходы которых подключены к выходам- входам соответственно первого и второго операндов арифметического блока, входы-выходы первого и второго результатов которого подключены к информационным входам-выходам соответственно второго и третьего блоков коммутации, информационные входы которых являются соответственно первым и вторым входами приема из канала расширения процессора,первым и вто . рым выходами выдачи в канал расширения которого являются выходы соответственно второго Vi третьего блоков коммутации, управляющие входы которых соединены с входом синхронизации арифметического блока, первым выходом блока управления, вторыми управляющими и адресными входами первого и второго блоков памяти, первые входы управления считыванием которых подключены к первым выходам соответственно синхронизатора обмена и блока управления матричным обменом, второй и третий выходы которого подключены соответственно к первому информационному входу блока коммутации адреса и входу синхронизации блока сопряжения, второй информационный вход-выход которого подключен к пер- вым входам синхронизатора обмена и блока управления матричным обменом и первым выходам блока управления матричным обменом, четвертый выход которого подключен к второму входу блока управления, третий вход которого подключен к выходу состояния арифметического блока, первый выход синхронизатора обмена подключен к входу управления блока коммутации адреса и первому входу блока управления матричным обменом,пятый вьгход которого соединен с вторым выходом синхронизатора обмена и подключен к входу Синхронизации регистра адреса, вход и выход котооого подключены к второму информационному входу-выходу первого блока коммутации, вторым информационным входам-выходам первого и второго блоков памяти и второму входу блока управления матричным обменом, гретий выход синхронизатора обмена подключен к второму информационному входу блока коммутации адреса, причем блок д управления матричным обменом содержит три триггера, элемент ШЩ, три регистра, два счетчика, два одновиб- ратора, ключ, узел постоянной памяти, узел дешифрации обмена, первый выход g которого подключен к счетным входам первого и второго счетчиков, синхро- входам первого и второго одновибра- торов и- информационному входу ключа, выход которого является третьим вы- Q ходом блока управления матричным обменом, первым выходом которого является второй выход узла дешифрапии обмена, третий выход которого является пятым выходом блока управления 5 матричным обменом, вторым выходом которого является информационный выход первого счетчика, информационный вход которого соединен с первым адресным входом узла постоянной памяти и под- Q ключен к выходам первого и второго регистров, входы разрешения чтения которых подключены соответственно к прямому и nHBepCHONry выходу первого триггера, тактовый вход которого соединен с установочными входами первого и второго счетчиков, R-входом второго триггера, первым входом элемента ИЛИ, тактовым входом третьего регистра, S-входом третьего триггера, объединен с тактовыми входами первого и второго регистров, D-входом первого триггера, информационным входом третьего регистра, первым входом узла дешифрации обмена, соединенными между собой вторым входом узла дешифрации обмена и тактовым входом третьего триггера и подключен к первому входу блока управления матричным обменом, вторым входом которого являются объединенные третий и четвертый входы узла дешифрации обмена, выход первого одновибратора подключен к второму входу элемента ИЛИ, выход которого подключен к пятому входу узла дешифрации обмена, шестой вход которого подключен к выходу третьего регистра, вьгход третьего триггера подключен к седьмому входу узла дешифрации обмена и является

5

0

5

0

5

13

четвертым выходом блока управления матричным обменом, четвертый выход узла дешифрации обмена объединен с третьим выходом узла дешифрации обмена и подключен к входу управления считыванием узла постоянной памяти, первый выход которого подключен к S-входу второго триггера, выход которого подключен к входу блокировки второго одновибратора, выход котороU6 147

.п

33

2

П

С

ц -|«g 3

1368889

го подключен к R-входу третьего гера, информационный выход второго счетчика подключен к второму адресному входу узла постоянной памяти, второй выход которого объединен с соединенными между собой информационными входами первого и второго регистров и 5шляется выход ом-в ход ом блока управления матричньм обме .- ном.

10

J7

б

J5

О

6

6

4

35

39

fS

в

±//5

cpua.Z

| Толстых Б.Л | |||

| и-др | |||

| Быстродействующий периферийный процессор | |||

| Деревянный торцевой шкив | 1922 |

|

SU70A1 |

| Периферийный процессор обработки сигналов | 1981 |

|

SU1013969A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-01-23—Публикация

1985-09-17—Подача