1

Изобретепие относится к вычислительной технике и может применяться в автоматизированных системах управления, контроля и обработки информации.

Известен шифратор, содержащий ячейки памяти, выходы которых подключены к входам элементов считывания.

При считывании кода с элементов считывания на выходе шифратора присутствует информация о всех входных сигналах независимо от того, поступили на них входные сигналы или нет. Педостаток шифратора состоит в излишестве информации, которое снижает быстродействие системы в целом 1.

Известен также наиболее близкий к изобретению шифратор адресов входных сигналов, содержащий ячейки памяти, выходы которых подключены к первому входу соответствующих элементов считывания, вторыми входами подсоединенных к шине разрешения считывания, формирователи сигналов сброса, выходы которых подключены к входам соответствующих ячеек памяти, и дешифратор 2.

Недостатком известиого шифратора является большой период времени считывания всех адресов, так как считываются все адреса ячеек памяти независимо от того, поступил на нее входной сигиал или нет.

Цель изобретения - повышение быстродействия нутем сокращения общего времени считывания адресов. Это достигается тем, что в шифратор введены формирователи входных сигналов, входы которых подключены к выходам соответствующих элементов считывания, а выходы-к входам дешифратора и входам соответствующих формирователей сигналов сброса, и

элементы ИЛИ, первые входы которых соединены с выходами соответствующих ячеек памяти, кроме первой, второй вход первого элемента ИЛИ связан с выходом первой ячейкн памяти и с третьим входом последующего

элемента считывания, а выходы всех элементов ИЛИ - с вторыми входами последующих элементов ИЛИ и с третьими входами последующих элементов считывания. Такое устройство иозволяет получить на

выходе дешифратора коды адресов только тех ячеек памяти, на которые поступили входные сигналы.

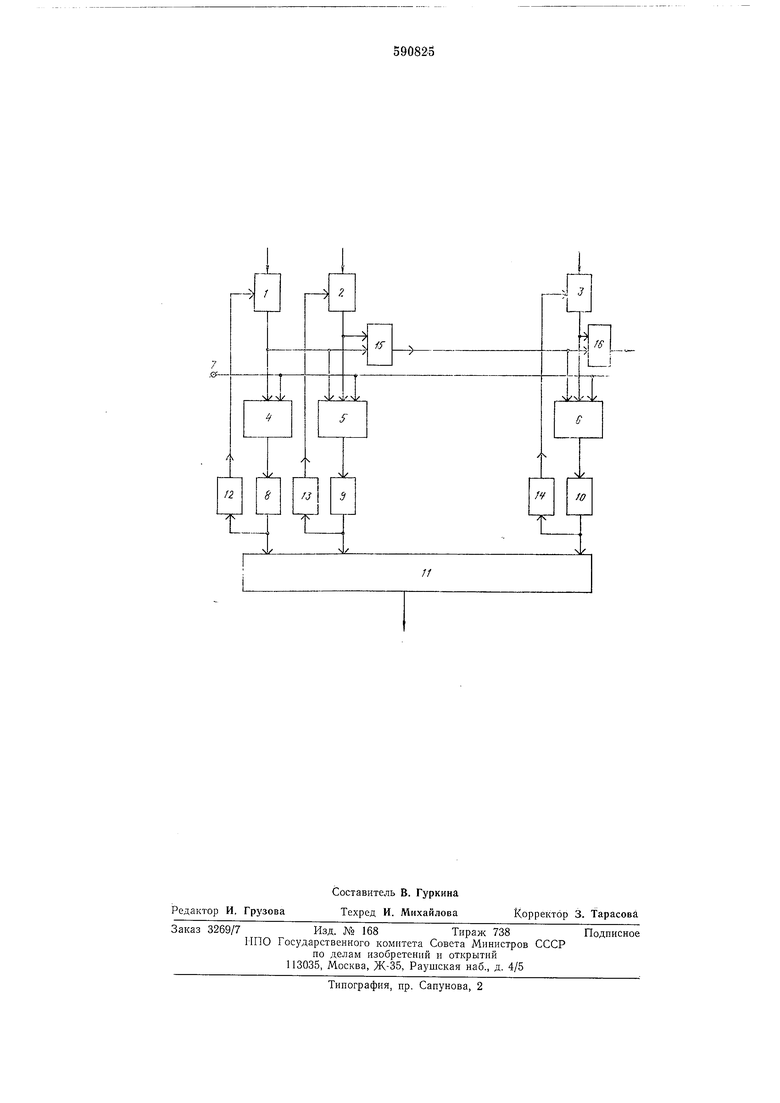

Иа чертеже представлена схема шифратора.

Шифратор содержит ячейки 1, 2, 3 памяти, подсоединенные выходами к первым входам элементов 4, 5 и 6 считывания, вторые входы которых соединены с щиной 7 разрешения считывания. Выходы элементов считывания

подключены к входам формирователей 8, 9 и 10 входных сигналов, выходы формирователей входных сигналов - к входам дентифратора 11 и входам формирователей 12, 13 и 14 сигналов сброса, а выходы формирователей сигналов сброса - к вторым входам ячеек 1, 2 и 3 памяти. Ячейки 2 и 3 памяти подсоединены выходами к первым входам соответствующих элементов ИЛИ 15 и 16. Выход элемента ИЛИ 15 подключен к второму входу последующего элемента ИЛИ 16 и третьему входу соответствующего элемента считывания.

Один вход элемента ИЛИ 15 соединен с выходом ячейки 1 памяти, другой вход - с выходом ячейки 2 памяти. Входом устройства являются ячейки 1, 2 и 3 памяти, на которые поступают входные спгпалы, а выходом - дещифратор 11, с его выхода снимаются кодовые сигналы адресов ячеек памяти, па которые поступили входные спгналы.

Шифратор работает следующим образом.

Входные сигналы запоминаются на ячейках 1, 2 и 3 палМятп, выходными сигналами которых открываются элементы 4, 5 и 6 считывапия. Сигналы с шины 7 считывания проходят через элемент 4 считывания и поступают на формирователь 8 входных сигналов. Выходной сигнал с формирователя 8 подается на дешифратор 11 и на формирователь 12 сигналов сброса. На дешифраторе 11 сигнал превращается в код адреса ячейки 1 памяти и с выхода дешифратора на выход устройства. Сигнал с выхода формирователя 12 сигналов сброса попадает на вход ячейки 1 памяти и устанавливает ее в состояние «О. Сигнал с шины 7 считывания через элементы 5 и 6 считывания не проходит, так как они закрыты запрещающим сигпалом, поступающим на их третий вход. После установки в «О ячейки 1 памяти элемент 5 считывания открывается, и сигнал с шины считывания проходит через формирователи 9, 13 и дешифратор 11 аналогично сигналу от элемента 4 считывания. Иосле считывания адреса ячейки 2 памяти происходит аналогичный процесс считываиия адреса ячейки 3 памяти.

Если на ячейку памяти входной сигнал не ноступил, соответствующий элемент считывания не открывается, и код адреса соответствующей ячейки памяти па выходе дешифратора отсутствует.

Технико-экономический эффект заключается в том, что данный шифратор выдает адреса только тех ячеек памяти, на которые ноступили входные сигналы, и эффективность работы шифратора определяется количеством считываемых адресов за допустимый такт времени в системе. Для систем управления с

малым временем реакции количество считываемых адресов составляет единицы процентов от общего количества. Таким образом, эффективность работы шифратора, определяемая как сокращение времени считывания адресов, увеличивается в десятки раз.

Формула изобретения

Шифратор, С0х1ержащий ячейки памяти, выходы которых подключены к первому входу соответствующих элементов считывания, вторые входы которых подключены к шине разрешения считывания, формирователи сигналов сброса, выходы которых подключены к

входам соответствующих ячеек памяти, и дешифратор, отличающийся тем, что, с целью иовыщения быстродействия, в него введены формирователи входных сигналов, входы которых подключены к выходам соответствующих элементов считывания, а выходы - к входам дещифратора и входам соответствующих формирователей сигналов сброса, и элементы ИЛИ, первые входы которых соединены с выходами соответствзющих ячеек памяти, кроме первой, второй вход первого элемента ИЛИ соединен с выходом первой ячейки памяти и с третьим входом последующего элемента считывання, а выходы всех элементов ИЛИ соединены с вторыми входами последующих элементов ИЛИ и с третьими входами последующих элементов считывания.

Источники информации, цринятые во внимание при экспертизе

1. Модуль ввода иннциативных сигналов МВИС А622-4 комплекса технических средств М-6000 АСВТ-М.ТУ.25.01.698.72.

2. Авторское свидетельство СССР № 347739, кл. G 05В 23/02.

| название | год | авторы | номер документа |

|---|---|---|---|

| Шифратор | 1980 |

|

SU886048A2 |

| Шифратор | 1981 |

|

SU1005187A2 |

| Шифратор | 1980 |

|

SU920835A1 |

| Ассоциативное запоминающее устройство | 1986 |

|

SU1429169A1 |

| Шифратор | 1985 |

|

SU1298801A2 |

| Устройство для ввода-вывода аналоговых сигналов | 1981 |

|

SU1015369A1 |

| Шифратор | 1978 |

|

SU752470A2 |

| СПУТНИКОВАЯ СИСТЕМА СВЯЗИ "КИБОЛ" | 1992 |

|

RU2033693C1 |

| Логический анализатор | 1989 |

|

SU1730627A1 |

| Шифратор | 1985 |

|

SU1298802A2 |

Авторы

Даты

1978-01-30—Публикация

1975-04-24—Подача