Изобретение относится к области автоматики и вычислительной техники и может быть использовано для контроля как дешифраторов, так и распределителей и преобразователей в единичный позиционный код.

Цель изобретения - расширение функциональных возможностей устройства за счет селектирования отказов и сбоев.

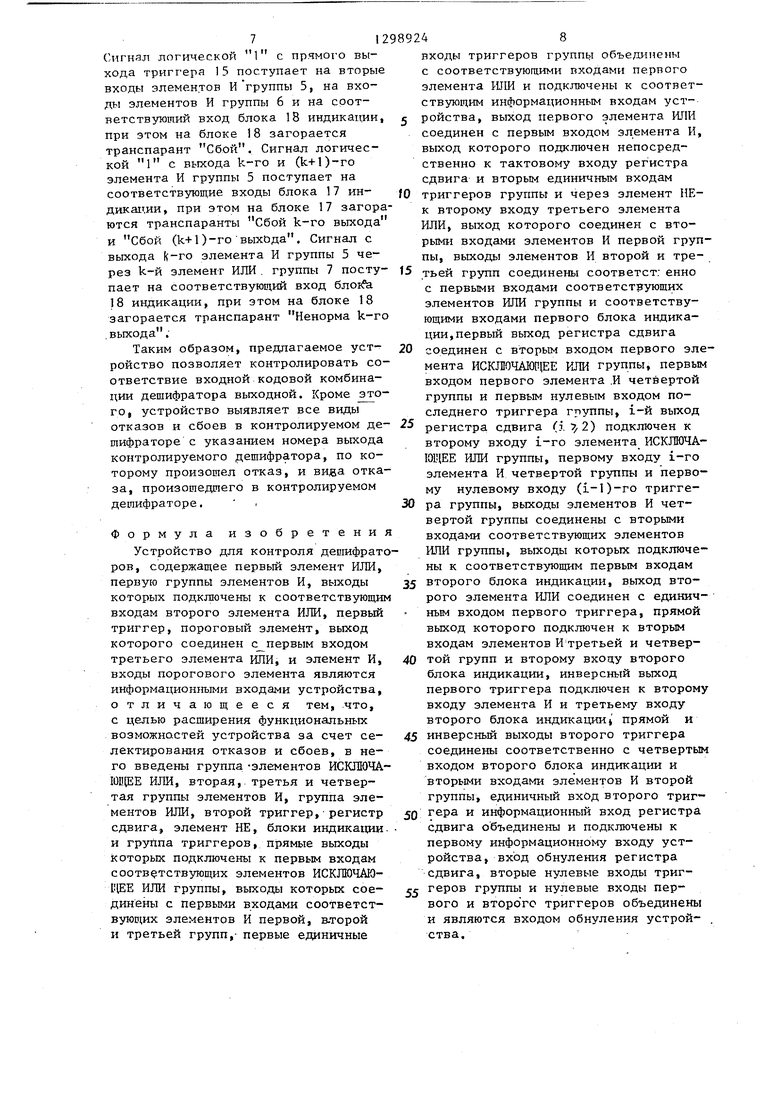

На чертеже представлена функциональная схема устройства.

Устройство для контроля дешифраторов содержит грзшпу 1 триггеров, группу 2 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, первую-четвертую группы 3-6 элементов И, группу 7 элементов ИЛИ, первый, второй и третий элементы ИЛИ 8-10, пороговый элемент 11, элемент НЕ 12, элемент И 13, регистр 14 сдвига, первый и второй триггеры 15 и 16, первый и второй блоки 17 и 18 индикацииj информационные входы 19, вход 20 обнуления, а также контролируемый дешифратор 21.

Блоки 17 и 18 индика11;ии включают в себя лампы накаливания или све- тодиоды, соответствующим образом подключенные к входам блока (через логические элементы или реле).

Устройство для контроля дешифраторов работает следующим образом..

В исходном состоянии триггеры 1, 15 и 16 и регистр 14 устанавливаются в нулевое состояние (на вход 20 подается высокий потенциал). На вход контролируемого дешифратора 21 подается последовательность кодовых Комбинаций с произвольной частотой. Последовательность кодовых комбинаций выбирается так, что на выходе контролируемого дешифратора 21 появляется сигнал в заранее заданной последовательности (например, в порядке возрастания с первого по п-й)

При включении устройства контроля дешифратора на блоке 18 индикации загораемся транспарант Норма Появившийся на первом выходе контро лируемого дешифратора 21 сигнал ло- .гической 1 поступает на один из единичных установочных входов первого триггера группы 1, элемент ИЛИ 8 пороговый элемент 11, информационный вход регистра 14, единичный установочный вход триггера 16. На прямом выходе триггера 16 появляется сигнал логической 1, который сигнализирует о начале работы, и на

блоке 18 индикации загорается парант Работа, С выхода элемента ИЛИ 8 сигнал логической I поступает на вход элемента И 13, на другом

входе которого имеется сигнал логической 1 с инверсного выхода триггера 15. Появившийся сигнал логической I на выходе элемента И 13 подступает на вторые единичные установочные входы триггеров группы 1, тактовый вход регистра 14 и на вход элемента НЕ 12. На прямом выходе первого триггера группы 1 и на первом выходе регистра I4 появляются

сигналы логической 1, которые поступают на соответствующие входы первого элемента ИСКЛЮЧАЮЩЕЕ РШИ группы 2. Сигнал логической 1 с первого выхода регистра 14 поступает также

на один из входов первого эленента И группы 6 и на нулевой установочный вход h-го триггера группы 1, устанавливая его в нулевое состояние. Сигнал логического О с элемента

НЕ 12 через элемент ИЛИ 10 поступает на входах -элементов И группы 3. Сигнал логического О с выхода первого элемента ИСКЛ10ЧА10и11ЕЕ ИЛИ группы 2 поступает на вт.орой вход первого элемента И группы 3. После окончания действия сигнала логической 1 и до появления сигнала логической 1 на втором выходе контролируемого дешифратора 21 (в период Т

смены кодовой комбинации) сигнал логической 1 с выхода элемента НЕ 12 через элемент ШИ-Г 10 поступает на -Г первые входы элемента И группы 3, на вторых входах которых имеется

сигнал логического О. Сигнахс логического О с элементов И группы 3 поступает через элемент ИЛИ 9 на единичный установочньй вход триггера 15 и не меняет его состояния. На

блоке 18 индикации продолжают гореть транспаранты Норма и Работа.

Через период Т смены кодовых комбинаций сигнал логической 1 появляется на втором выходе контроли-,

руемого дешифратора 21. Работа уст- ройства контроля дешифраторов остается аналогичной. Отличие заключается в том, что происходит перезапись логической 1 с первого выхода регистра 14 на второй, и сигнал логической 1 с второго выхода регистра 14 поступает на один из входов второго элемента И группы 6, на нулевой установочный вход первого триг3 .

т сра группы 1 , устанавливая его в нулевое состояние. Сигнал логическо 1 появляется на прямом выходе второго триггера группы 1 и поступает на первый вход второго элемента ИС- КГПОЧАЮЩЕЕ ИЛИ группы 2, на второй вход которого поступает сигнал логической 1 с второго выхода регистра 14, Сигнал логического О с выхода второго элемента ИСКЛЮЧАЮ- ЩЕЕ ИЛИ группы 2 поступает на один из входов второго элемента И группы 3. В дальнейшем работа устройства контроля дешифраторов остается аналогичной описанному, если контроля- руемый дешифратор 21 исправлен.

При возникновении различных видов неисправностей .в контролируемом дешифраторе 21, например, когда возбуждается требуемая k-я мина и не требуемая (k+I)-H шина, на k-ом и (k+l)-OM входах 19 появляются сигналы логической которые поступают на соответствующие входы элемента ИЛИ 8, порогового элемента 1 на один из единичных установочных входов k-ro и (1с+1) -го триггеров группы К Сигнал логической (сигнал Сбой) с выхода порогового элемента 1 1 , нас гро нного на порог срабатывания, превышающий номинальное значение выходного потенциала, через элемент ИЛИ 10 поступает на один из входов элементов И группы 3. Сигнал логической 1 с выхода элемента ИЛИ 8 поступает на один из входов элемента И 13, на другом входе которого имеется сигнал логической 1 с инверсного выхода триггера 15. Сигнал логической 1 с выхода элемента И 13 поступает на вторые единичные входы триггеров групп

, тактовый вход регистра 14, вход элемента НЕ 2. На прямых выходах k-ro и (k+)-ro триггеров группы 1 и на k-OM выходе регистра 14 появляются сигналы логической 1, которые поступают на соответствующие входы k-ro и (k+)ro элементов ИСКЛ10ЧА10- ЩЕЕ ИЛИ группы 2 соответственно. Сигнал логической 1 с k-ro выхода регистра 14 поступает также на один из входов k-ro элемента И группы 6 и на нулевой установочный вход (k- -1)-го триггера группы 1, устанавливая его в нулевое состояние.

Сигнал лoг iчecкoй с выхода (k+l)-ro элемента ИСКЛЮ ШСЩЕЕ ИЛИ группы 2 и сигнал логического О

5

0 5

5

0

5

0

5

выхода элемента ИСКЛЮЧМ01ЧЕЕ ИЛИ группы 2 поступают на вторые входы (k+l)-ro и k-ro элемента И группы 3 соответственно, на вторых входах которых имеется сигнал логической с выхода элемента ИЛИ 10, Сигнал логической 1 с выхода (k+ fD-ro элемента ИСКЛЮЧАЮЩЕЕ ИЛИ группы 2 также поступает на один из входов (k+l)-ro элемента И группы 5 и на один из входов (k+l)-ro элемента И группы 4. Сигнал логической 1 с выхода (k+l)-ro элемента И группы 3 через элемент 9 поступает на - единичный установочный вход триггера 15. Сигнал лопгческого О с инверсного выхода триггера 15 поступает на один из входов элемента И 13 и на соответствуюппш вход блока .18 индикации, при этом гаснет его транспарант Норма. Сигнал логичес- кой с прямого выхода триггера 15 поступает на вторые входы элементов И группы 5, на выходы элементов И группы 6 и на соответствз1 щий вход блока 18 индикации, при этом на блоке 18 загорается транспарант Сбой, Сигнал логической с выхода (k+l)-ro элемента И группы 5 поступает на соответствуюпцто вход блока 17 индикации.При этом на блоке 17 загорается транспарант Сбой (k+l)ro выхода. Сигнал с выхода R-ro элемента И группы 6 через k-й элемент ИЛИ группы 7 поступает на соответст- в тощий вход блока 18 индикации, при этом на блок е 18 загорается транспарант Ненорма k-ro выхода,

В случае, когда на выходе контролируемого дешифратора 2 при наличии входной кодовой комбинации не возбуждается ни одна выходная шина, на блоке 18 индикации горит транспарант Норма и не загорается транспарант Работа, так как триггер 16 не установлен в единичное состояние, В случае, когда на выходе контролируемого дешифратора 21 при наличии входной кодовой комбинации не возбуждается первая шина, а возбуждается k-я шина, сигнал логической 1 с первого ззыхода контролируемого дешифратора 2 не поступает на информационный вход регистра 4 и на единичньп установочньш вход триггера 16j при этом не загорается транспарант Работа на блоке 1В ии- дикации. Сигнал логической 1 с R-ro выхода контролируемого дешифра5129

тора 21 поступает на соответствующий вход элемента ИЛИ 8, порогового элемента 11, на один из единичных установочных входов К-го триггера группы 1, Сигнал логической с выхода элемента ИЛИ 8 поступает на один из входов элемента И 13, на другом входе которого имеется сигнал логической I с инверсного выхода триггера 15 Сигнал логической 1 с вькода элемента И 13 поступает на вторые единичные установочные входы триггеров группы 1., тактовый вход регистра 14, вход элемента НЕ 12„ На прямом выходе

-ro триггера группы 1 появляется сигнал логической 1, который через -й элемент ИСКЛЮЧА1ЩЕЕ ИЛИ 2 постуает на один из входов k-ro элемента И группы 3, один из входов k-ro элемента И группы 5, один из входов -ro элемента И группы 4i на втором входе которого имеется сигнал логиеской 1 с инверсного выхода триггера 16. Сигнал логической- с выхода R-ro элемента И группы А через k-й элемент ИЛИ группы 7 поступает на соответствующий вход блока 18 индикации, при этом на блоке 18 загорается транспарант Ненорма k-rO; выхода, После окончания действия сигнала логической 1 на k-M выходе и-до поя вления сигнала, логической 1 на втором выходе контролируемого дешифратора 21 (в период Т , смены входной кодовой комбинации), сигнал логической 1 с выхода элемента НЕ 12 через элемент ИЛИ 10 поступает на втОрые входы элементов И группы 3. Сигнал логической 1 с выхода k-ro элемента И группы 3 через элемент ИЛИ 9 поступает на еди- ничный установочный вход триггера 15. Сигнал логического О с инверсного выхода триггера 15 поступает на один из входЬв элемента И 3 и на соответствующий вход блока 18 индикации, при этом гаснет транспарант Норма на блоке 18. Сигнал логической 1 с прямого выхода триггера 5 поступает на вторые входы элемён тов И группы 5, на входы элементов И группы 6 и на соответствующий вход блока 18 индикадаи, при этом на блоке 18 загорается транспарант Сбой. . Сигнал логической 1 с выхода k-ro элемента И (Группы 5 поступает на соответствующий вход блока 17 индикации, при этом на блоке 17 загорается транспарант Сбой k-ro выхода.

В случае, когда па выходе контролируемого дешифратора 21 при наличии входной кодовой комбинации не возбуждается k-я шина, а возбуждается (k+)-я шина (т.е. возбуждается не требуемая шина), на (k+l)ом выходе контролируемого дешифратора 21 появляется сигнал логической l, кото

рый поступает .на соответс- вующий вход элемента ИЛИ 8, порогового элемента 11, на один из единичных установочных входов (k+l)-ro триггера группы . Сигнал логической 1 с выхода элемента ИЛИ 8 поступает на один из входов элемента И 13, на другом входе которого имеется сигнал логической 1 с инверсного выхода триггера 15, Сигнал логической 1 с выхода элемента И 13 поступает на вторые единичные установочные входы триггеров группы 1, тактовый вход регистра 14, вход элемента НЕ 12, На прямом выходе (k+I)-го триггера группы 1 и на k-OM выходе регистра 14 появляются сигналы логической 1, которые поступают на соответствующие входы (k+l)-ro и k-ro элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы 2 соответственно. Сигнал логической 1 с k-ro выхода регистра 14 поступает также на один из входов k-го элемента И группы 6 и на нулевой установочный вход (k+l)-го триггера группы I, .устанавливая его в нулевое состояние. Сигнал логической 1 с k-ro и (k+)-ro элементов ИСКЛ10ЧАЮ1 Щ:Е или группы 2 поступает на вторые входы k-ro и (k+)-ro элементов И группы 4 и на один из входов k-ro и (k+l)-го элементов И группы 5, один из входов k-ro и (k+l)-ro элементов И группы 3, После окончания действия сигнала логической 1 на (k+l)-ом выходе контролируемого дешифратора 2 в период Т смены входной кодовой комбинации сигнал логической с выхода элемента НЕ 12 через элемент ИЛИ 10 поступает на вторые входы элементов И группы 3, Сигнал логической 1 с выходи k-ro и (k+l)-ro элемента И группы 3 через элемент ИЛИ 9 поступает на единичный установочный вход триггера 15, Сигнал логического О с инверсного выхода триггера 15 поступает на один из входов элемента И 13 и на соответствующий вход блока 18 индикации, при этом гаснет г транспарант Норма на блоке 18,

С игнал логической 1 с прямого выхода триггера 15 поступает на вторые входы элементов И группы 5, на входы элементов И группы 6 и на соответствующий вход блока 18 индикации, при этом на блоке 18 загорается транспарант Сбой. Сигнал логической 1 с выхода k-ro и (k+l)-ro элемента И группы 5 поступает на соответствующие входы блока 17 ин- дикап .ии, при этом на блоке 17 загораются транспаранты Сбой k-ro выхода и Сбой (k+1)-го выхода. Сигнал с выхода k-ro элемента И группы 5 через k-й элемент ИЛИ . группы 7 поступает на соответствующий вход бло1 18 индикации, при этом на блоке 18 загорается транспарант Ненорма k-ro .выхода.

Таким образом, предлагаемое устройство позволяет контролировать соответствие входной кодовой комбинации дешифратора выходной. Кроме это- го, устройство выявляет все виды отказов и сбоев в контролируемом дешифраторе с указанием номера выхода контролируемого дешифратора, по которому произошел отказ, и виеа отказа, произошедшего в контролируемом дешифраторе.

Формула изобретения

Устройство для контроля дешифраторов, содержащее первый элемент ИЛИ, первую группы элементов И, выходы которых подключены к соответствующим входам второго элемента ИЛИ, первый триггер, пороговый элемент, выход которого соединен с первым входом третьего элемента ИЛИ, и элемент И, входы порогового элемента являются информационными входами устройства, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет се- лектирования отказов и сбоев, в него введены группа -элементов ИСКЛЮЧА- ИЛИ, вторая,, третья и четвертая группы элементов И, группа элементов ИЛИ, второй триггер, регистр сдвига, элемент НЕ, блоки индикащш. и группа триггеров, прямые выходы которых подключены к первым входам соотв тствзтащих элементов ИСКЛЮЧАЮ- 1ЦЕЕ ИЛИ группы, выходы которых соединены с первыми входами соответст- вуюпщх элементов И первой, аторой и третьей групп,- первые единичные

входы триггеров группы объед 1иены с соответствующими входами первого элемента ШШ и подк,пючены к соответствующим информационным входам устройства, выход первого элемента ИЛИ соединен с первым входом элемента И, выход которого подключен непосредственно к тактовому входу регистра сдвига и вторым единичным входам

триггеров группы и через элемент НЕ- к второму входу третьего элемента ИЛИ, выход которого соединен с вторыми входами элементов И первой группы, выходы элементов И второй и третьей групп соединены соответст: енно с первыми входами соответствующих элементов ИЛИ группы и соответствующими входами первого блока индикации, первый выход регистра сдвига

соединен с вторым входом первого элемента ИСКЛ10ЧАЮР1ЕЕ ИЛИ группы, первым входом первого элемента .И четвертой группы и первым нулевым входом последнего триггера группы, i-й выход

регистра, сдвига О. т/2 ) подключен к второму входу i-ro элемента ИСКЛЮЧА Ю1НЕЕ ИЛИ группы, первому входу i-ro элемента И четвертой группы и первому нулевому входу (i-l)-ro триггера группы, выходы элементов И четвертой группы соединены с вторыми входами соответствующих элементов ИЛИ группы, выходы которых подключены к соответствующим первым входам

второго блока индикации, выход второго элемента ИЛИ соединен с единичным входом первого триггера, прямой выход которого подключен к вторьи входам элементов И третьей и четвертой групп и второму входу второго блока индикации, инверсный вьпсод первого триггера подключен к второму входу элемента И и третьему входу второго блока индикации прямой и

инверсный выходы второго триггера соединены соответственно с четвертым входом второго блока индикации и вторыми входами элементов И второй группы, единичный вход второго триггера и информационный вход регистра сдвига объединены и подключены к первому информационному входу устройства, вход обнуления регистра сдвига, вторые нулевые входы триггеров группы и нулевые входы первого и второ гс триггеров объединены и являются входом обнуления устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля оперативной памяти | 1986 |

|

SU1401520A2 |

| Устройство для контроля логических блоков | 1983 |

|

SU1160414A1 |

| Устройство для ввода-вывода информации | 1984 |

|

SU1218373A1 |

| Устройство для контроля оптимальных @ -кодов Фибоначчи | 1983 |

|

SU1149261A1 |

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1474650A2 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1986 |

|

SU1425698A2 |

| Устройство для управления процессами передачи сигналов контроля и управления в иерархической автоматизированной системе управления | 1990 |

|

SU1807501A1 |

| Устройство для контроля счетчиков | 1977 |

|

SU741268A2 |

| Устройство для контроля логических блоков | 1988 |

|

SU1649550A1 |

| Устройство для формирования тестов диагностики дискретных блоков | 1983 |

|

SU1149265A1 |

Изобретение относится к автоматике и вычислительной технике. Его использование для контроля устройств. формирующих на своих выходах единичный позиционный код, позволяет селектировать отказы и сбои в элементах контролируемого дептифратора. Устройство, содержит элементы ИЛИ 8- 10,группу 3 элементов И, триггер 15, элемент И 13, пороговый элемент 11t Введение группы 1 триггеров, группы 2 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, групп 4-6 элементов И, группы -7 эле- ментов ИЛИ, триггера 16, регистра 14 сдвига, элемента НЕ 12 и блоков 17, 18 индикации обеспечивает возможность выявления различных неисправностей в работе контролируемого дешифратора. 1 ил. ± 8лТ (Л С

| УСТРОЙСТВО для КОНТРОЛЯ ДЕШИФРАТОРА | 0 |

|

SU206639A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для контроля дешифратора | 1980 |

|

SU918948A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-03-23—Публикация

1985-10-14—Подача