Изобретение относится к вычислительной технике и может быть использовано для контроля логических блоков и схем при приемосдаточных испытаниях.

Целью изобретения является упрощение устройства и сокращение времени контроля однотипных логических блоков.

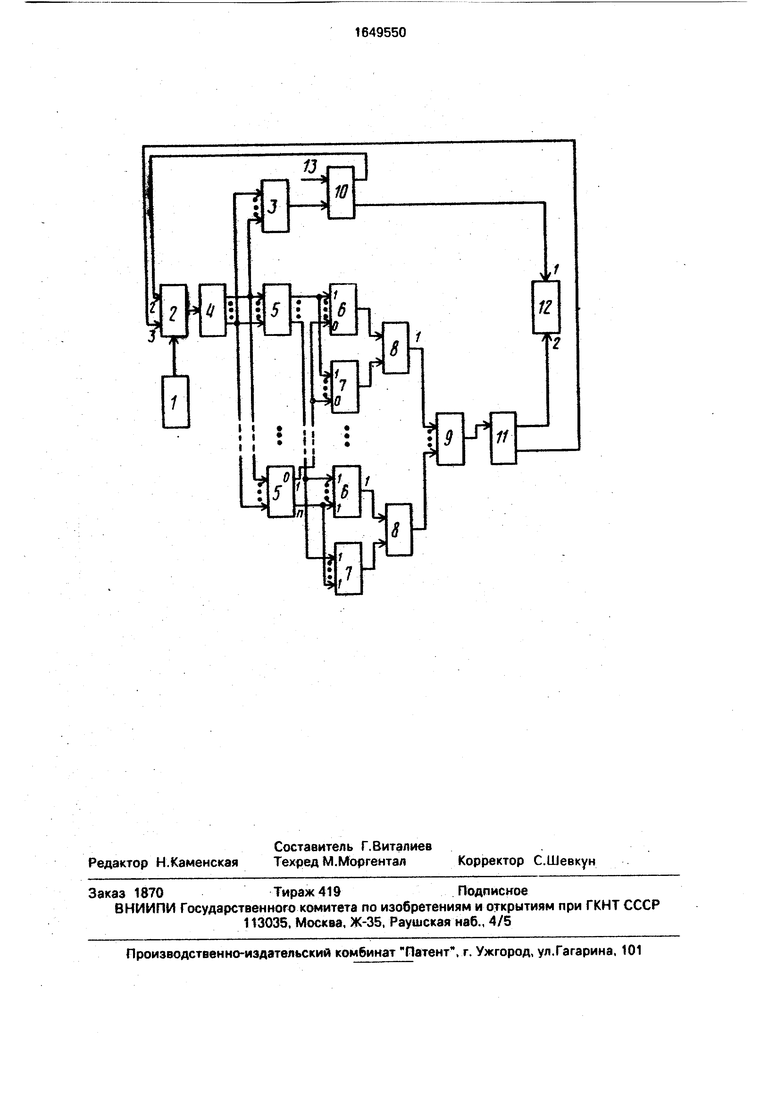

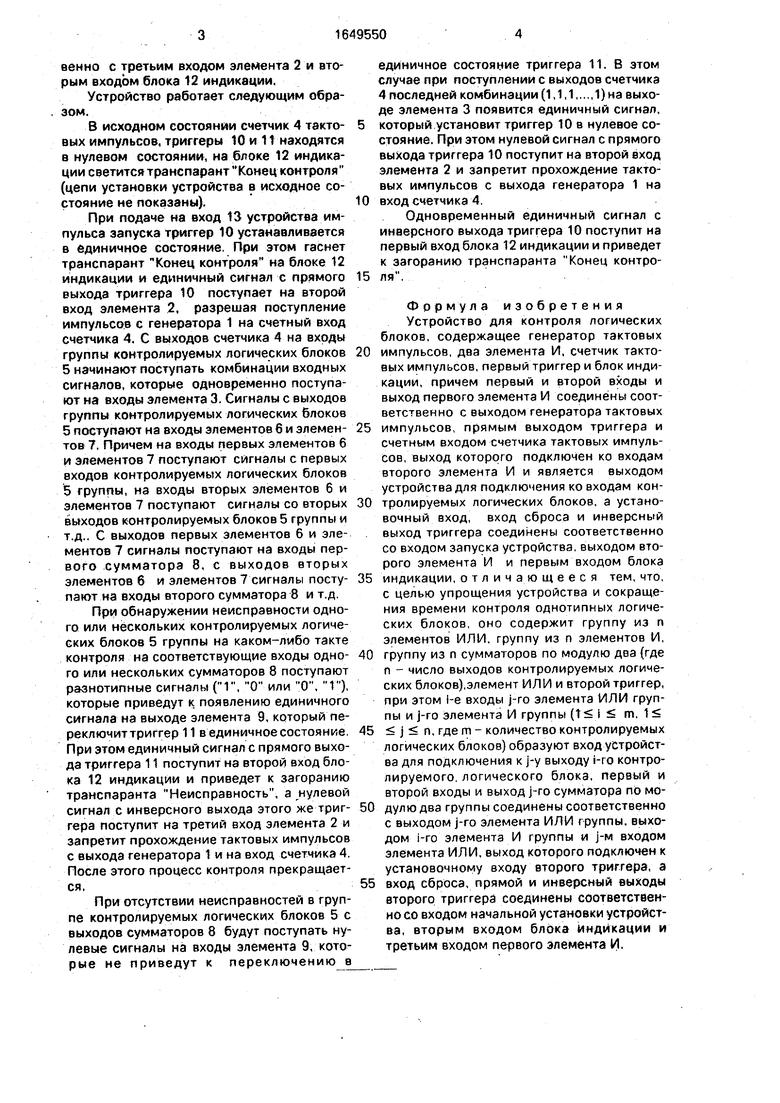

На чертеже показана структурная схема устройства для контроля логических блоков.

Устройство для контроля логических блоков содержит генератор 1 тактовых импульсов, первый и второй элементы И 2 и 3, счетчик 4 тактовых импульсов, группу контролируемых логических блоков 5, группу элементов ИЛИ 6, группу элементов И 7, группу сумматоров 8 по модулю два, элемент ИЛИ 9, первый и второй триггеры 10 и 11, блок 12 индикации и имеет вход 13 запуска устройства.

Выход генератора 1 тактовых импульсов соединен с первым входом элемента 2, выход которого соединен со счетным входом счетчика 4, выходы которого соединены

со входами группы контролируемых логических блоков 5 и входами элемента 3. Выход элемента 3 соединен со входом установки в нулевое состояние триггера 10, вход установки в единичное состояние которого является входом 13 запуска устройства, а инверсный и прямой выходы триггера 10 соединены соответственно с первым входом блока 12 индикации и вторым входом элемента 2. Первые выходы контролируемых логических блоков 5 группы соединены со входами первых элементов 6 группы и элементов группы, выходы которых соединены со входами первого сумматора 8 группы сумматоров по модулю два. Вторые выходы контролируемых логических блоков 5 группы соединены со входами второго сумматора 8 группы сумматоров по модулю два и т.д., а выходы сумматора 8 соединены со входами элемента 9, выход которого соединен со входом установки в единичное состояние триггера 11. Инверсный и прямой выходы триггера 11 соединены соотаетст(Л

С

о

о ел ел о

венно с третьим входом элемента 2 и вторым входом блока 12 индикации.

Устройство работает следующим образом.

В исходном состоянии счетчик 4 тактовых импульсов, триггеры 10 и 11 находятся в нулевом состоянии, на блоке 12 индикации светится транспарант Конец контроля (цепи установки устройства в исходное состояние не показаны).

При подаче на вход 13 устройства импульса запуска триггер 10 устанавливается в единичное состояние, При этом гаснет транспарант Конец контроля на блоке 12 индикации и единичный сигнал с прямого выхода триггера 10 поступает на второй вход элемента 2. разрешая поступление импульсов с генератора 1 на счетный вход счетчика 4. С выходов счетчика 4 на входы группы контролируемых логических блоков 5 начинают поступать комбинации входных сигналов, которые одновременно поступают на входы элемента 3. Сигналы с выходов группы контролируемых логических блоков 5 поступают на входы элементов б и элементов 7. Причем на входы первых элементов 6 и элементов 7 поступают сигналы с первых входов контролируемых логических блоков 5 группы, на входы вторых элементов 6 и элементов 7 поступают сигналы со вторых выходов контролируемых блоков 5 группы и т.д.. С выходов первых элементов 6 и элементов 7 сигналы поступают на входы первого сумматора 8, с выходов вторых элементов 6 и элементов 7 сигналы поступают на входы второго сумматора 8 и т.д.

При обнаружении неисправности одного или нескольких контролируемых логических блоков 5 группы на каком-либо такте контроля на соответствующие входы одного или нескольких сумматоров 8 поступают разнотипные сигналы (1, О или О, 1), которые приведут к появлению единичного сигнала на выходе элемента 9, который переключит триггер 11 в единичное состояние. При этом единичный сигнал с прямого выхода триггера 11 поступит на второй вход блока 12 индикации и приведет к загоранию транспаранта Неисправность, а нулевой сигнал с инверсного выхода этого же триггера поступит на третий вход элемента 2 и запретит прохождение тактовых импульсов с выхода генератора 1 и на вход счетчика 4. После этого процесс контроля прекращается.

При отсутствии неисправностей в группе контролируемых логических блоков 5 с выходов сумматоров 8 будут поступать нулевые сигналы на входы элемента 9, которые не приведут к переключению в

единичное состояние триггера 11. В этом случае при поступлении с выходов счетчика 4 последней комбинации (1,1,11) на выходе элемента 3 появится единичный сигнал,

который установит триггер 10 в нулевое состояние. При этом нулевой сигнал с прямого выхода триггера 10 поступит на второй вход элемента 2 и запретит прохождение тактовых импульсов с выхода генератора 1 на

вход счетчика 4.

Одновременный единичный сигнал с инверсного выхода триггера 10 поступит на первый вход блока 12 индикации и приведет к загоранию транспаранта Конец контроля.

Формула изобретения Устройство для контроля логических блоков, содержащее генератор тактовых

импульсов, два элемента И, счетчик тактовых импульсов, первый триггер и блок индикации, причем первый и второй входы и выход первого элемента И соединены соответственно с выходом генератора тактовых

импульсов, прямым выходом триггера и счетным входом счетчика тактовых импульсов, выход которого подключен ко входам второго элемента И и является выходом устройства для подключения ко входам контролируемых логических блоков, а установочный вход, вход сброса и инверсный выход триггера соединены соответственно со входом запуска устройства, выходом второго элемента И и первым входом блока

индикации, отличающееся тем, что, с целью упрощения устройства и сокращения времени контроля однотипных логических блоков, оно содержит группу из п элементов ИЛИ, группу из п элементов И,

группу из п сумматоров по модулю два (где п - число выходов контролируемых логических блоков),элемент ИЛИ и второй триггер, при этом 1-е входы j-ro элемента ИЛИ группы и j-ro элемента И группы (1 i m, 1

j п, где m - количество контролируемых логических блоков) образуют вход устройства для подключения к j-y выходу i-ro контролируемого, логического блока, первый и второй входы и выход j-го сумматора по модулю два группы соединены соответственно с выходом j-ro элемента ИЛИ группы, выходом i-ro элемента И группы и j-м входом элемента ИЛИ, выход которого подключен к установочному входу второго триггера, а

вход сброса, прямой и инверсный выходы второго триггера соединены соответственно со входом начальной установки устройства, вторым входом блока индикации и третьим входом первого элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических блоков | 1986 |

|

SU1336011A2 |

| Устройство для контроля логических блоков | 1984 |

|

SU1185342A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1238082A1 |

| Устройство для контроля логических блоков | 1987 |

|

SU1448346A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1288700A1 |

| Устройство для контроля дешифраторов | 1985 |

|

SU1298924A1 |

| Устройство для контроля лоических блоков | 1986 |

|

SU1453409A1 |

| Устройство для контроля экспоненциальных процессов | 1987 |

|

SU1500997A1 |

| Устройство для контроля микропроцессорных цифровых блоков | 1986 |

|

SU1383364A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1124312A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля логических блоков и схем, при приемосдаточных испытаниях. Целью изобретения является упрощение устройства и сокращение времени контроля однотипных логических блоков. С этой целью в устройство, содержащее генератор тактовых импульсов, два элемента И, счетчик тактовых импульсов, первый триггер и блок индикации, введены группа из п элементов ИЛИ, группа из п элементов И, группа сумматоров по модулю два, элемент ИЛИ и второй триггер. 1 ил.

| Устройство для контроля логическихСХЕМ | 1979 |

|

SU830392A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля логических блоков | 1981 |

|

SU1049913A1 |

Авторы

Даты

1991-05-15—Публикация

1988-02-10—Подача