Изобретение относится к телевизионной технике и может быть использовано в системах синхронизации строчной и кадровой разверток приемной телевизионной аппаратуры,

Цель изобретения - повышение помехозащищенности при одновременном уменьшении времени вхождения в синхронизм.

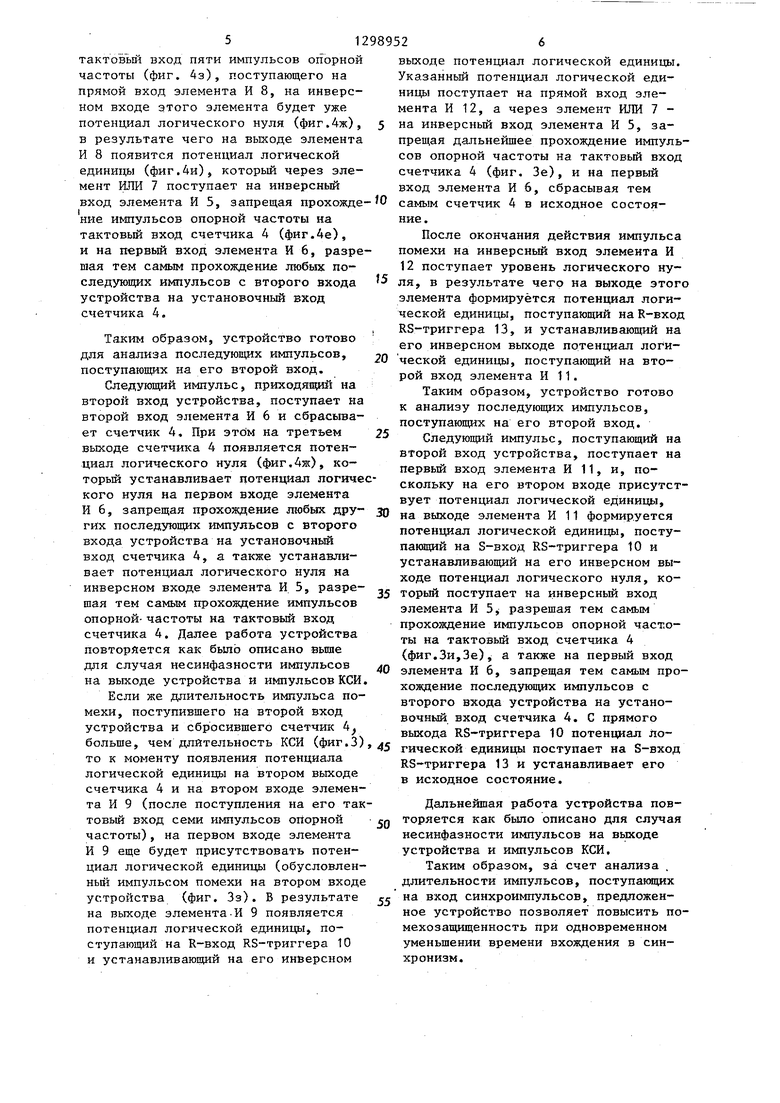

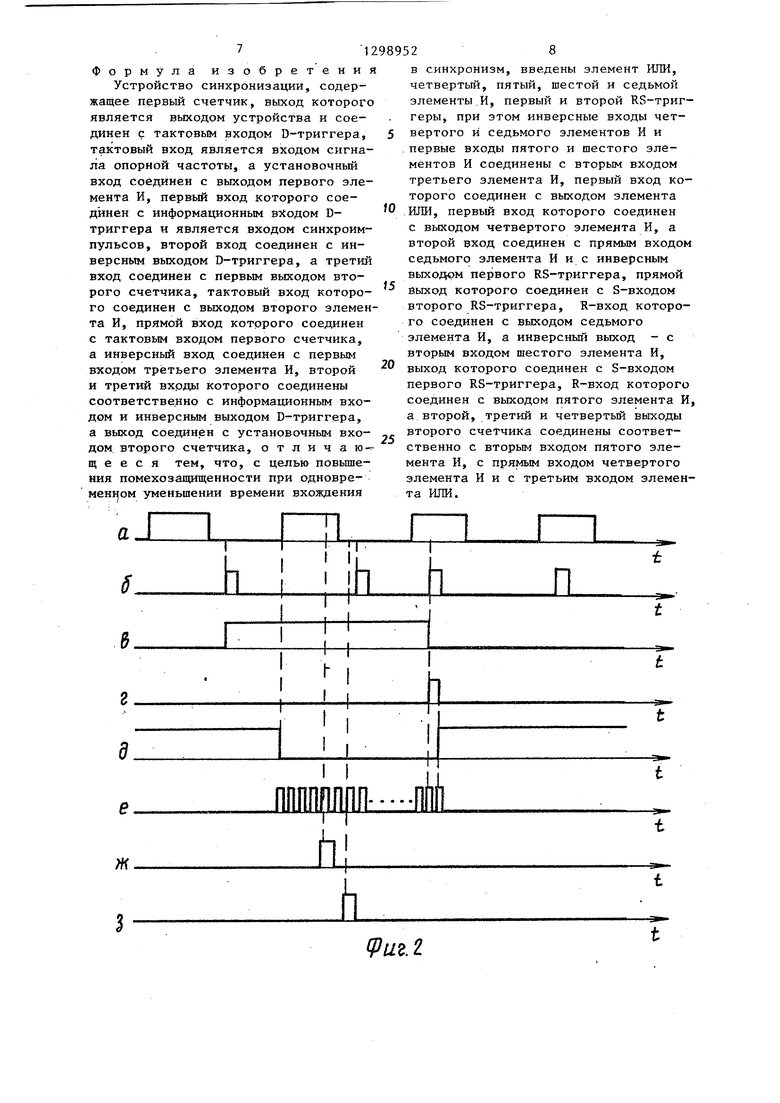

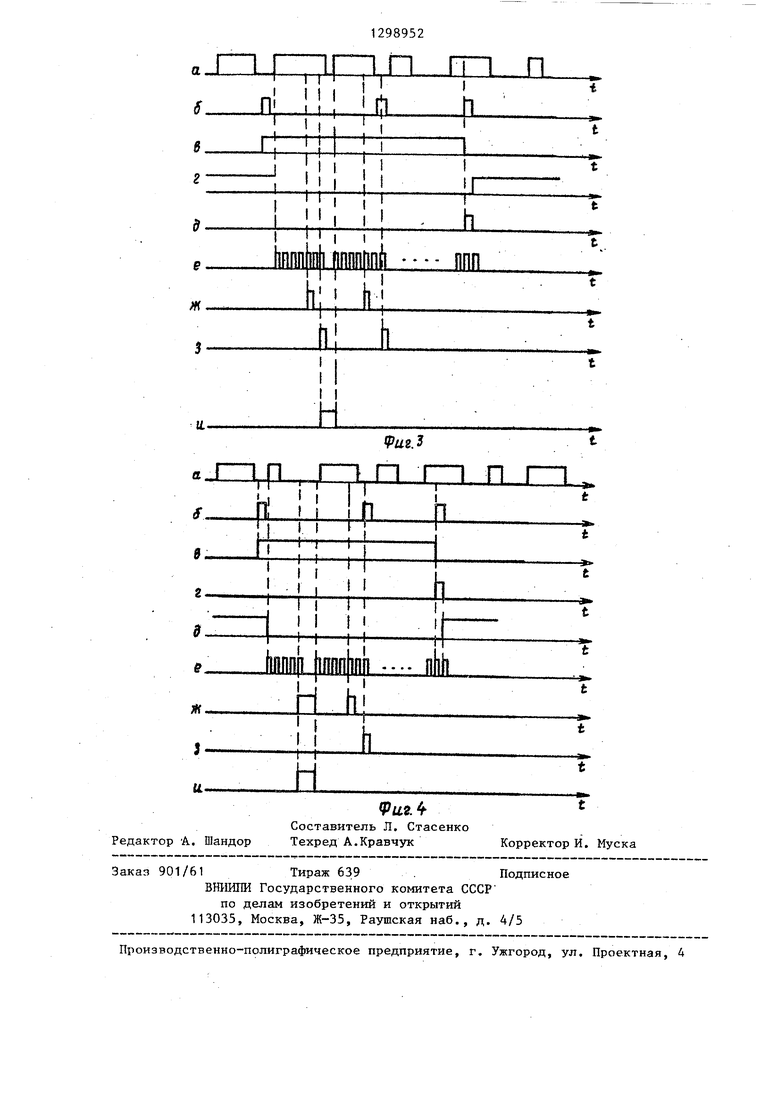

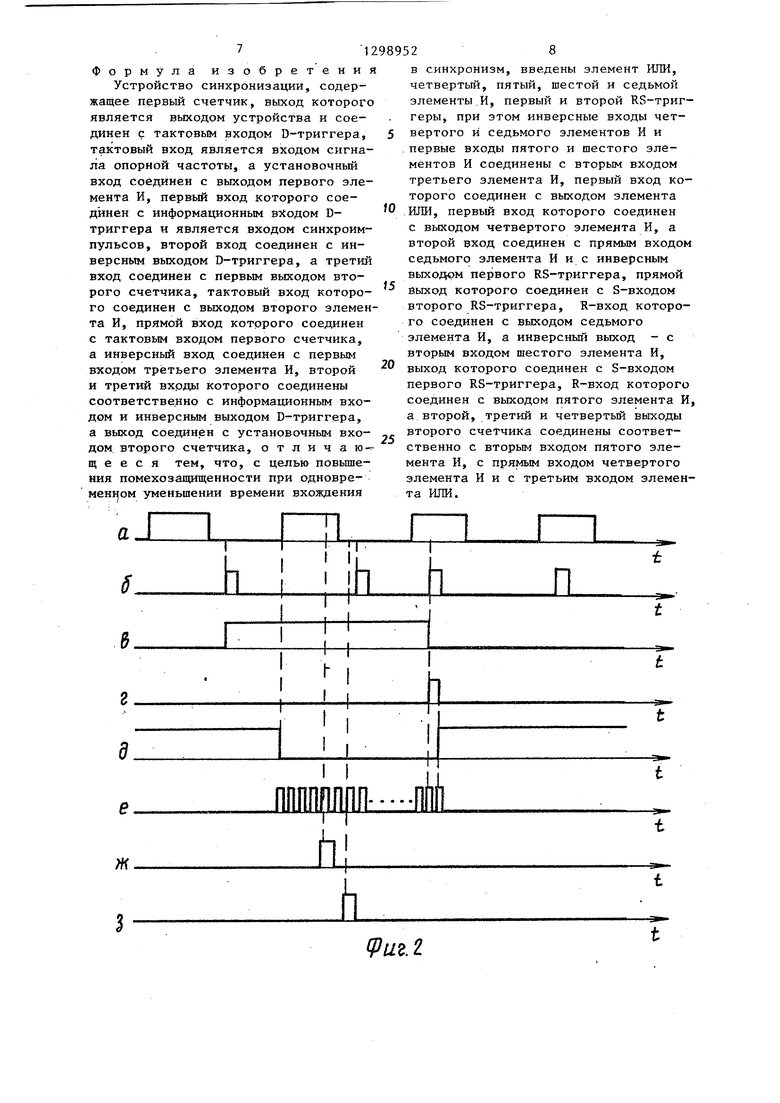

На фиг. 1 представлена структур- ная электрическая схема устройства синхронизации; на фиг. 2-4 - временные ди.аграммы, поясняющие работу устройства в различных режимах.

Устройство синхронизации содержит первый счетчик 1, первый элемент И 2 D-триггер 3, второй счетчик 4, второй 5 и третий 6 элементы И, элемент ИЛИ 7, четвертый 8 и пятый 9 элементы И, первый RS-триггер 10, шестой 11 и седьмой 12 элементы И, второй RS- триггер 13,

Устройство синхронизации работает следующим образом.

Предположим, что устройство работает в системе кадровой синхронизации телевизора. В этом случае на вход сигнала опорной частоты подаются импульсы удвоенной строчной частоты 2f , а на вход синхроимпульсов - кадровые синхроимпульсы (КСИ), вьще- ленные из полного телевизионного сигнала. Коэффициент счета первого счетчика 1 в этом случае равен .625, а на выходах второго счетчика 4 формируется уровень логической единицы при следующих состояниях:

на ijepBOM выходе.- после подсчета 627 импульсов;

на втором выходе - после 7 импульсов;

на третьем выходе - после 5 импулсов;

на четвертом выходе - после 628 импульсов.

На выходе первого счетчика 1 в результате деления опорной частоты при переходе счетчика 1 в исходное состояние вырабатьшаются импульсы с часто той следования полукадров, поступающие на выход устройства и на тактовы вход D-триггера 3, Если импульсы на выходе устройства синфазны с КСИ, подаваемыми на второй вход устройства, то на инверсном выходе D-триггера 3 присутствует уровень логического нуля, который поступает на второй вход элемента И 2 и запрещает прохождение

5

О

0

5

Q

.,

5

импульсов на установочный вход счетчика 1; тем самым исключается прохождение импульсов помехи на выход устройства.

Если импульсы на выходе устройства не синфазны с КСИ, или если произошло случайное пропадание КСИ (фиг. 2а,3а, 4а,2б,3б,4б), то на тактовый и информационный входы D-триггера 3 приходят импульсы, не совпадающие во времени, и на инверсном выходе D-триггера 3 формируется потенциал логической единицы (фиг. 2в,3в,4в). Этот сигнал поступает на второй вход элемента И 2 и на третий вход элемента И 6. При условии наличия синхронизма в предыдущий момент времени на первом и втором входах элемента ИЛИ 7 присутствует потенциал логического нуля,. а на четвертом выходе второго счетчика 4 - уровень логической единищ 1 (фиг. 2д,3д,4д)5 который поступает на третий вход элемента ИЛИ 7.

С приходом на второй вход устройства импульса КСИ (фиг.2) или импульса помехи (фиг. 3,4)и при наличии потенциала логической единицы на первом и третьем входах элемента И 6 происходит сброс второго счетчика 4, при этом на его четвертом выходе формируется потенциал логического нуля (фиг,2д,3д,4д), который устанавливает потенциал логического нуля на выходе элемента ШШ 7 и на инверсном входе элемента И 5, разрешая, прохождение импульсов опорной частоты с первого входа устройства на тактовый вход счетчика 4 (фиг.2е,3е,4е), а также запрещая прохождение любых последующих импульсов с второго входа устройства на установочный вход счетчика 4 через элемент И 6.

Если импульс, пришедший на второй вход устройства и сбросивший счетчик 4 в исходное состояние, является импульсом КСИ, то согласно ГОСТу его длительность равна 2,5 периодам строчной частоты или 5 периодам импульсов удвоенной строчной частоты.Поэтому, при поступлении на тактовый вход счетчика 4 пяти импульсов опорной частоты, на его третьем выходе появится потенциал логической еди- НИЦ61 (фиг.2ж,3ж,4ж), который поступает на прямой вход элемента И 8, на инверсном входе которого еще присутствует потенциал логической единищзЦ обусловленный КСИ на втором входе

устройства. В результате на выходе элемента И 8, соединенного с первым входом элемента ИЛИ 7, остается неизменным потенциал логического нуля, который не влияет на дальнейшую рабо- ту устройства.

При поступлении на тактовьй вход счетчика 4 семи импульсов опорной частоты на втором выходе счетчика 4 fg формируется потенциал логической единицы (фиг.2з), поступающий на второй вход элемента И 9, на первом входе которого к этому времени уже присутствует потенциал логического jf нуля, поскольку КСИ уже закончился. В результате на выходе элемента И 9 потенциал логического нуля остается неизменным и не влияет на дальнейшую работу устройства. Счетчик 4 продол- 20 жает подсчет импульсов опорной частоты. После поступления на его тактовый вход 627-го импульса опорной частоты на его первом выходе формируется импульс (фиг. 2г,3г,4г), посту25 ц, (фиг.3в,4в), обусловленный несин- пающий на третий вход элемента И 2

628-й импульс опорной частоты устана ливает уровень логической единигш на четвертом выходе счетчика 4 (фиг.2д) который через элемент ИШ 7 поступае на инверсный вход элемента И 5, тем самым запрещая дальнейшее прохождение импульсов опорной частоты на так товый вход счетчика 4 (фиг,2е).

Таким образом, устройство вошло в синхронизм, и дальнейшая работа его происходит аналогично описанной для случая синфазности импульсов на выхо де устройства и КСИ.

Работа устройства в случае, когда в период несинфазности импульсов на выходе устройства и импульсов КСИ на второй вход устройства приходит импульс помехи с длительностью, отличающейся от длительности КСИ, иллюст рируется временными диаграммами (фиг.З и 4).

В этом случае, как и в описанном, на инверсном выходе D-триггера 3 при сутствует потенциал логической едини-

фазностью импульсов на выходе устройства и КСИ. Этот уровень поступает на третий вход элемента И 6 и на второй вход элемента И 2, а на четвертом выходе счетчика 4 присутствует потенциал логической единицы (фиг.3д,4д), -обусловленный наличием синхронизма в предыдущий момент времени, который поступает через элемент ИЛИ 7 на пер- 35 вый вход элемента И 6.

и дакиций разрешение на прохождение с второго входа устройства на установочный вход счетчика 1 лишь того и fflyльca, который пришел в момент времени, отстоящий от импульса КСИ на время, равное периоду полукадра с увеличением его на длительность одной строки, что обеспечивает проверку на периодичность импульса КСИ, а также проверку его наличия в момент времени, отстающий от переднего фронта на длительность, равную одной строке, что обеспечивает неизменной фазу импульсов на выходе уст- ройства при последующем случайном отставании КСИ на длительность полутора строк либо опережении на длителность одной строки относительно их среднестатистического положения.По- ступивший в момент разрешения прохождения на установочный вход счетчика 1 КСИ импульс сбрасывает его, тем самым устанавливая новое значение фазы импульсов на выходе устройства (фиг.26). Первый же импульс, появившийся на выходе устройства в момент сброса счетчика 1, устанавливает уровень логического нуля на инверсном

выходе D-триггера 3 (фиг. 2в), запре-55 ства. и сбросившего счетчик 4, меньщающий прохождение любых импульсов на установочные входы первого 1 и второго 4 счетчиков. Поступивший на тактовьш вход ВТОРОГО счетчика. 4.

ц, (фиг.3в,4в), обусловленный несин-

628-й импульс опорной частоты устаналивает уровень логической единигш на четвертом выходе счетчика 4 (фиг.2д) который через элемент ИШ 7 поступае на инверсный вход элемента И 5, тем самым запрещая дальнейшее прохождение импульсов опорной частоты на так товый вход счетчика 4 (фиг,2е).

Таким образом, устройство вошло в синхронизм, и дальнейшая работа его происходит аналогично описанной для случая синфазности импульсов на выходе устройства и КСИ.

Работа устройства в случае, когда в период несинфазности импульсов на выходе устройства и импульсов КСИ на второй вход устройства приходит импульс помехи с длительностью, отличающейся от длительности КСИ, иллюстрируется временными диаграммами (фиг.З и 4).

В этом случае, как и в описанном, на инверсном выходе D-триггера 3 присутствует потенциал логической едини-

ц, (фиг.3в,4в), обусловленный несин-

фазностью импульсов на выходе устройства и КСИ. Этот уровень поступает на третий вход элемента И 6 и на второй вход элемента И 2, а на четвертом выходе счетчика 4 присутствует потенциал логической единицы (фиг.3д,4д), обусловленный наличием синхронизма в предыдущий момент времени, который поступает через элемент ИЛИ 7 на пер- вый вход элемента И 6.

Импульс помехи, приходящий на второй вход устройства, поступает на второй вход элемента И 6, и при наличии потенциала логической единицы на первом и третьем входах этого элемента сбрасывает счетчик 4, в результате чего на его четвертом выходе (фиг.3д,4д), на выходе элемента ИЛИ 7 и на инверсном входе элемента И 5 появляется потенциал логического нуля запрещающий прохождение любых последующих импульсов с второго входа устройства на установочный вход счетчика 4, а также разрешающий прохождение импульсов опорной частоты на тактовый вход счетчика 4 (фиг.3е,4е). Если длительность импульса помехи, поступившего на второй вход устройше, чем длительность КСИ, то к моменту появления потенциала логической единицы на третьем выходе счетчика 4 (после поступления на его

тактовьш вход пяти импульсов опорной частоты (фиг. 4з), поступающего на прямой вход элемента И 8, на инверсном входе этого элемента будет уже потенциал логического нуля (фиг.4ж), в результате чего на выходе элемента И 8 появится потенциал логической единицы (фиг.4и), который через элемент ШШ 7 поступает на инверсный вход элемента И 5, запрещая прохожде ние импульсов опорной частоты на тактовый вход счетчика 4 (фиг.4е), и на первый вход элемента И 6, разрешая тем самым прохождение любых по- следуюпщх импульсов с второго входа устройства на установочный вход счетчика 4,

Таким образом, устройство готово для анализа последующих импульсов, поступающих на его второй вход.

Следующий импульс, приходящий на второй вход устройства, поступает на второй вход элемента И 6 и сбрасывает счетчик 4, При этим на третьем выходе счетчика 4 появляется потенциал логического нуля (фиг.4ж), который устанавливает потенциал логичекого нуля на первом входе элемента И 6, запрещая прохождение любых дру- гих последующих импульсов с второго входа устройства на установочный вход счетчика 4, а также устанавливает потенциал логического нуля на инверсном входе элемента И 5, разре- шая тем самым прохождение импульсов опорной- частоты на тактовый вход счетчика 4. Далее работа устройства повторяется как было описано выше для случая несинфазности импульсов на выходе устройства и импульсов КСИ

Если же длительность импульса помехи, поступившего на второй вход устройства и сбросившего счетчик 4 больше, чем длительность КСИ (фиг.З) то к моменту появления потенциала логической единицы на втором выходе счетчика 4 и на втором входе элемента И 9 (после поступления на его тактовый вход семи импульсов ойорной частоты), на первом входе элемента И 9 еще будет присутствовать потенциал логической единицы (обусловленный импульсом помехи на втором входе устройства (фиг. Зз). В результате на выходе элемента-И 9 появляется потенциал логической единицы, поступающий на R-вход RS-триггера 10 и устанавливающий на его инверсном

выходе потенциал логической единицы. Указанный потенциал логической единицы поступает на прямой вход элемента И 12, а через элемент ИЛИ 7 - на инверсный вход элемента И 5, запрещая дальнейшее прохождение импульсов опорной частоты на тактовый вход счетчика 4 (фиг. Зе), и на первый вход элемента И 6, сбрасывая тем самым счетчик 4 в исходное состояние .

После окончания действия импульса помехи на инверсный вход элемента И 12 поступает уровень логического нуля, в результате чего на выходе этог элемента формируется потенциал логической единицы, поступающий на R-вход RS-триггера 13, и устанавливающий на его инверсном выходе потенциал лоГи- ческой единицы, поступающий на второй вход элемента И 11.

Таким образом, устройство готово к анализу последующих импульсов, поступающих на его второй вход.

Следующий импульс, поступающий на второй вход устройства, поступает на первый вход элемента И 11, и, поскольку на его втором входе присутствует потенциал логической единицы, на выходе элемента И 11 формируется потенциал логической единицы, поступающий на S-вход RS-триггера 10 и устанавливающий на его инверсном выходе потенциал логического нуля, который поступает на инверсный вход элемента И 5 разрешая тем самым прохождение импульсов опорной частоты на тактовый вход счетчика 4 (фиг.3и,3е) а также на первый вход элемента И 6, запрещая тем самым прохождение последующих импульсов с второго входа устройства на установочный вход счетчика 4. С прямого выхода RS-триггера 10 потенциал логической единицы поступает на S-вход RS-триггера 13 и устанавливает его в исходное состояние.

Дальнейшая работа устройства повторяется как было описано для случая несинфазности импульсов на вькоде устройства и импульсов КСИ,

Таким образом, за счет анализа длительности импульсов, поступакицих на вход синхроимпульсов, предложенное устройство позволяет повысить помехозащищенность при одновременном уменьшении времени вхождения в синхронизм.

Формула изобретения

Устройство синхронизации, содержащее первый счетчик, выход которого является выходом устройства и соединен с тактовым входом D-триггера, тактовый вход является входом сигнала опорной частоты, а установочный вход соединен с выходом первого элемента И, первый вход которого соединен с информационным входом D- триггера и является входом синхроимпульсов, второй вход соединен с инверсным выходом D-триггера, а третий вход соединен с первым выходом второго счетчика, тактовый вход которого соединен с выходом второго элемента И, прямой вход которого соединен с тактовым входом первого счетчика, а инверсный вход соединен с первым входом третьего элемента И, второй и третий вхрды которого соединены соответственно с информационным входом и инверсным выходом D-триггера, а выход соединен с установочным входом второго счетчика, отличаю- щ е е с я тем, что, с целью повьппе- ния помехозащищенности при одновременном уменьшении времени вхождения

0

5

0

5

в синхронизм, введены элемент ИЛИ, четвертый, пятый, шестой и седьмой элементы.И, первый и второй К5-трИ1- геры, при этом инверсные входы четвертого и седьмого элементов И и .первые входы пятого и шестого элементов И соединены с вторьм входом третьего элемента И, первый вход которого соединен с выходом элемента ИЛИ, первый вход которого соединен с выходом четвертого элемента И, а второй вход соединен с прямым входом седьмого элемента И и с инверсным выходом первого RS-триггера, прямой выход которого соединен с S-входом второго RS-триггера, К-вход которого соединен с выходом седьмого элемента И, а инверсный выход - с вторым входом шестого элемента И, выход которого соединен с S-входом первого RS-триггера, R-вход которого соединен с выходом пятого элемента И, а второй, третий и четвертый выходы второго счетчика соединены соответственно с вторым входом пятого элемента И, с прямым входом четвертого элемента И и с третьим входом элемента ИЛИ.

f

тцпл

г

е

ж

I I

Н

Ряе.

р п п 1-1

I I II 11г

Z

S в

ж

г

и.

Редактор А. Шандор

(pfi.

Составитель Л. Стасенко Техред А.Кравчук

Заказ 901/61 Тираж 639 . Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Я

Ряе.

Корректор И. Муска

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство кадровой синхронизации | 1990 |

|

SU1737745A1 |

| Цифровой фазометр мгновенных значений | 1988 |

|

SU1553920A1 |

| Синтезатор частоты | 1984 |

|

SU1257845A1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО ИЗМЕРЕНИЯ ХАРАКТЕРИСТИК ДИСКРЕТНОГО КАНАЛА СВЯЗИ | 1995 |

|

RU2138910C1 |

| Устройство измерения времени ограничения тока транзисторными коммутаторами систем зажигания | 1989 |

|

SU1758279A1 |

| Устройство формирования опорного сигнала системы движения для мессбауэровского спектрометра | 1988 |

|

SU1672326A1 |

| Устройство синхронизации М-последовательности по задержке | 1986 |

|

SU1398106A1 |

| Устройство для измерения фазового дрожания | 1987 |

|

SU1469556A1 |

| Устройство для индикации синхронизма | 1980 |

|

SU944131A1 |

| УСТРОЙСТВО ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЫ | 1991 |

|

RU2014740C1 |

Изобретение относится к телевизионной технике. Цель изобретения - повьшение помехозащищенности при одновременном уменьшении времени вхождения в синхронизм. Устр-во содержит два счетчика 1 и 4, семь эл-тов И 2, 5, 6, 8, 9, 11 и 12, D-триггер 3, зл-т ИЛИ 7 и два RS-триггера 10 и 13. Цель достигается введением зл-та ИЛИ 7, эл-тов И 8, 9, 11 и 12 и RS-триг- геров 10 и 13 с помощью которых осуществляется анализ длительности синхроимпульсов, поступающих на вход устр-ва. 4 ил. Bo/jfffd сл o со ОО ю СП ю

| Патент Великобритании №1559559, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство синхронизации | 1983 |

|

SU1164909A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-03-23—Публикация

1985-08-06—Подача